摘要

在集成電路的制造階段延續摩爾定律變得越發困難,而在封裝階段利用三維空間可以視作 對摩爾定律的拓展。硅通孔是利用三維空間實現先進封裝的常用技術手段,現有技術中對于應用于CMOS圖像傳感器件封裝的圓臺硅通孔,采用的是在頂部不斷橫向刻蝕的方式實現的,不利于封裝 密度的提高,且對于光刻設備的分辨率有一定的要求。針對現有技術中的問題,一種嚴格控制橫向 刻蝕尺寸(僅占原始特征尺寸的3%~12%)的圓臺硅通孔刻蝕方法被研究探索出來。該方法通過調節 下電極功率(≤30 W),獲得了側壁角度可調(70°~88°)、通孔底部開口尺寸小于光刻定義特征尺寸 的圓臺硅通孔結構。這一方法有望向三維集成電路領域推廣,有助于在封裝階段延續摩爾定律。

引言

依循摩爾定律,芯片的特征尺寸越來越小,以滿 足器件集成度的增長。但是,當芯片的特征尺寸小到 一定程度會出現量子效應等現象,從而改變芯片目前 所遵循的物理規律。因此,長期來看,單純采用越來越 先進的工藝技術來延續摩爾定律是不可持續的。值得 注意的是,先進工藝技術節點對特征尺寸的微縮主要 還是一種針對平面區域的概念。目前最先進的環柵技 術盡管可以實現晶體管立體/三維方向的堆疊,但還 沒有確切的量產記錄(韓國三星公司聲稱已可以實現 量產)。加入封裝交流群,加VX:tuoke08。相比于在芯片制造過程中利用三維空間,在芯 片封裝過程中利用三維空間的難度更低。能夠利用三 維空間的區域將增加芯片的集成度,實際上就可以視 作對摩爾定律的拓展。利用三維空間進行堆疊封裝, 可以實現高性能的異質集成,這樣的系統級封裝具有 更高的容量、更好的性能和更高的良率。

硅通孔(TSV)技術是先進封裝中的常用技術之 一,采用硅通孔技術實現三維空間中芯片或者線路 的垂直互連具有降低寄生效應、提高運行速率和降低 器件功耗等優點。硅通孔技術在先進封裝中的應用 可以分成以下幾類:(1)在三維空間中實現芯片的垂直 堆疊互連,這類通孔被稱作3D硅通孔(硅通孔是在芯 片所在的硅片上開通的,封裝與芯片制造的界限模糊 化,因此也被稱作3D IC);(2)采用硅轉接板將不同芯 片的通信距離拉近,硅轉接板上的這類通孔被稱作2.5D硅通孔;(3)采用圓臺硅通孔技術,從而利用三維 空間對圖像傳感器件進行封裝。

同時,硅通孔技術也面臨一些挑戰。盡管采用硅 通孔的三維封裝電學性能優良,但其工藝流程相對復 雜,在生產成本上不如采用重新布線技術來實現三維 封裝。具體到硅通孔技術的工藝流程,其最主要的步 驟是硅通孔刻蝕和鈍化層、阻擋層金屬填充。在進行 硅通孔刻蝕時,通常采用Bosch工藝,但這種工藝形成 的硅通孔角度一般比較垂直,不利于后續的鈍化層、 阻擋層金屬填充。例如,在3D系統級封裝的硅通孔中 深寬比比較大,一般需要原子層沉積等技術來實現孔 的填充,導致產能降低。另外,雖然采用直孔替代斜孔 可以提高封裝的密度和可靠性,但是采用直孔無法掛 膠(即無法通過旋涂實現孔側壁鈍化膠的涂布),需要 改用等離子體增強化學氣相沉積(PECVD)工藝生長 絕緣層、物理氣相沉積(PVD)工藝生長種子層和電鍍, 而每增加一步工藝過程都會增加產品的制造成本,過 長的工藝路線會使產品失去商業競爭力。因此,對于 應用于圖像傳感器件的封裝,其通孔一般采用圓臺結構,可以通過旋涂實現孔側壁鈍化膠的涂布,降低成 本。現有的技術主要利用硅的側向刻蝕獲得這類圓臺結構,即現有技術對通孔側壁角度的工藝量化控制 是通過調節上開口的尺寸實現的。因此,現有技術中 的圓臺通孔的下開口尺寸與光刻膠定義的尺寸相同, 而上開口的尺寸則大于光刻膠定義的尺寸。這就對光 刻分辨率提出了更高的要求,即在圓臺通孔的上開口 尺寸一定的情況下,需要利用***定義出更小的圖 形。與光刻定義線條狀圖形不同,定義孔狀圖形對光 刻分辨率的要求更高,當孔的尺寸小到一定程度后, 定義的圖案會出現不圓等異常。并且,硅的側向刻蝕 容易導致開口尺寸的均勻性難以控制,甚至相鄰2個 孔之間會發生穿通,使得2個孔之間需要預留安全距 離,限制了封裝密度的提高。針對上述問題,本文提出 了一種應用于圖像傳感器件封裝的圓臺硅通孔的刻 蝕方法,可以保證其上開口與光刻定義的尺寸近乎一 致(偏差僅為3%~12%),從而降低工藝整合時對光刻 工藝的要求,并且可以避免硅側向刻蝕所導致的封裝 密度下降的問題。

2 試驗部分

2.1試驗儀器與材料

本研究使用的試驗儀器包括:上海微電子公司生 產的SMEE SSB500步進式***,北方華創公司生 產的HSE P230等離子體刻蝕機,日立公司生產的SU8010冷場發射掃描電子顯微鏡。本研究使用的試驗材料包括:12英寸硅晶圓,電子 級O2、He、SF6、C4F8、Ar,德國All Resist公司生產的光刻 膠和顯影液,北京化工廠生產的H2SO4(濃)和H2O2。

2.2試驗方法

本研究使用的12英寸硅晶圓,其(100)晶面垂直 于晶圓平面朝上。試驗采用Piranha溶液H2SO4(濃)和H2O2以7:3的配比組成]清洗后,在晶圓上旋涂光刻 膠。然后,試驗使用步進式***進行光刻,并通過顯 影定義出待刻蝕的圖形。最后,試驗使用等離子體刻 蝕機進行刻蝕,刻蝕后的剖面結構使用冷場發射掃描 電子顯微鏡進行表征。

其中,等離子體刻蝕是關鍵的試驗步驟,等離子 體刻蝕的基準工藝配方如表1所示。

其中,氣壓用于達到等離子體產生的條件,應用 于刻蝕機的等離子體屬于低溫等離子體,需要一定的 真空才能產生,而電感耦合等離子體形成所需要的真 空一般在26.66 Pa以下;上電極功率產生等離子體;下 電極射頻功率牽引腔室中的等離子體向下運動作用 于晶圓;SF6用于產生氟基自由基刻蝕硅片;O2用于形 成硅氧復合物保護孔道結構的側壁,從而實現各向異 性刻蝕;工藝時間與所需要的刻蝕深度相關。

2.3試驗結果

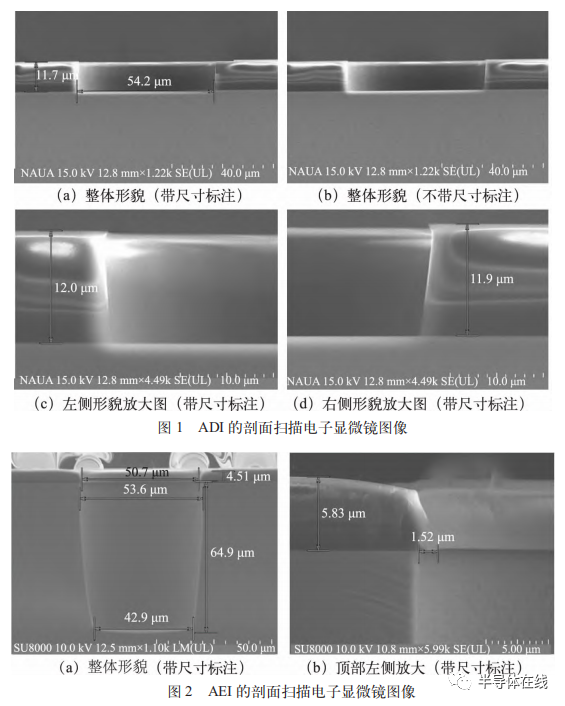

圖1為光刻膠顯影后(即等離子體刻蝕之前)檢測 (ADI)的剖面掃描電子顯微鏡圖像,光刻所定義出的 特征尺寸約為50μm。

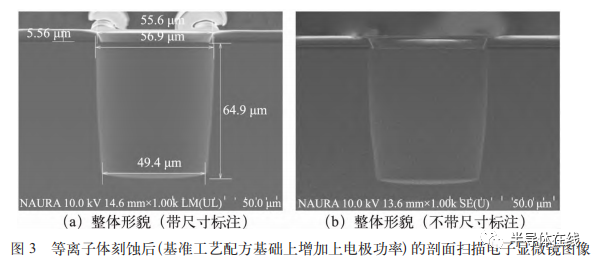

圖2為等離子體刻蝕后檢測(AEI)的剖面掃描電 子顯微鏡圖像。

從圖2(a)可以看出,其硅通孔的上開口尺寸(大 約為54μm)與光刻定義的特征尺寸(大約為50μm) 相差無幾,下開口尺寸(大約為43μm)則顯著小于光 刻定義的特征尺寸,再結合約65μm的刻蝕深度值, 可得出其側壁的平均角度大約為85°,有利于后續的 填充工藝;而從圖2(b)的放大圖可以更加清晰地看 出,硅通孔的頂部沒有出現明顯的在光刻膠底部向硅 通孔內側的刻蝕現象,即沒有明顯的下切現象出現。進一步的研究還發現,當光刻定義出的圖案的特征尺 寸減小時,采用上述等離子體刻蝕技術所刻蝕出的圖 形的下切尺寸的絕對值也會隨之減小,而下切尺寸占 光刻定義尺寸的比值雖有上升,但有逐步趨于飽和的 趨勢,預示其有望向尺寸更小的三維封裝方向發展, 但相應地也存在一定的挑戰。

3 分析與討論

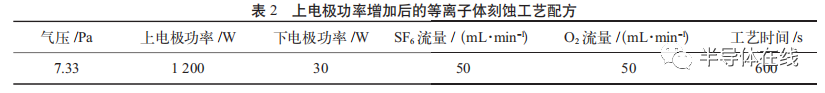

對形成上述形貌的影響因素進行探討。首先,調 整工藝配方中的上電極功率,若上電極功率增加,對 形貌的影響不大(上開口尺寸約為57μm,下開口尺寸 約為49μm,刻蝕深度約為65μm,下切現象加重,但 側壁的平均角度保持為約85°不變),圖3為等離子體 刻蝕后的剖面掃描電子顯微鏡圖像。上電極功率增加 后的等離子體刻蝕工藝配方如表2所示。

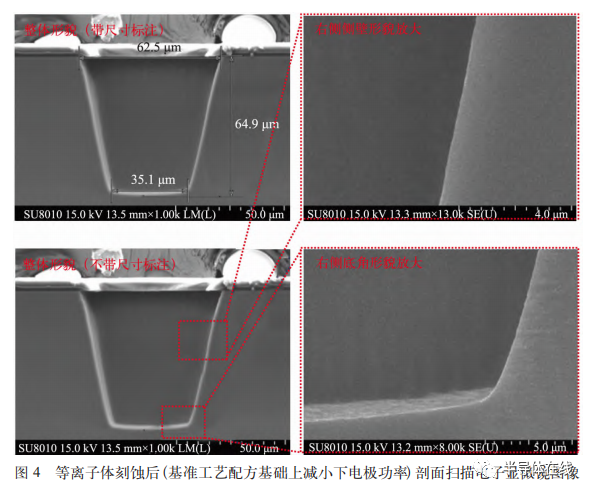

試驗結果證明,上電極功率并不是形成該形貌的 主要影響因素。通過進一步的探索發現,若減小下電 極功率,則可以獲得側壁角度更加傾斜的硅通孔(上 開口尺寸約為62μm,下開口尺寸約為35μm,刻蝕深 度約為65μm,側壁平均角度約為76°),圖4為其等 離子體刻蝕后的剖面掃描電子顯微鏡圖像。

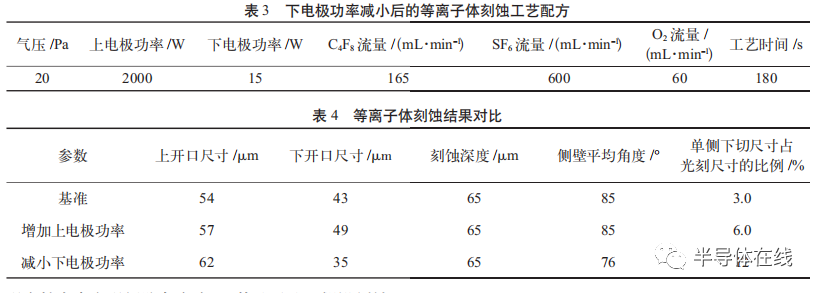

從圖4可以看出,相比于高深寬比的Bosch工藝, 該等離子體刻蝕技術在側壁粗糙度方面具有優勢,有 利于后續工藝以及保證器件的電學性能。下電極功率 減小后的等離子體刻蝕工藝配方如表3所示。

對試驗的結果進行分析,增加上電極功率會加大 下切現象(通過單側下切尺寸占光刻定義出的原始特 征尺寸的比例來定量描述該現象),但不會明顯影響 側壁的平均角度,而減小下電極功率則可以明顯減小 側壁的平均角度,等離子體刻蝕結果對比如表4所示。

從唯象的角度,對減小下電極射頻功率可以獲得 圓臺型微孔結構進行分析討論:對于電感耦合等離子 體刻蝕機而言,其上電極射頻功率用于產生等離子 體,下電極射頻功率用于牽引腔室中的等離子體向下 運動并作用于晶圓。等離子體的平均自由程有限,在 孔道結構中運動時更容易發生湮滅,當下電極功率不 足時,會使得到達孔道結構底部的等離子體明顯少于 頂部,進而獲得上大下小的圓臺型微孔結構。

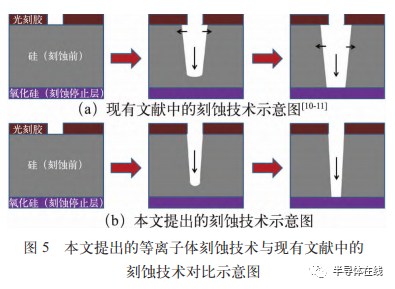

現有文獻中,硅通孔的下開口尺寸與光刻膠定義 的特征尺寸保持一致,傾斜側壁是通過較大的下切現 象獲得的,圖5(a)為現有文獻中的刻蝕技術示意圖。而本文提出的刻蝕方法,是硅通孔的上開口尺寸與光 刻膠定義的特征尺寸保持一致,通過對側壁的保護作 用使得下開口明顯小于光刻膠定義的特征尺寸而獲 得傾斜側壁。圖5為本文提出的等離子體刻蝕技術與 現有文獻中的刻蝕技術對比示意圖,當光刻膠定義的 特征尺寸一定的情況下,通過本文提出的刻蝕方法能 得到尺寸更小的硅通孔結構,從而使得硅通孔技術對 于光刻分辨率的要求降低。從定量的角度分析,采用現有技術來實現側壁角度為76°的硅通孔,假設刻蝕 深度為65μm、光刻定義的特征尺寸為50μm,通過一 個簡單的三角函數運算可以得到現有技術的上開口 需要達到82μm(現有技術的下開口尺寸與光刻定義 的特征尺寸50μm保持一致),比原始的特征尺寸50μm多出32μm,比本文報道的上開口尺寸還要多 出20μm,單側的下切值占特征尺寸的比例達到32%, 遠大于3%~12%的比例,不利于封裝密度的提高。

另外,不同于集成電路制造領域(特別是制約先 進制程發展的特征尺寸領域)的光刻定義的圖案(主 要是線條狀的圖案),先進封裝領域的光刻圖案主要 是圓孔狀的圖案,在相同特征尺寸下的圓形圖案比線 條狀圖案對光刻分辨率的要求更高。

對硅通孔的側壁角度進行進一步的分析:一方 面,硅通孔刻蝕后的工藝是鈍化膠的涂布工藝或者通孔的填充工藝,所以通孔刻蝕的側壁不能太直,否則 不利于后續的鈍化膠涂布(無法掛膠)或者填孔工藝 (封口效應);另一方面,通孔刻蝕的側壁又不能太斜, 太斜的話會降低晶圓利用率,并且在回刻步驟中容易 破壞側壁的絕緣層。因此,這類圓臺硅通孔的側壁傾 斜角度在70°~88°最適宜。研究結果證明,通過調節下 電極功率可以實現圓臺硅通孔側壁傾斜角度的調節。

本技術所能實現的硅通孔深寬比還有待提升,目 前并不適合集成電路的高密度互連,更加適合分立器 件的先進封裝,例如微機電系統器件(如低阻硅柱的 三維互連等)以及圖像傳感器件等的三維封裝。此 類器件的共同特征是所需的互連接口數量較少,而器 件尺寸又相對比較大。另外,采用本技術形成的硅通 孔側壁粗糙度具有優勢,有利于減少光學傳輸損耗, 還可以應用于半導體照明等領域。

4 結論

本文提出了一種圓臺硅通孔的刻蝕方法,可以在 先進封裝(特別是針對圖像傳感器件的封裝)中引入 側壁平均角度在70°~88°的硅通孔互連結構。通過施 加30 W及以下的下電極功率實現圓臺硅通孔的刻 蝕,該圓臺硅通孔的下開口尺寸顯著小于光刻定義的 特征尺寸。與現有文獻中的刻蝕技術不同,該刻蝕技 術可以降低工藝整合時對光刻分辨率的要求,且有利 于提高封裝密度。該刻蝕技術對于高深寬比的刻蝕還 具有一定的局限性,對于如何將該技術擴展到三維封 裝硅通孔刻蝕還需要進一步的研究和探索。

審核編輯:湯梓紅

-

傳感器

+關注

關注

2564文章

52724瀏覽量

764726 -

芯片

+關注

關注

459文章

52308瀏覽量

437816 -

集成電路

+關注

關注

5420文章

11991瀏覽量

367570 -

封裝

+關注

關注

128文章

8598瀏覽量

144992 -

刻蝕

+關注

關注

2文章

203瀏覽量

13349 -

先進封裝

+關注

關注

2文章

465瀏覽量

549

原文標題:【半導光電】一種用于先進封裝的圓臺硅通孔的刻蝕方法

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【轉帖】干法刻蝕的優點和過程

中微推出用于3D芯片及封裝的硅通孔刻蝕設備Primo TSV200E(TM)

詳解TSV(硅通孔技術)封裝技術

晶體硅太陽能電池刻蝕的作用及方法與刻蝕的工藝流程等介紹

實現高精度深硅刻蝕的方法

技術資訊 I 3D-IC 中 硅通孔TSV 的設計與制造

一種用于先進封裝的圓臺硅通孔的刻蝕方法

一種用于先進封裝的圓臺硅通孔的刻蝕方法

評論