16阻抗補償技術

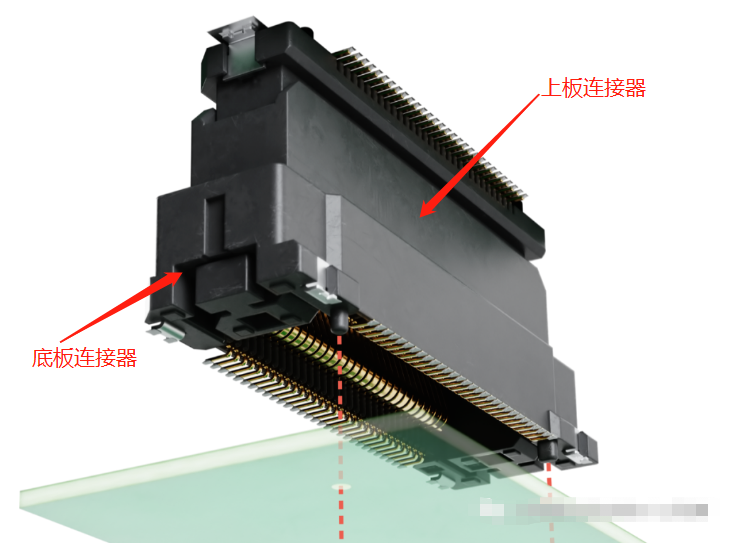

針對傳輸線上寄生電容和寄生電感帶來的反射噪聲,在現實PCB設計中是無法避免的。例如2個PCB板通過B2B連接器結合時,B2B連接器的寄生電感。下圖是一對B2B連接器,可以將兩塊PCB連接起來。

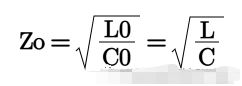

使用補償設計可以抵消一部分反射噪聲。此種補償設計的出發點就是盡量讓信號,在傳輸線上傳輸的過程中,不要感受到很大的感性突變,即信號遇到的傳輸線阻抗始終是一致的。在之前的文章《信號完整性之傳輸線--四》的文章中提到,理想傳輸線的一階模型

Z0是傳輸線特征阻抗(單位Ω);L0是單位長度電感(單位nH/in);C0是單位長度電容(單位nF/in);L是整段傳輸線總電感(單位nH);C是整段傳輸線總電容(單位nF)。

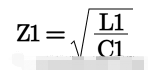

在感性阻抗突變L1的附近添加補充電容C1,可以將感性突變補償成一段阻抗可控的傳輸線。

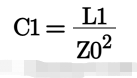

為了將反射信號噪聲降低到最小,需要找到一個合適的電容值。使感性阻抗突變這一段傳輸線的阻抗等于傳輸線目標,即Z0=Z1。由此得知:

例如某連接器的寄生電感為10nH,傳輸線阻抗是50R,則總的補充電容為

C1=10/50*50=4pF。連接器左右兩邊各1個2pf的電容是比較推薦的補償方式。

上述的這種方法,根據信號上升時間不同,對反射噪聲的補充不同。有時可以降低75%的反射噪聲。除了連接器,此方法也可用在其他有感性突變的電路中,例如過孔、電阻等。

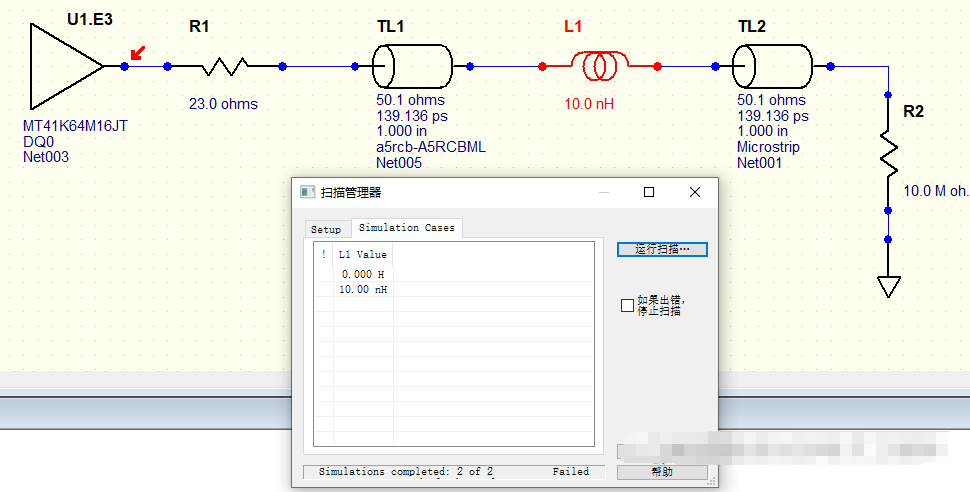

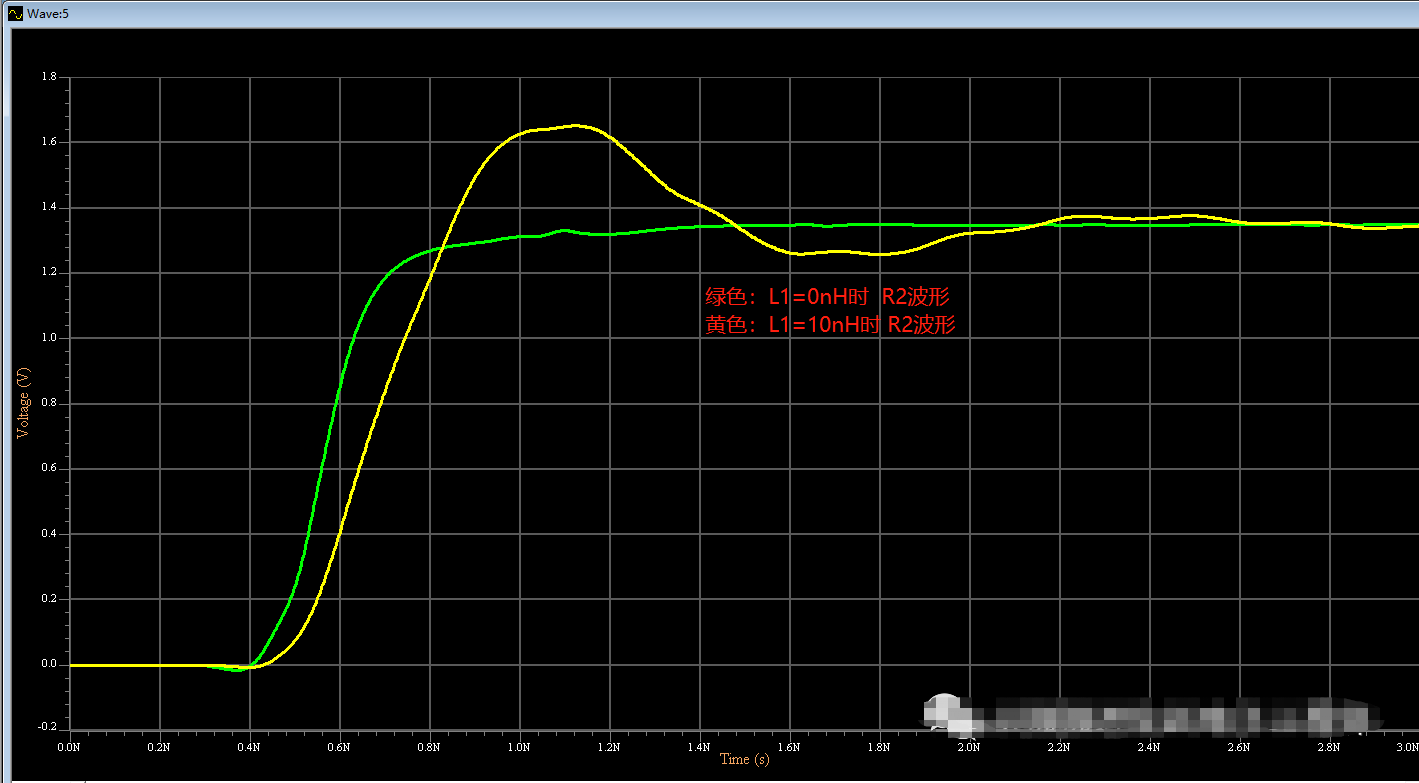

如下是仿真數據。首先是L1=0nH和L1=10nH的波形

看仿真結果,傳輸線上沒有寄生電感時,波形沒有反射(綠色波形)。當有一個10nH的寄生電感存在時,波形明顯反射(黃色過沖)。

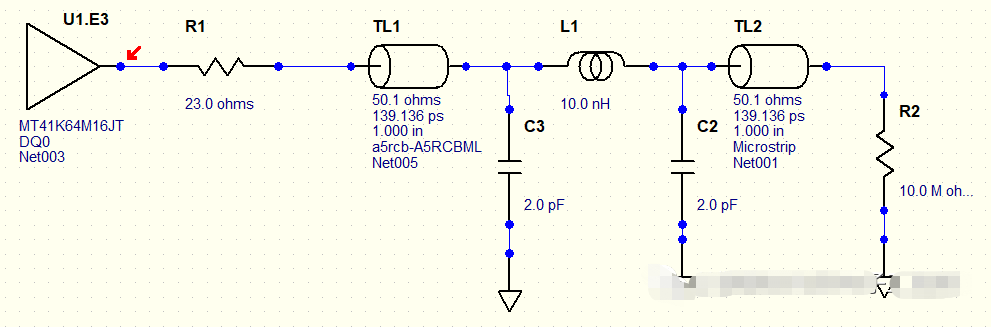

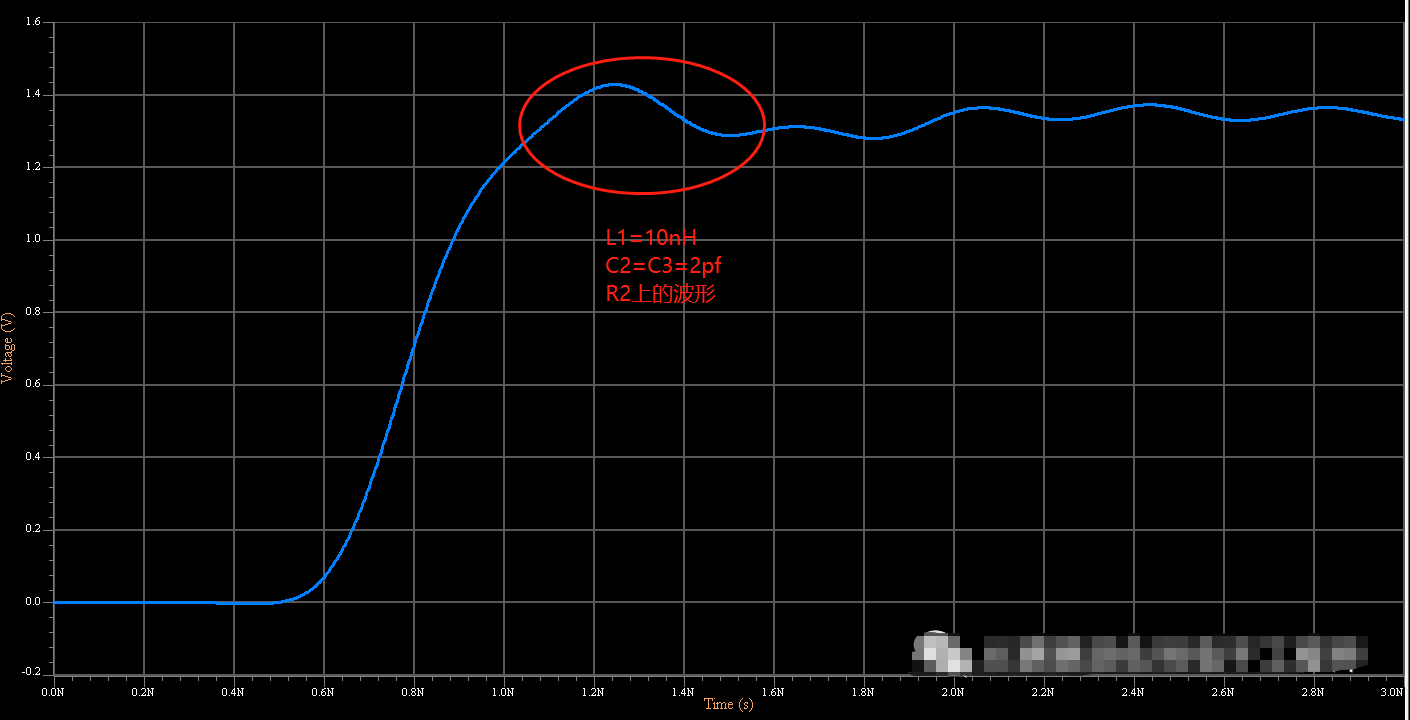

針對L1=10nH,在L1左右兩邊各放置1個2pf電容C2和C3(C2+C3=4pf),仿真電路如下

看仿真結果,信號過沖已經比電容不存在時降低了大約0.2V。

-

pcb

+關注

關注

4347文章

23391瀏覽量

406090 -

連接器

+關注

關注

99文章

15176瀏覽量

139110 -

PCB設計

+關注

關注

396文章

4767瀏覽量

88963 -

信號完整性

+關注

關注

68文章

1431瀏覽量

96360 -

反射

+關注

關注

0文章

69瀏覽量

16001

發布評論請先 登錄

信號完整性(五):信號反射

信號完整性簡介及protel信號完整性設計指南

信號完整性之反射(八)

信號完整性之反射(八)

評論