不管是基于什么方法學Verilog或者SystemVerilog編寫測試平臺,進行仿真的時候都需要將設計代碼例化在頂層模塊(module)中,然后將頂層名指定在仿真命令中,但是從來沒有把頂層進行例化。因為可能會想如果頂層再例化就需要把頂層再例化到另一個module中,然后將這個module的名字再作為新的頂層。。。這樣下去就沒有窮盡了。其實在Verilog和SystemVerilog中,module的例化一般要么是在設計層次結構中被例化,以形成整個層次化的設計,要么就是作為整個仿真環境的頂層module出現進行例化,并且此時給大家的假象是沒有例化。其中第一種例化方式就是“顯式例化”,后一種頂層module實際上是以一種“隱式例化”的方式存在的,那么“隱式例化”和“顯式例化”都有哪些特點和使用上的區別呢?本文將示例說明。

1 隱式例化

隱式例化常見的情況主要出現在頂層模塊在仿真時,頂層模塊會被隱式的進行一次例化,并且這個例化名與頂層module的名字,這樣的一個實例稱之為“頂層實例”,即頂層的“隱式例化”

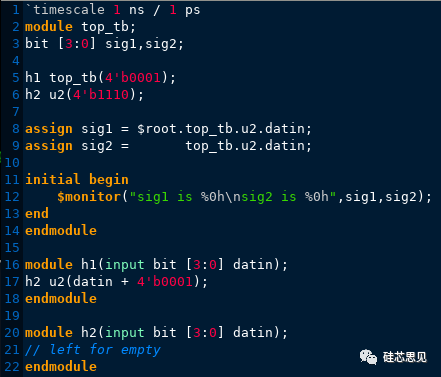

【示例】

【仿真結果】

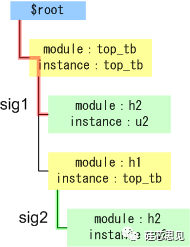

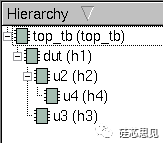

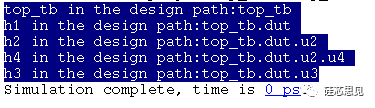

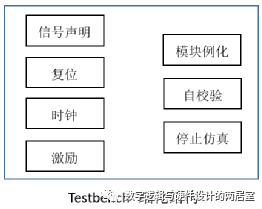

示例中,在頂層top_tb中例化了兩個module(h1和h2),例化名分別是top_tb和u2,其中h1中又例化了h2,也就是h2在頂層top_tb和h1中分別進行了例化,在例化時分別傳遞了對應的參數。其中h1和h2在各層次的例化屬于“顯式例化”,整個代碼的層次結構如下圖所示。

示例中第8行通過層次化引用將u2中的datin的值傳遞給了頂層變量sig1,sig1的值來自于通過$root指向頂層例化名(top_tb,此時的top_tb就是頂層模塊top_tb的“隱式例化”名),在通過頂層top_tb引用其中u2(h2例化),從而實現了對于u2中datin的訪問,因為此時datin的值來自于h2在頂層中例化時傳遞的參數“4’h1110”,所以此時sig1值為“4’h1110”;

示例中第9行,依然是通過層次化引用的方式將u2中的datin的值傳遞給了頂層變量sig2,但是此時需要注意的是這里的top_tb并不是頂層module名也不是頂層module的例化名,而是當前作用域內h1的例化名(top_tb),這里h1在頂層例化時傳入的參數為“4’h0001”該參數通過h1中h2例化的u2傳遞給了datin,此時datin的值為“4’h0010”,所以此時sig2獲得數值為“4’h0010”;

2顯式例化

除了頂層以外,其他模塊的使用都是建立在對應module“顯式例化”的基礎之上,正是通過模塊之間的一次或者多次例化形成了層次化的設計。

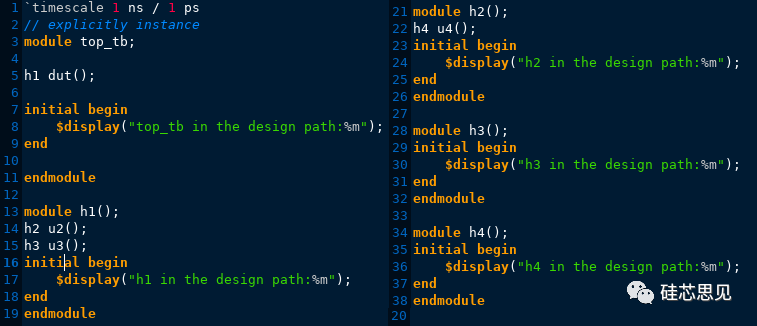

【示例】

【仿真結果】

示例仿真結果可以看到,h1、h2、h3、h4分別在不同的模塊中進行了例化,形成了層次化的結構,這幾個模塊的例化都屬于“顯式例化”。

通過上述示例,在IEEE1800目前版本的SystemVerilog中“隱式例化”主要是指頂層模塊的例化,不需要指明實例名,其實例名與模塊名相同,“顯式例化”則需要指明模塊名和實例名,主要用于模塊之間形成層次化結構時各模塊之間的相互實例化。

審核編輯 :李倩

-

仿真

+關注

關注

51文章

4245瀏覽量

135368 -

Verilog

+關注

關注

29文章

1366瀏覽量

111907 -

變量

+關注

關注

0文章

614瀏覽量

28839

原文標題:仿真時為什么頂層不例化

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

代碼和原理圖設計的頂層文件有什么不同么

使用user design文件夾下的.v文件,如果編寫頂層讀寫控制程序對mig-39-2.v進行例化,如何操作才能使用sim_tb_top.v仿真文件?

FPGA例化問題?

以MIPI項目為例講解Diamond FIFO生成和例化全過程

基于linux系統的VCS使用及仿真說明

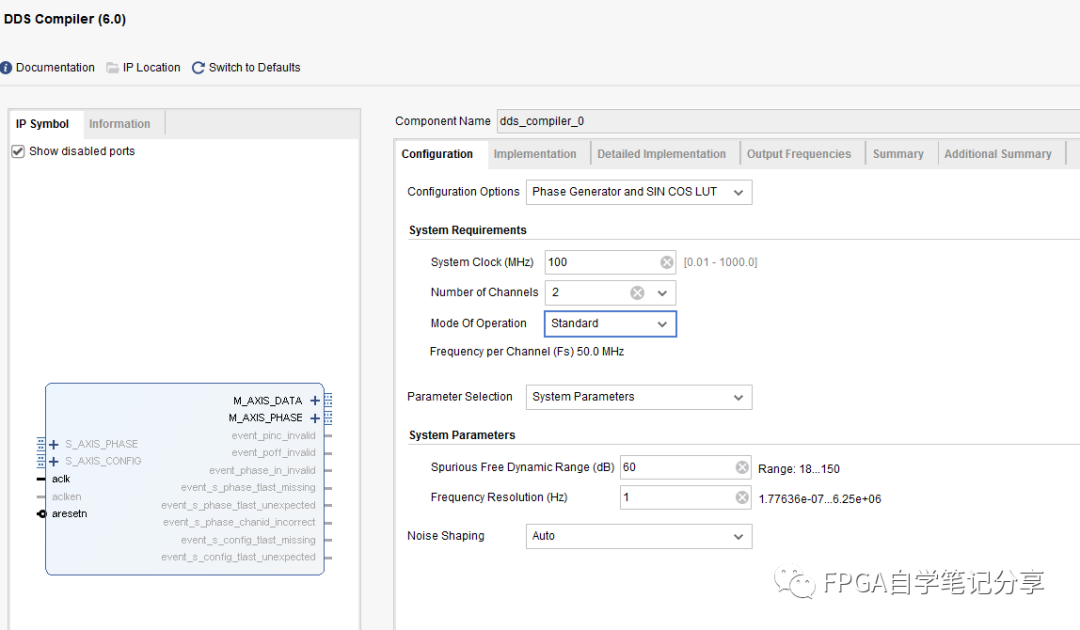

XILINX FPGA IP之DDS Compiler_ip例化仿真

仿真時為什么頂層不例化

仿真時為什么頂層不例化

評論