隨著多芯片系統在半導體領域變得越來越普遍,通用小芯片互連高速(UCIe)規范正在成為焦點。

由于其對高帶寬和高性能的支持,以及其靈活性,UCIe有望成為引領新一輪創新浪潮的黃金標準。

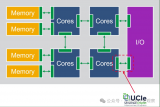

傳統的單片 SoC 正在達到超大規模數據中心的人工智能 (AI)、機器學習 (ML) 和高性能計算 (HPC) 等數據密集型應用的功耗、性能和面積 (PPA) 限制。響應號召的是多芯片系統,由單個芯片或小芯片組成,通過支持離散功能或乘以單個芯片的功能來擴展性能。它們集成在標準或高級包中。

雖然單片芯片正在接近制造上限,但多芯片系統可以提供更多的系統功能、增強的 PPA、更好的良率以及更低的成本來支持先進的設計。UCIe 為可定制的、基于標準的封裝級小芯片集成提供了支持。一個開放的規范,它定義了封裝內小芯片之間的互連。其特性非常適合多芯片系統的要求。

支持當今和未來的帶寬需求

雖然已經出現了幾種不同的標準來解決多芯片系統的挑戰,但UCIe是唯一具有芯片間接口完整堆棧的標準。該規范支持 2D 和 2.5D 包,預計未來將推出 3D 包。其他標準僅關注協議棧的特定層,缺乏確保實現之間互操作性的完整芯片到芯片接口的全面規范。

UCIe 適用于當今每個引腳 8 Gbps 至 16 Gbps 的大部分設計;它還支持每個引腳 32 Gbps 的設計,適用于未來的高帶寬應用,如網絡和超大規模數據中心。有兩種封裝變體可供選擇。用于高級封裝的UCIe支持硅中介層、硅橋和再分布層(RDL)扇出,而用于標準封裝的UCIe支持有機襯底和層壓板。

UCIe 堆棧本身由三層組成。頂部是協議層,它通過基于流控制單元(基于 FLIT)的協議實現確保最大效率和減少延遲。協議層支持常用規范,包括 PCI Express? (PCIe?)、計算快速鏈路 (CXL) 和/或用戶定義的流式處理協議。在第二層,協議進行仲裁和協商,鏈路管理通過芯片到芯片適配器進行。該層實現基于循環冗余校驗 (CRC) 和重試機制的錯誤檢測和糾正功能。PHY 標記第三層,指定與封裝介質的電氣接口。在PHY層中,電模擬前端(AFE)、發射器和接收器以及邊帶通道允許兩個芯片之間進行參數交換和協商。Logic PHY 實現了鏈路初始化、訓練和校準算法以及測試和修復功能。

經過驗證的 IP 如何實現強大的芯片間鏈路

為了簡化UCIe在多芯片系統設計中的應用,設計人員可以轉向PHY、控制器和驗證IP。PHY IP 支持標準和高級封裝選項,可提供靈活性,而在高級 FinFET 工藝中,可支持高帶寬、低功耗和低延遲的芯片間連接。控制器 IP 支持與 PCIe 和 CXL 等常用協議一致的解決方案,并可通過流協議實現延遲優化的片上網絡 (NoC) 到 NoC 鏈路;例如,橋接到 CXS 接口和 AXI 接口。最后,在全棧的每一層支持各種被測設計 (DUT) 的驗證 IP 有助于加快運行時間,以及設計的調試和覆蓋收斂。

正確的 PHY、控制器和驗證 IP 集可以帶來可靠、穩健的芯片間鏈路,具有低延遲和高能效。針對已知良好芯片的內置可測試性功能以及用于糾錯的 CRC 或奇偶校驗檢查支持芯片良率和質量目標。

審核編輯:郭婷

-

soc

+關注

關注

38文章

4354瀏覽量

221827 -

AI

+關注

關注

88文章

34406瀏覽量

275680 -

ML

+關注

關注

0文章

150瀏覽量

34988

發布評論請先 登錄

一文解析UCIe技術細節

Chiplet芯片互聯再進一步,AMD、ARM、英特爾聯手發布UCIe 1.0標準

芯原股份加入UCIe產業聯盟 推動UCIe技術標準應用

淺談UCIe對解決多芯片系統的設計

設計更簡單,運行更穩健,UCIe標準如何“拿捏”Multi-Die系統?

深度詳解UCIe協議和技術

新思科技發布全球領先的40G UCIe IP,助力多芯片系統設計全面提速

XSR芯片間互連技術的定義和優勢

為什么UCIe是多芯片系統的集成互連

為什么UCIe是多芯片系統的集成互連

評論