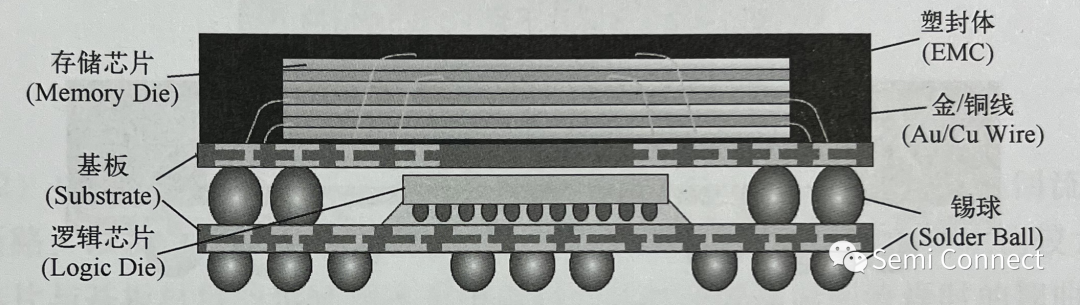

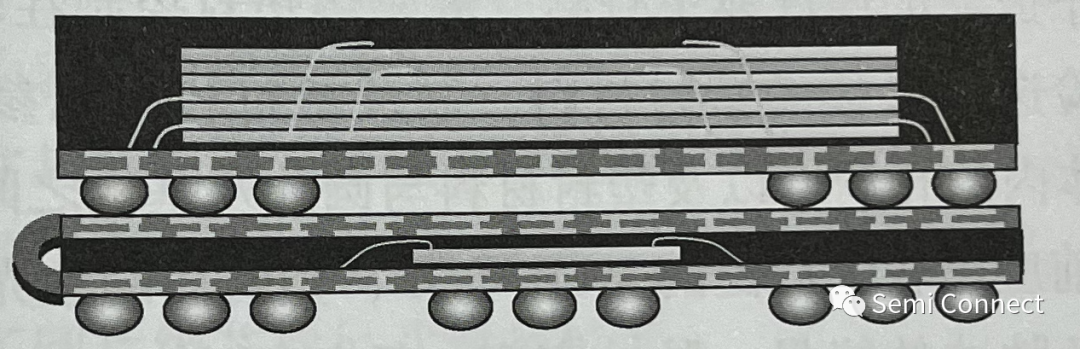

疊層封裝 (Package on Package, PoP)是指在個處于底部具有高集成度的邏輯封裝件上再疊加另一個與之相匹配的大容量存儲器封裝件,形成一個新的封裝整體。這種新的高密度封裝形式,主要應(yīng)用在智能手機、數(shù)碼相機、便攜式穿戴設(shè)備等多種消費類電子產(chǎn)品中。PoP 產(chǎn)品圖如下圖1所示,其基本結(jié)構(gòu)示意圖如下圖2所示。

POP 主要是針對移動設(shè)備而發(fā)展起來的系統(tǒng)集成3D封裝,其結(jié)構(gòu)主要有如下特點。

(1)存儲器件和邏輯器件可自由組合,并可單獨進行測試或替換,保障了成品率。

(2)POP 在垂直方向上實現(xiàn)堆疊,節(jié)省占板面積,提高了系統(tǒng)封裝密度

(3)堆疊器件垂直互連取代了傳統(tǒng)二維封裝互連,可以實現(xiàn)邏輯器件和存儲器件之間更快的數(shù)據(jù)傳輸。隨著技術(shù)的發(fā)展,出現(xiàn)了如下幾類主要的 POP 結(jié)構(gòu)。

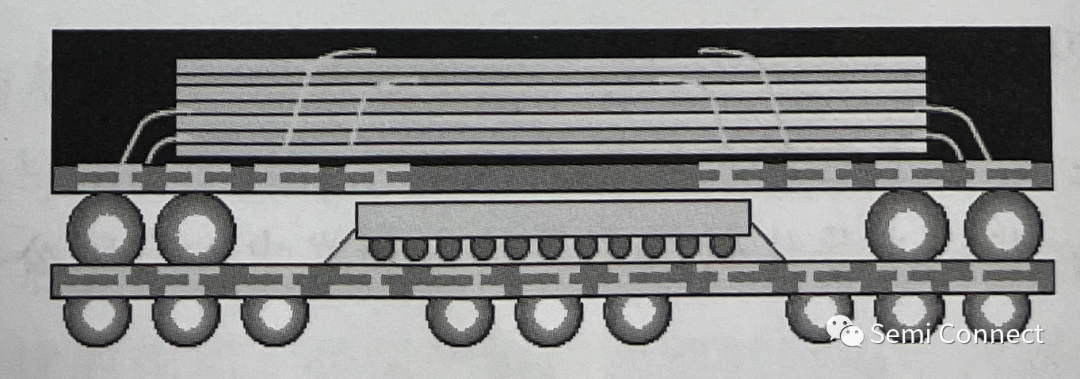

(1)錫球連接 PoP:邏輯芯片擁有更多的I/0 端口,因而常采用倒裝互連(Flip Chip, FC)技術(shù)對其進行封裝,并以此作為底部組件。底部芯片采用毛細(xì)管底部填充工藝(Capillary Under Fill, CUF),其結(jié)構(gòu)示意圖如圖所示。

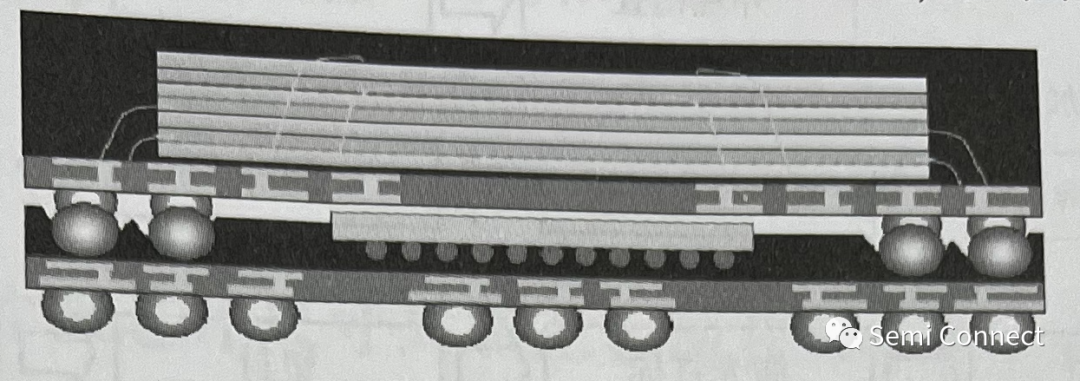

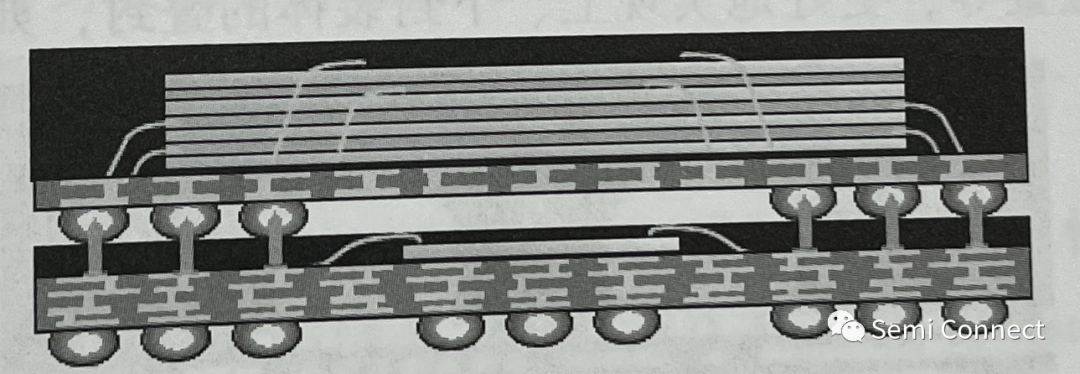

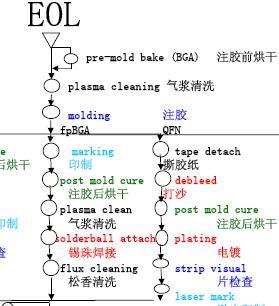

(2) MLP 連按PoP:為了發(fā)展較薄的PoP 封裝結(jié)構(gòu),成型激光封裝( MoldimgLaser Package, MLP)技術(shù)應(yīng)運而生,市場上也稱之為穿塑孔 (Through Mold Via,TMV)技術(shù)。其方法是,首先在底部芯片四周焊接錫球并直接塑封,然后采用激光穿孔方式使錫球露出,以便后續(xù)與上層元器件連按,如圖所示。

(3)折香形式 POP 和 BVA 連接PoP:為了滿足 PoP 產(chǎn)品尺寸薄、功能強、I/0數(shù)多等需求,采用柔性電路板連接各種封裝組件并進行折疊形成 PoP結(jié)構(gòu)2,以及采用 BVA (Bond Via Array),技術(shù)1來提高產(chǎn)品性能、縮小引腳間距,如圖所示。

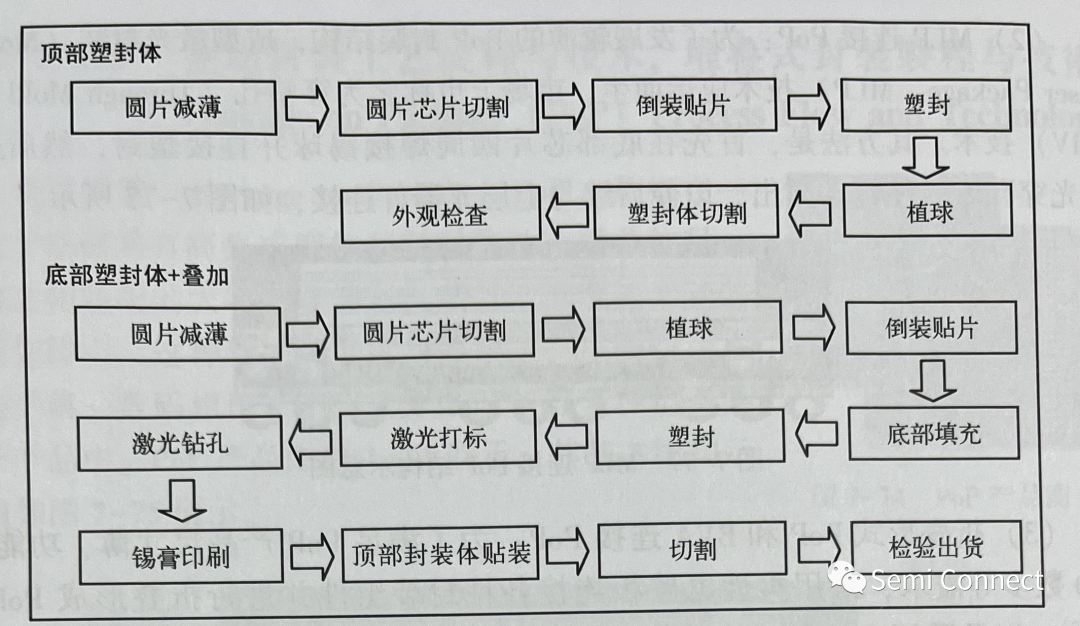

依上所述,POP 封裝體底部組件與頂部組件的連接方式主要有錫球連接(Attached with Solder Ball)、 MIP、柔性基板連接和 BVA。 MLP POP 封裝工藝流程如圖所示

PoP 關(guān)鍵技術(shù)如下所述。

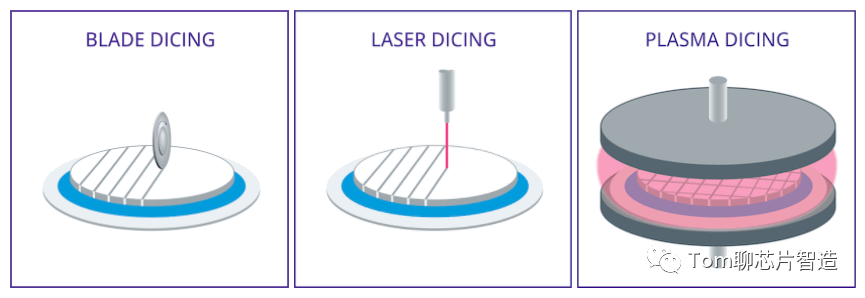

(1) PoP 作為高度集成的 3D 封裝體,對于封裝及圓片的厚度有著更高的要求(低于 100um)。因而對減薄工藝提出了更高的要求,需嚴(yán)格控制并避免出現(xiàn)圓片破裂和芯片裂紋等問題,而且對于厚度薄于 100wm 的圓片進行切割時,易造成芯片剝離藍膜。

(2)由于封裝集成度高,信號端口之間的間距更小 (小于 0.3mom),所以對于植球工藝提出了更高的要求,需要更高精度的植球機,嚴(yán)格控制對推工藝精度。?

(3)POP 對于成品的厚度要求較高,需要將塑封控制在較薄的厚度范圍內(nèi),因而必領(lǐng)通過實驗選擇最佳的塑封材料,以及塑封和固化參數(shù),以避免發(fā)生不完全塑封、塑封體內(nèi)的孔洞,以及塑封材料與圓片及基板之問分層等問題。

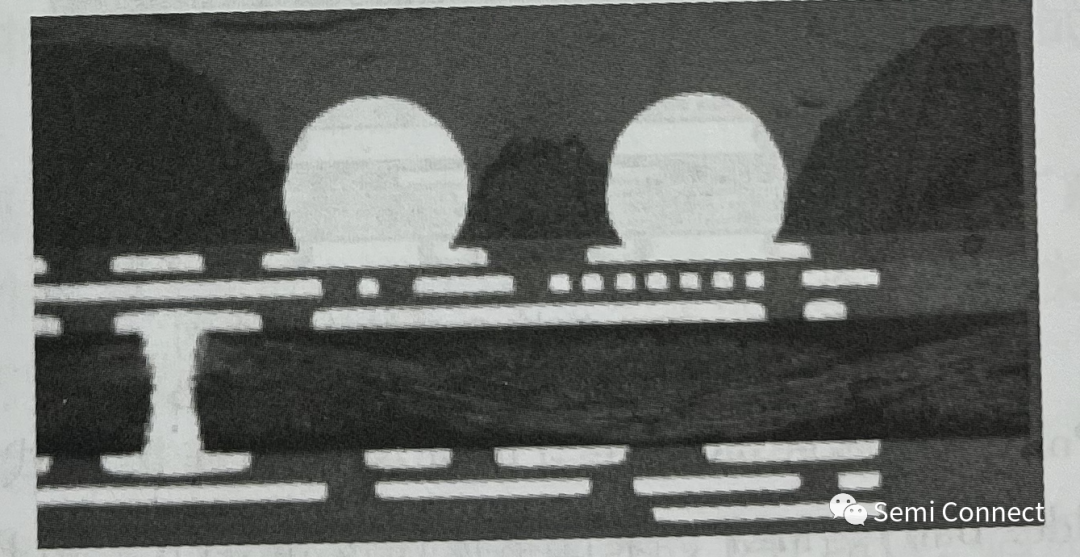

(4)作為目前應(yīng)用較為廣泛的 MLP-POP,塑封后的激光鉆孔尤為重要,因此需要控制好激光脈沖的能量、脈沖寬度、重復(fù)頻率、對位,從而控制好鉆孔的尺寸、形狀、位置等,更好地實現(xiàn)上、下封裝體的疊封,如圖所示。

(5) PoP作為高度集成的兩個封裝體的疊加,對于上、下封裝體的翹曲有著較高的要求,應(yīng)盡量使上、下封裝體具有相同的翹曲方向,從而實現(xiàn)疊加上的一致性。對于封裝體翹曲過大的情況,需要更好地控制香加時的錫膏量。進行新產(chǎn)品評估時,需要專門評估分析上、下封裝體的翹曲數(shù)據(jù)。

審核編輯:湯梓紅

-

存儲器

+關(guān)注

關(guān)注

38文章

7637瀏覽量

166529 -

封裝

+關(guān)注

關(guān)注

128文章

8561瀏覽量

144875 -

邏輯器件

+關(guān)注

關(guān)注

0文章

88瀏覽量

20354 -

工藝流程

+關(guān)注

關(guān)注

7文章

112瀏覽量

16522 -

封裝工藝

+關(guān)注

關(guān)注

3文章

64瀏覽量

8121

原文標(biāo)題:疊層封裝工藝流程與技術(shù),堆疊式封裝製程與技術(shù)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

半導(dǎo)體封裝工藝流程的主要步驟

疊層封裝工藝流程與技術(shù)

疊層封裝工藝流程與技術(shù)

評論