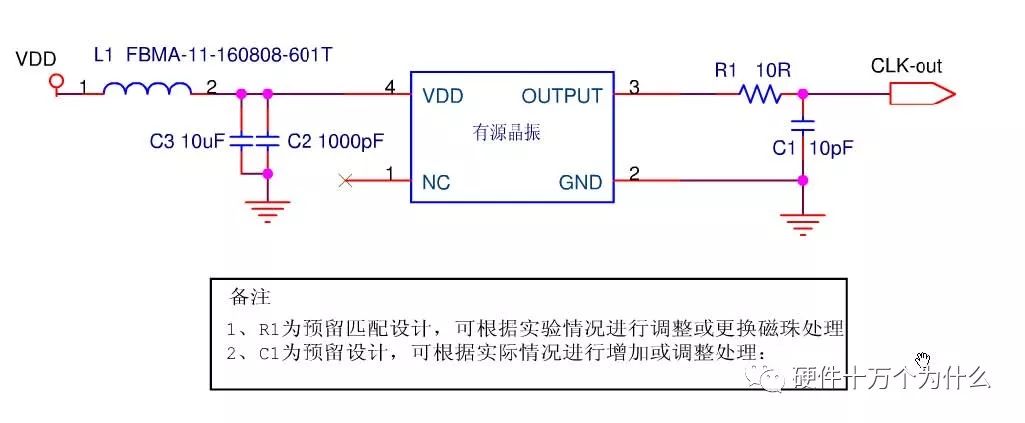

原理圖設計要點:

(1)、晶振電源去耦非常重要,建議加磁珠,去耦電容選兩到三個,容值遞減。

(2)、時鐘輸出管腳加匹配,具體匹配阻值,可根據測試結果而定。

(3)、預留的電容C1,容值要小,構成了一級低通濾波,電阻、電容的選擇,根據具體測試結果而定。

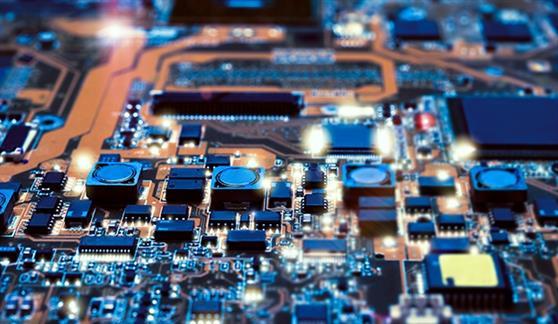

PCB設計要點:

(1)、在PCB設計是,晶振的外殼必須接地,可以防止晶振的向往輻射,也可以屏蔽外來的干擾。

(2)、晶振下面要鋪地,可以防止干擾其他層。因為有些人在布多層板的時候,頂層和底層不鋪地,但是建議晶振所在那一塊鋪上地。

(3)、晶振底下不要布線,周圍5mm的范圍內不要布線和其他元器件(有的書是建議300mil范圍內,大家可以參考),主要是防止晶振干擾其他布線和器件。

(4)、晶振不要布在板子的邊緣,因為為了安全考慮,板卡的地和金屬外殼或者機械結構常常是連在一起的,這個地我們暫且叫做參考接地板,如果晶振布在板卡的邊緣,晶振與參考接地板會形成電場分布,而板卡的邊緣常常是有很多線纜,當線纜穿過晶振和參考接地板的電場是,線纜被干擾了。而晶振布在離邊緣遠的地方,晶振與參考接地板的電場分布被PCB板的GND分割了,分布到參考接地板電場大大減小了。

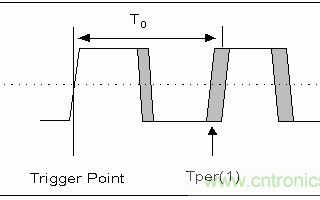

(5)、當然時鐘線盡量要短。如果你不想讓時鐘線走一路干擾一路,那就布短吧。還有一點,關于晶振的選擇,如果你的系統能工作在25M,就盡量不要選50M的晶振。時鐘頻率高,是高速電路,時鐘上升沿陡也是高速電路,需要考慮信號完整性。

審核編輯:湯梓紅

-

pcb

+關注

關注

4367文章

23485瀏覽量

409510 -

有源晶振

+關注

關注

1文章

931瀏覽量

21334 -

晶振

+關注

關注

35文章

3262瀏覽量

70091 -

PCB設計

+關注

關注

396文章

4801瀏覽量

90354 -

emc

+關注

關注

172文章

4164瀏覽量

186909

原文標題:有源晶振的EMC方面的設計考慮

文章出處:【微信號:EMC電磁兼容,微信公眾號:EMC電磁兼容】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

有源晶振的EMC方面的設計考慮

有源晶振的EMC方面的設計考慮

評論