產品描述

Versal HBM 棧可通過內部 HSM0 參考時鐘來進行時鐘設置,此參考時鐘是由 CIPS 或外部時鐘源生成的。

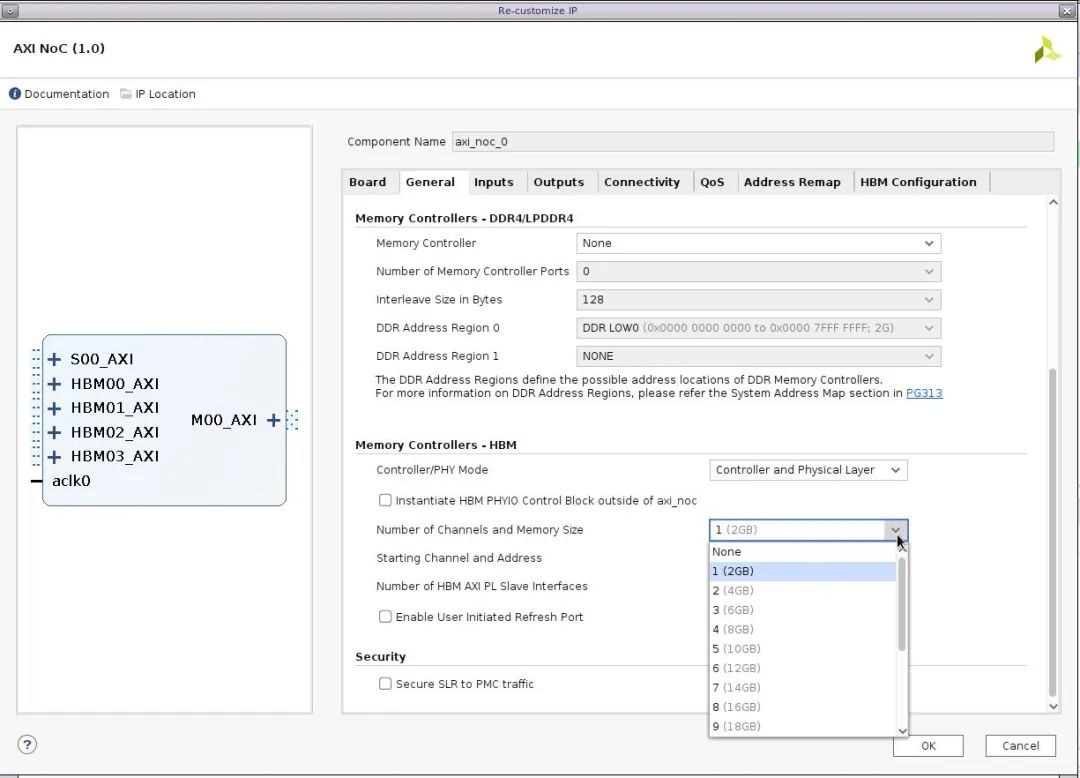

通過 AXI NoC 配置 GUI 啟用 HBM 時,將顯示一個額外的“HBM Configuration”(HBM 配置)選項卡。以下截屏顯示 AXI NoC 配置,其中已啟用 HBM 通道并導致出現“HBM Configuration”選項卡:

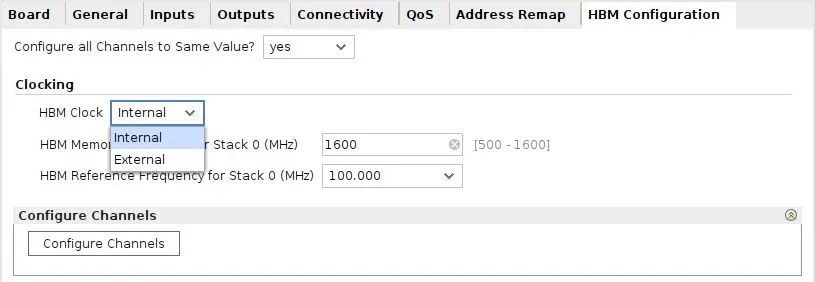

在“HBM Configuration”選項卡中,用戶可以通過“HBM Clock”(HBM 時鐘)下拉菜單選擇“Internal”(內部)或“External”(外部)源,如下所示:

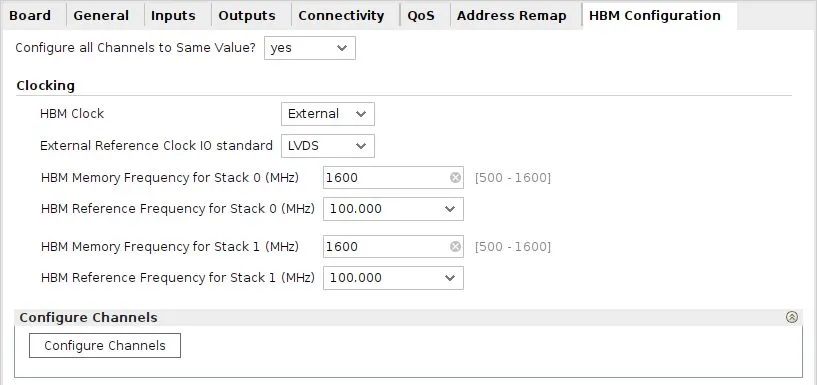

用戶可搭配 Versal HBM 系列器件來使用單棧或雙棧 HBM 器件。每個 HBM 棧都需要參考時鐘。當 AXI NoC 實例配置為同時啟用這 2 個 HBM 棧后,GUI 會自動更新 2 個時鐘源。

使用 HBM 棧時,這兩個棧應同時使用內部時鐘設置或者同時使用外部時鐘設置。使用 External 時鐘設置時,兩者應使用相同的“External Reference Clock IO Standard”(外部參考時鐘 IO 標準)選項。

示例如下:

當 HBM 棧配置為使用 Internal 時鐘設置時,工具將自動把器件配置為根據“HBM Reference Frequency for Stack”(HBM 棧參考頻率)字段中設置的頻率來生成并傳輸 HSM0 時鐘。

解決方案

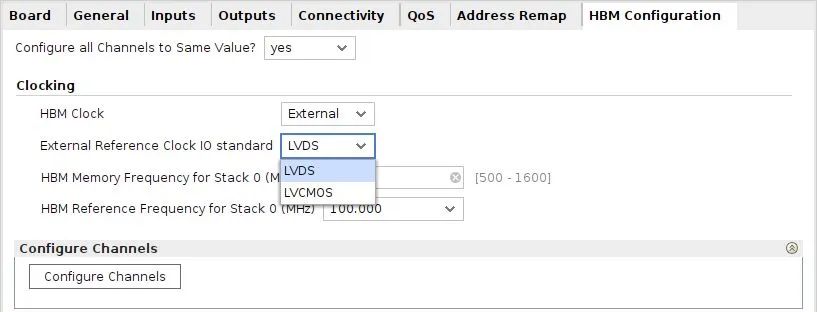

為 Versal HBM 系列參考時鐘使用 External 時鐘設置時,可以選擇 LVDS 或 LVCMOS I/O 標準,如下所示:

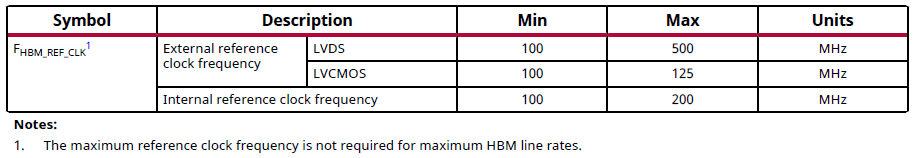

LVDS 和 LVCMOS 的最小時鐘頻率均為 100MHz,而其各自的最大時鐘頻率分別為 500MHz 或 125MHz,如下所示:

如需了解此信息以及有關 Versal HBM 器件要求的其他詳細信息,請參閱《Versal HBM 系列數據手冊:DC 和 AC 開關特性》(DS960)

https://docs.xilinx.com/r/en-US/ds960-versal-hbm

外部參考時鐘應保持穩定運行一段時間,然后才能啟動 HBM 棧。

外部參考時鐘應持續運行,既不停止也不更改時鐘周期。

外部參考時鐘的 RMS 抖動應少于 3ps,占空比應為 50/50。

不支持擴展頻譜時鐘設置。

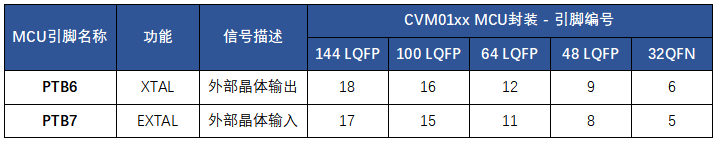

HBM 參考時鐘管腳名稱采用 C4CCIO_PAD0_800/801 和 C4CCIO_PAD1_800/801 格式,其中 800 和 801 表示器件上的特定 HBM 棧。PAD0 是“P”側,PAD1 則是“N”側。

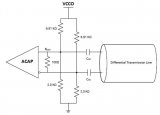

下圖顯示了使用 LVDS、LVCMOS 或 Internal 時鐘設置選項時的外部電路要求。

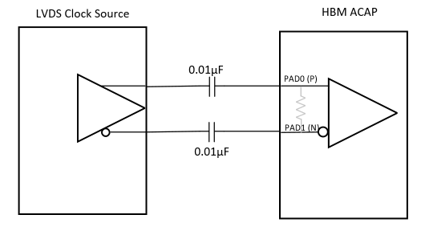

LVDS

將 0.01μF 電容器與 P 管腳和 N 管腳串聯,如下所示:

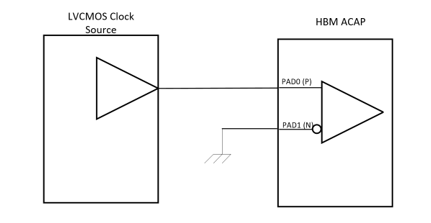

LVCMOS

將 P 輸入直接連接到時鐘源,將 N 輸入接地,如下所示:

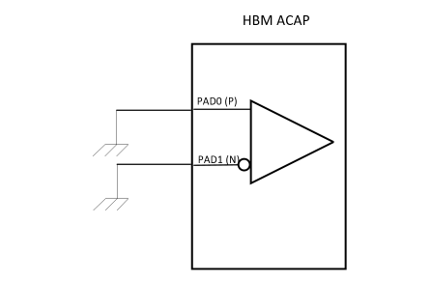

內部時鐘設置

使用內部時鐘選項時,P 輸入和 N 輸入都接地,如下所示:

重要

使用任一外部時鐘設置選項(LVDS 或 LVCMOS)時,無需其他 I/O 標準約束或用戶干預。這些端口不需要額外的 I/O 標準或 I/O 約束,所以手動添加額外標準或約束將會生成錯誤。

審核編輯:湯梓紅

-

時鐘

+關注

關注

11文章

1887瀏覽量

132933 -

NoC

+關注

關注

0文章

39瀏覽量

11902 -

AXI

+關注

關注

1文章

135瀏覽量

17137 -

HBM

+關注

關注

1文章

409瀏覽量

15138 -

Versal

+關注

關注

1文章

169瀏覽量

8043

原文標題:開發者分享|Versal HBM 系列 - 外部參考時鐘設計指南文章

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DSP芯片如何選擇外部時鐘?

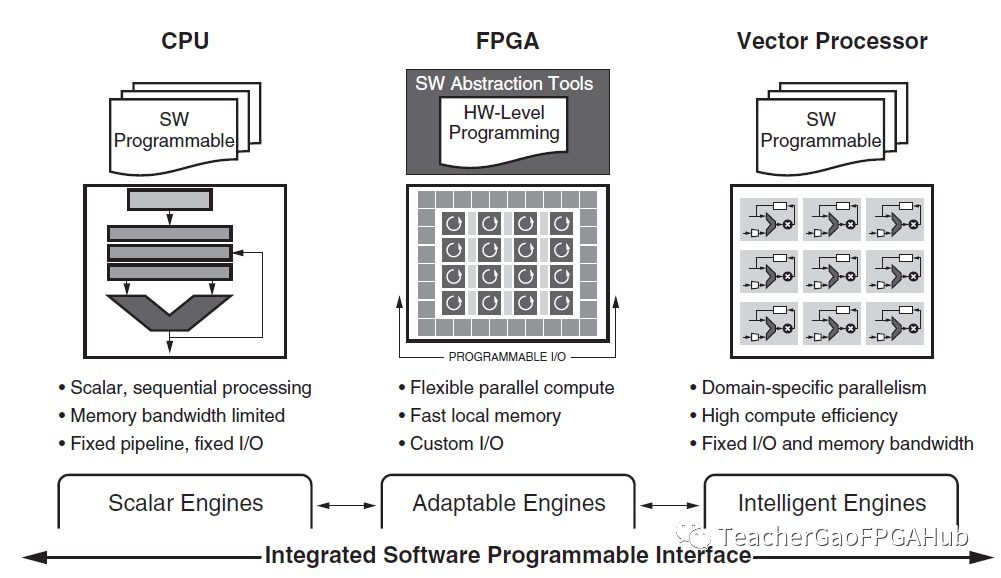

Versal系列芯片三個產品的基礎知識

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部參考時鐘設計指南

Versal ACAP收發器向導 LogiCORE IP產品指南

用于PCI Express的Versal ACAP集成塊產品指南

AMD Versal HBM 自適應 SoC 已投入量產

Versal HBM系列外部參考時鐘設計指南文章

Versal HBM系列外部參考時鐘設計指南文章

評論