芯片已經無處不在:從手機和汽車到人工智能的云服務器,所有這些的每一次更新換代都在變得更快速、更智能、更強大。創建更先進的芯片通常涉及縮小晶體管和其他組件并將它們更緊密地封裝在一起。然而,隨著芯片特征變得更小,現有材料可能無法在所需厚度下實現相同性能,從而可能需要新的材料。

泛林集團發明了一種名為SPARC的全新沉積技術,用于制造具有改進電絕緣性能的新型碳化硅薄膜。重要的是,它可以沉積超薄層,并且在高深寬比的結構中保持性能,還不受工藝集成的影響,可以經受進一步處理。SPARC將泛林無與倫比的等離子技術與化學和工藝工程相結合,實現了先進邏輯和DRAM集成設計的進一步發展。

提高邏輯器件性能

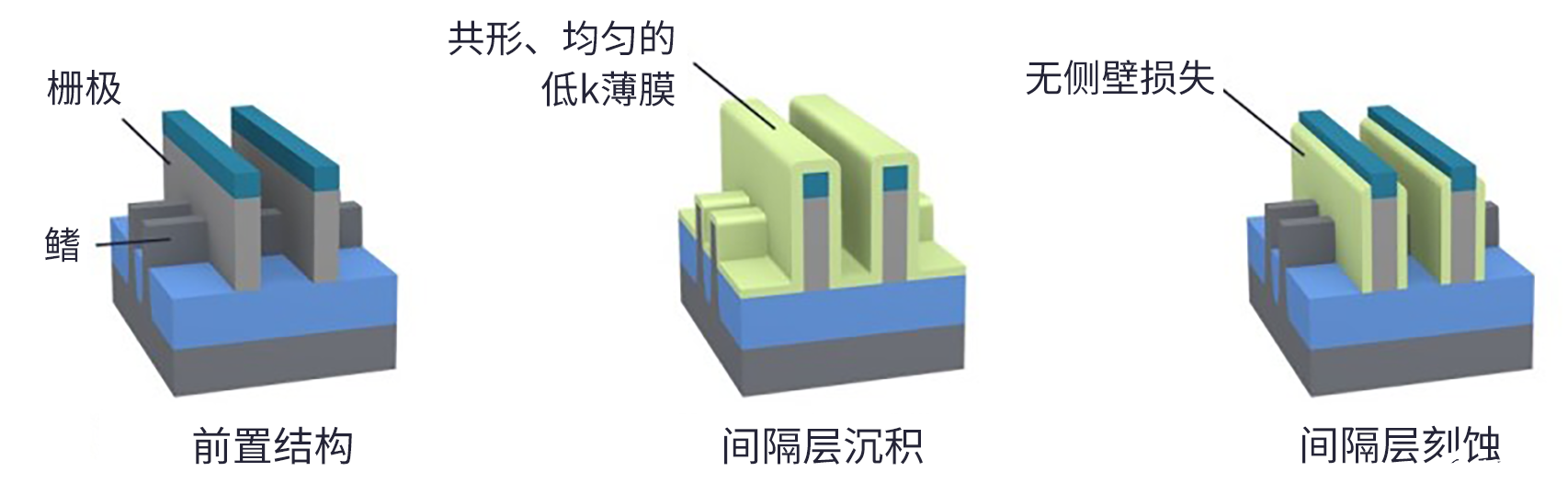

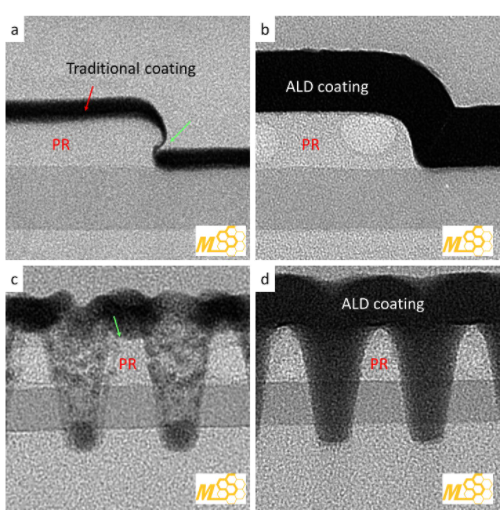

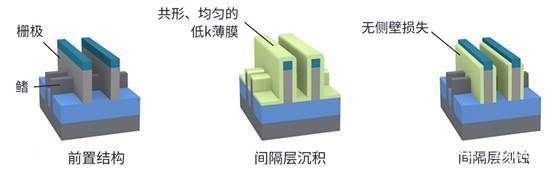

SPARC的一個關鍵邏輯應用是FinFET間隔層。如下面的流程所示,間隔膜沉積在前置結構的柵極和鰭上。薄膜必須遵循現有結構的精確輪廓,并保持厚度一致(結構均勻性)。它還必須對下面的層具有出色的附著力,且沒有針孔或其他缺陷。此外,除了在柵極側壁的所需位置外,它還必須易于從其他任何地方移除。

薄膜本身就有要求。隨著晶體管按比例縮小,柵極模塊中的電容耦合會增加,從而降低整體晶體管的性能。SPARC碳化物薄膜是電絕緣性能更佳的新型材料的絕佳例子,即所謂的“低k薄膜”,用于最大限度地減少這種耦合。現有的低k薄膜通常很脆弱,無法承受后續步驟中使用的強烈的化學物質,因而會導致整體芯片性能不佳。

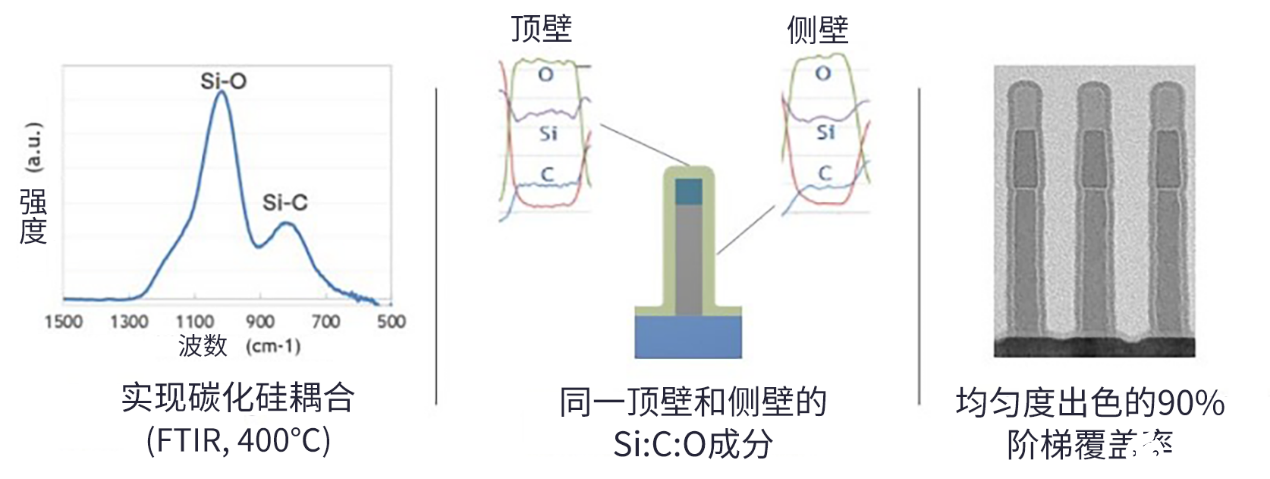

泛林的SPARC技術可提供均勻、堅固的低k薄膜,其厚度和特征內部的成分都是均勻的。SPARC薄膜被輕柔地沉積,沒有直接的等離子體對下面的敏感器件造成損壞,它通過使用由具有遠程等離子體和新型前驅體的獨特反應器產生的自由基來實現。與直接等離子體增強原子層沉積(ALD)薄膜不同,它可以輕松調整薄膜成分,以更好地預防損壞,優化干法或濕法刻蝕的選擇性。得到的薄膜很薄、無針孔,并且可以在芯片制造過程的其余環節保持正確的硅碳(Si-C)鍵合結構,從而保持其介電性能和堅固。

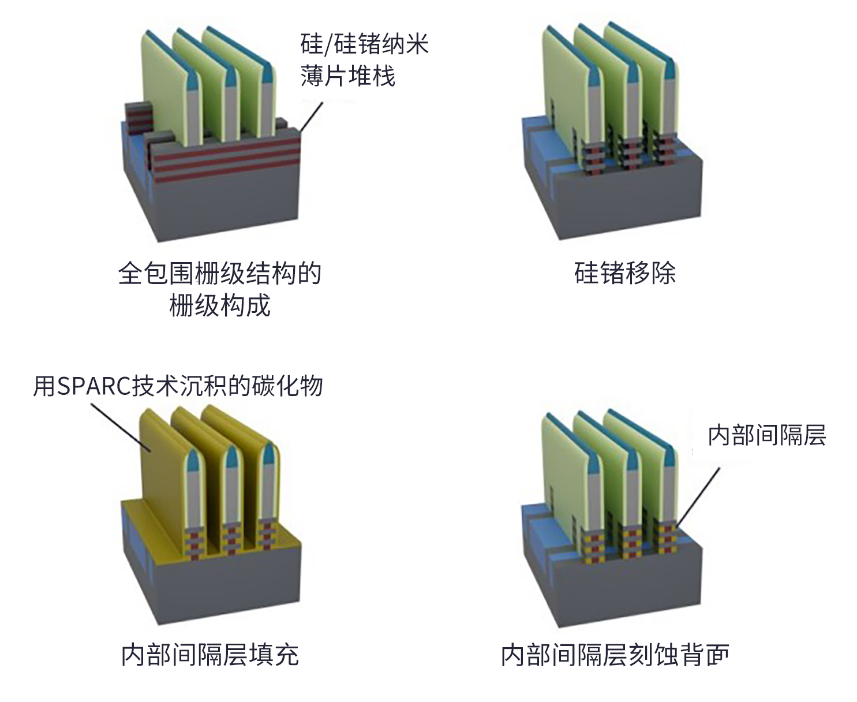

隨著全包圍柵極(GAA)架構的出現,泛林SPARC技術的價值變得愈加明顯。新的內部間隔層應用需要一種材料來降低器件的寄生電容——即降低器件之間的干擾。該薄膜還必須在硅鍺溝道釋放過程中作為外延處理的源極/漏極的保護層。SPARC沉積的薄膜為該應用帶來了關鍵特性,包括低k值,均勻性,高圖形負載,均勻厚度,對硅基、氧化物、碳類型材料的出色刻蝕選擇性,以及器件中的極低泄漏。

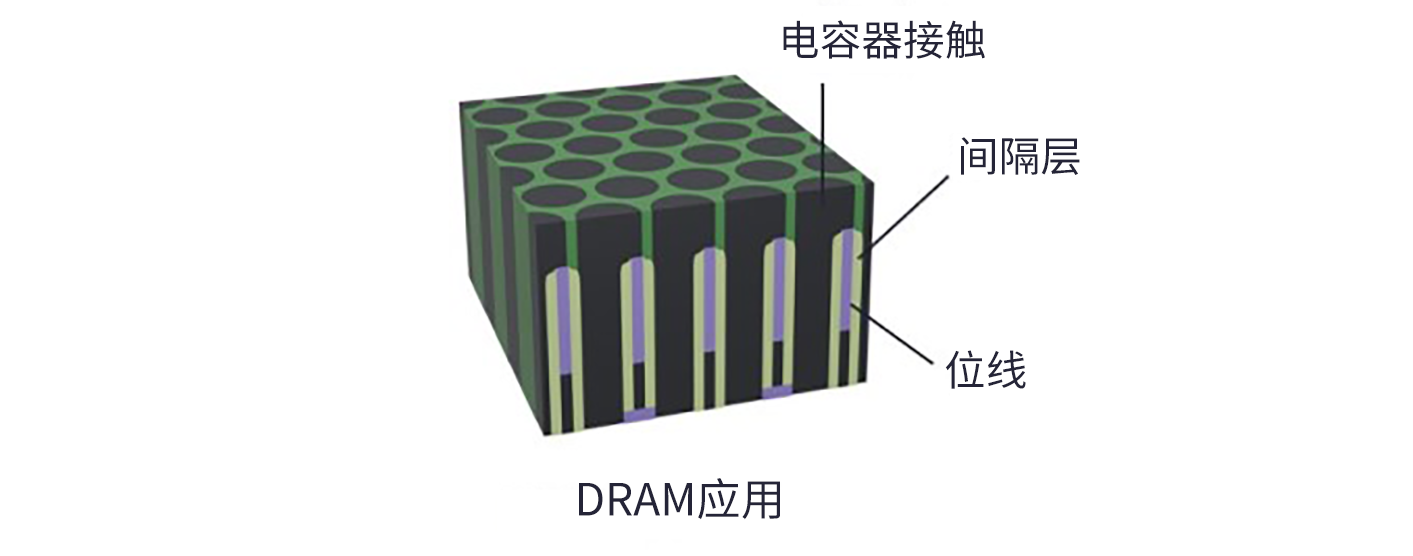

同樣有利于DRAM架構

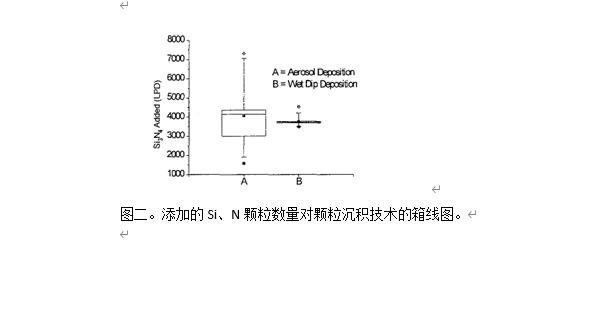

隨著器件的微縮,工程師們不斷努力減少位線和電容器觸點之間的電容,以保持良好的信號/噪聲進行位感應。位線深寬比的增加也使傳統的沉積方法難以成功。位線電容的一個重要組成部分是位線和存儲節點觸點(SNC)之間的耦合,隨著單位面積封裝越來越多的器件以降低DRAM成本和增加密度,該耦合正在增加。為了減少這種耦合,自1x nm技術節點以來,SPARC沉積的低k間隔材料至關重要。

理想的低k薄膜

使用SPARC或單個前驅體活化自由基腔室技術制造的碳化硅氧化物(SiCO)薄膜具備密度大、堅固耐用、介電常數低~ 3.5-4.9、泄漏率低、厚度和成分共形性極佳等特點。在250°C至600°C的廣泛溫度范圍內,碳完全交聯,末端甲基極少甚至沒有,與其他薄膜(如SiOC、SiOCN或SiCN)相比,該薄膜具有熱穩定性和化學穩定性。

在SPARC SiCO系列中,遠程等離子體、獨特的前驅體和工藝空間可實現廣泛的成分調整。此外,這些SPARC SiCO薄膜在稀氫氟酸和熱磷酸等典型濕法化學物質中的WER(濕法刻蝕速率)為零,因此還提供近乎無限的濕法刻蝕選擇性。這些薄膜也是連續的且無針孔的,厚度低于普通替代的一半。

由于這些特性,SPARC SiCO薄膜在某些間隔物應用中實現厚度最小化,是個很有吸引力的選擇。鑒于其對高深寬比堆棧材料的顯著濕法選擇性或等離子體損傷預防,這些薄膜能夠形成氣隙,減少電容耦合,并保護高深寬比堆棧中容易氧化或損壞的工藝元件。SPARC技術已被領先技術節點的所有主要邏輯/代工廠和DRAM制造商采用。隨著集成度和性能擴展挑戰的提升以及深寬比的提高,下一個節點應用程序空間預計將增加。

責任編輯:彭菁

-

DRAM

+關注

關注

40文章

2343瀏覽量

185374 -

SPARC

+關注

關注

0文章

16瀏覽量

10012 -

云服務器

+關注

關注

0文章

806瀏覽量

13802

發布評論請先 登錄

集成電路制程設備領域原子層沉積技術解析

全新沉積技術SPARC實現先進邏輯和DRAM集成設計

抗輻射SPARC處理器在航天應用中有什么優勢?

SPARC結構與實時內核的移植

Mouser推出全新可編程邏輯技術網站

關于SPARC微處理器綜述

泛林集團宣布推出一種用于沉積低氟填充鎢薄膜的新型原子層沉積 (ALD) 工藝

多家DRAM廠商開始評估采用EUV技術量產

MICRON Inside 1α:世界上最先進的DRAM技術

晶片表面沉積氮化硅顆粒的沉積技術

SPARC:用于先進邏輯和 DRAM 的全新沉積技術

HKMG工藝在DRAM上的應用

適用于Solaris 10和11、x86和SPARC的Avago驅動程序

SPARC:用于先進邏輯和 DRAM 的全新沉積技術

SPARC:用于先進邏輯和 DRAM 的全新沉積技術

評論