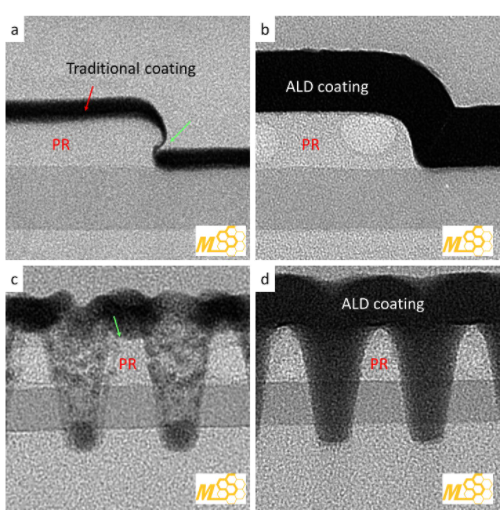

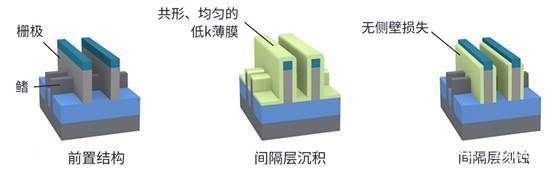

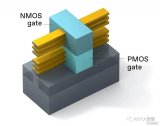

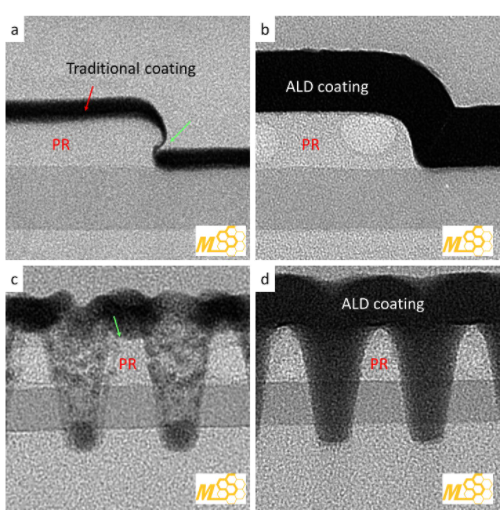

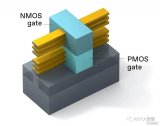

精準(zhǔn)的鍍膜厚度控制。隨著邏輯制程演進(jìn),原本二維的晶體管架構(gòu)已經(jīng)被三維的鰭魚式晶體管(FinFET)取代,關(guān)鍵尺寸(Critical dimension, CD)也由深次微米進(jìn)入到目前只有單一數(shù)字的納米大小,對于鍍膜的批覆性與厚度控制都有最嚴(yán)苛的要求,這讓原子層沉積技術(shù)成為先進(jìn)

2021-02-05 15:23:17 4743

4743

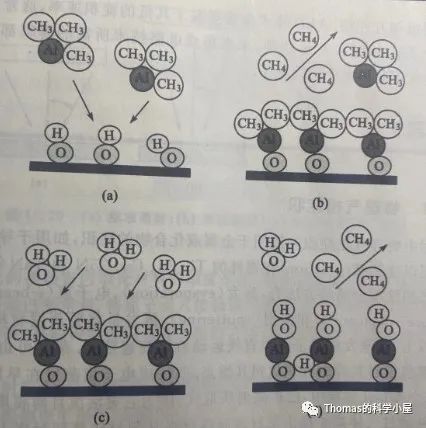

單晶圓系統(tǒng)也能進(jìn)行多晶硅沉積。這種沉積方法的好處之一在于能夠臨場進(jìn)行多晶硅和鎢硅化物沉積。DRAM芯片中通常使用由多晶硅-鈞硅化物形成的疊合型薄膜作為柵極、局部連線及單元連線。臨場多晶硅/硅化物沉積

2022-09-30 11:53:00 1235

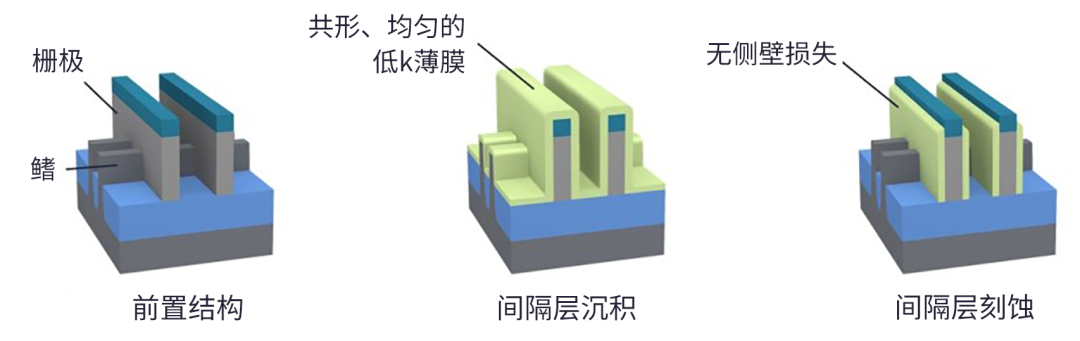

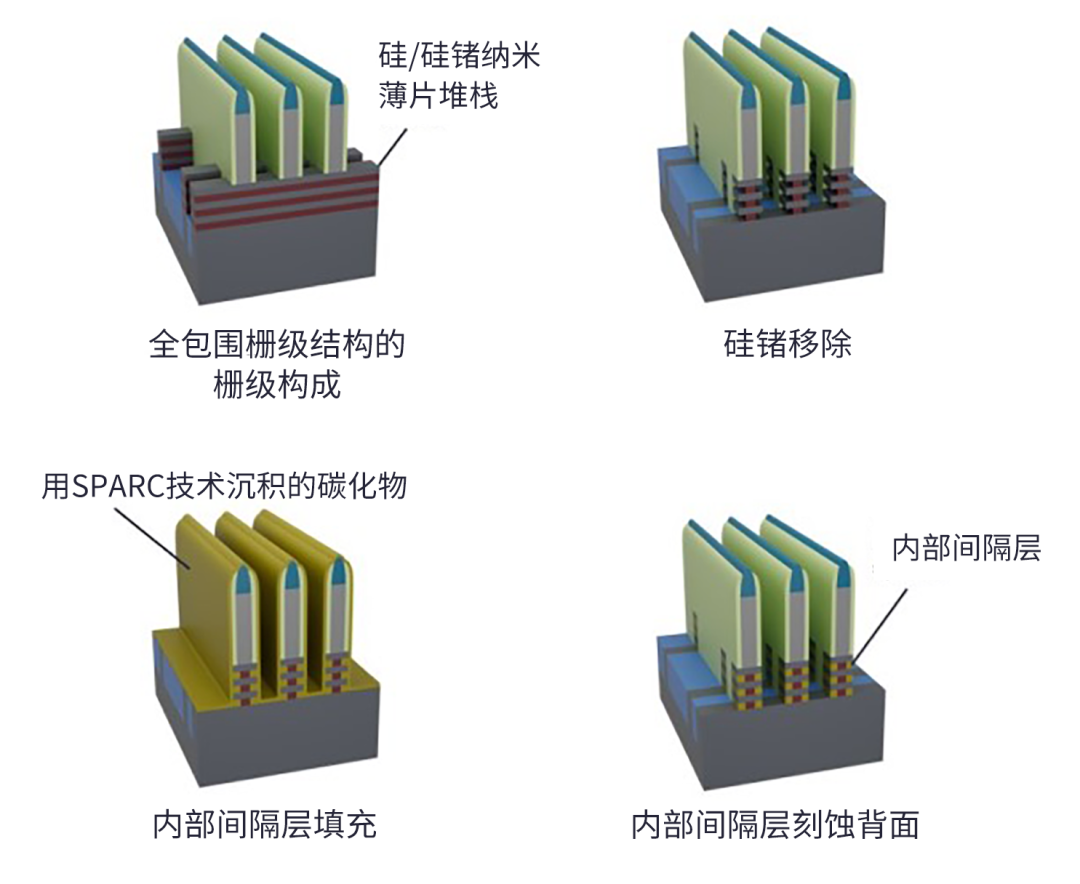

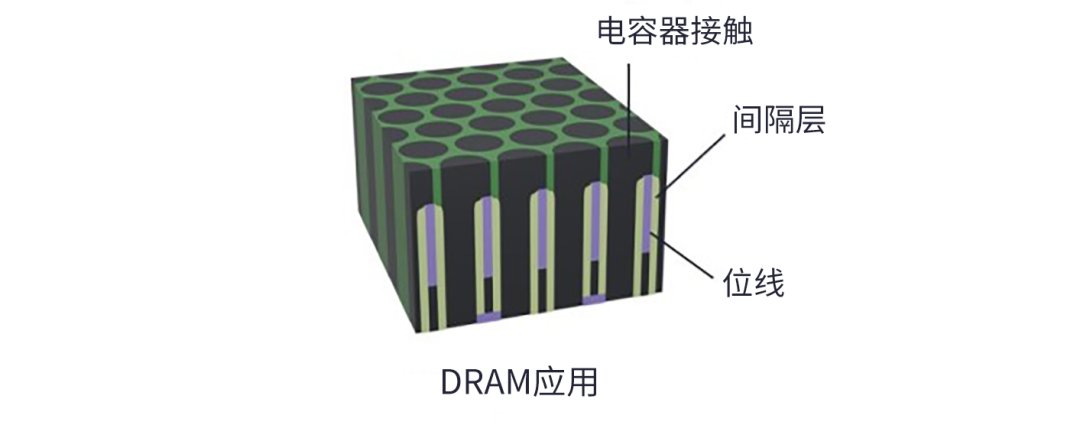

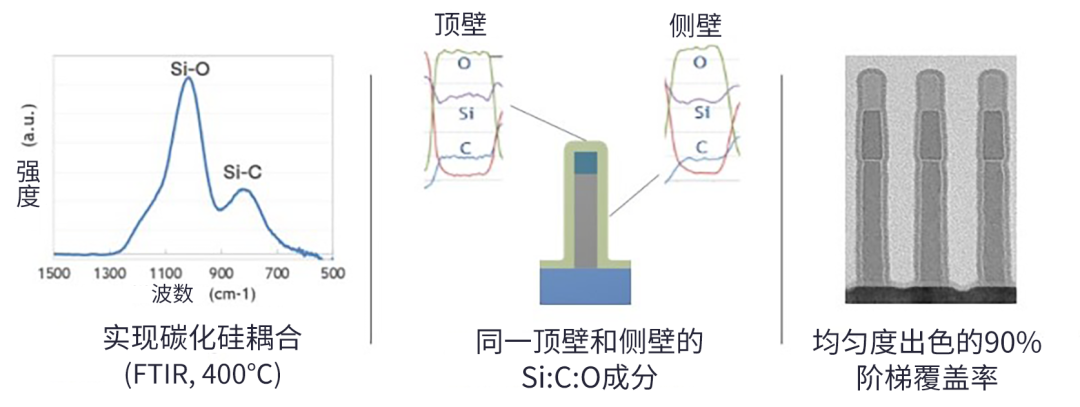

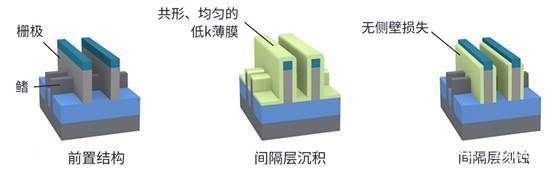

1235 SPARC沉積技術(shù)可滿足新興需求,為邏輯和DRAM器件提供有效隔離 作者:泛林集團(tuán)公司副總裁兼電介質(zhì)原子層沉積產(chǎn)品總經(jīng)理Aaron Fellis 提升集成電路中的介電層性能可以在現(xiàn)在和未來的存儲(chǔ)器

2023-08-08 14:22:28 605

605

電 化 學(xué) 沉 積 技 術(shù), 簡 稱 ECD(Electrical Chemical Deposition)技術(shù),也是應(yīng)用于半導(dǎo)體相關(guān)技術(shù)行業(yè)的電鍍技術(shù),作為集成電路制造的關(guān)鍵工藝技術(shù)之一,它是實(shí)現(xiàn)電氣互連的基石。

2023-11-29 10:07:20 609

609

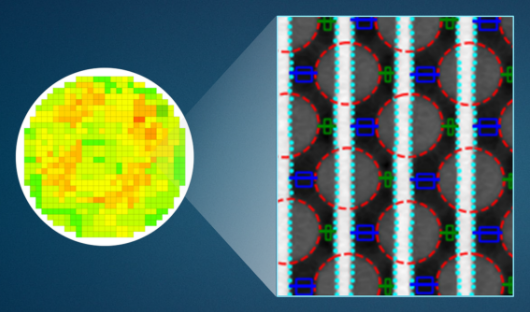

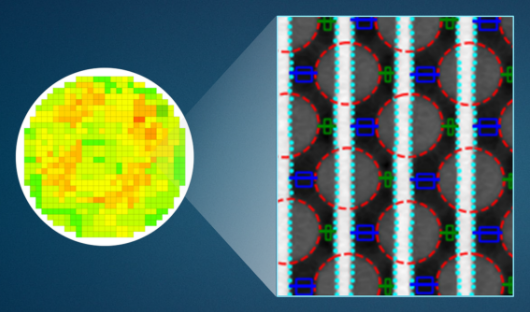

KLA全新的PWG5? 圖形晶圓幾何量測系統(tǒng)和Surfscan? SP7XP無圖案晶圓缺陷檢測系統(tǒng)支持先進(jìn)邏輯、DRAM和3D NAND產(chǎn)品的開發(fā)與生產(chǎn)。

2020-12-14 10:44:02 2139

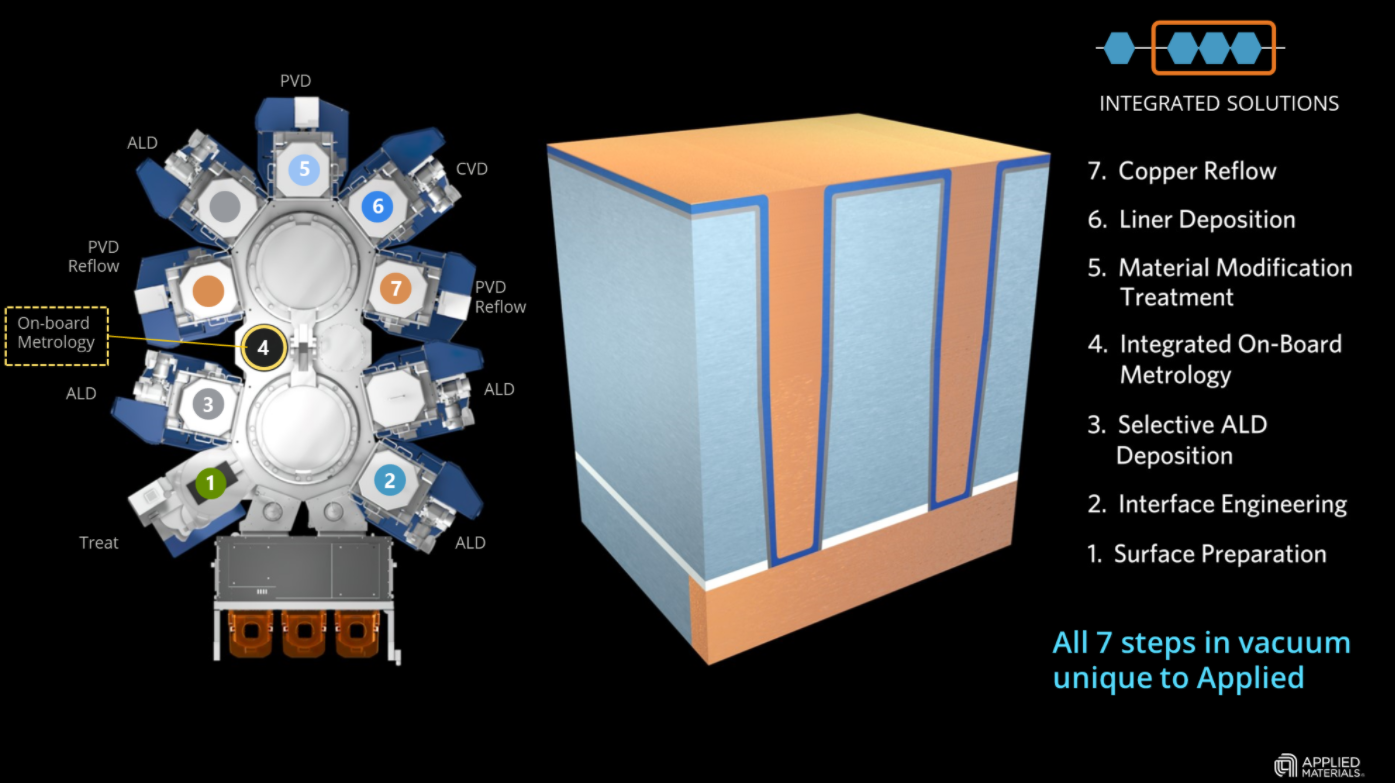

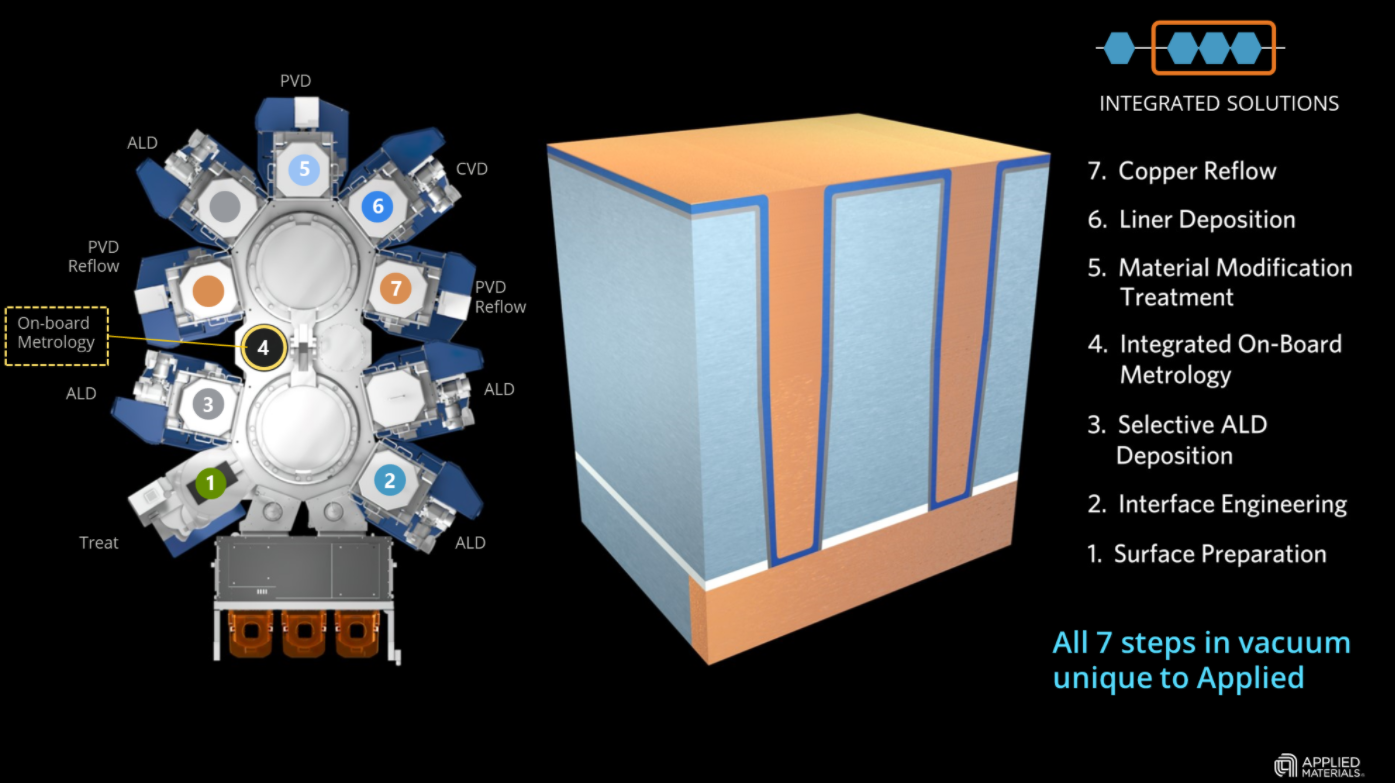

2139 應(yīng)用材料公司推出了一種全新的先進(jìn)邏輯芯片布線工藝技術(shù),可微縮到3納米及以下技術(shù)節(jié)點(diǎn)。

2021-06-18 10:21:42 868

868

PROVision 3E系統(tǒng)包含多種技術(shù)特征,支持當(dāng)下最先進(jìn)設(shè)計(jì)所需的圖形化控制能力,包括3納米晶圓代工邏輯芯片、全環(huán)繞柵極晶體管以及下一代 DRAM和3D NAND。

2021-10-19 16:08:07 1913

1913

? 電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))軍事和特種工業(yè)裝備對于設(shè)備的要求往往較為獨(dú)特,尤其是在航空航天領(lǐng)域。在過去的航天設(shè)備電子系統(tǒng)中,SPARC架構(gòu)的處理器因?yàn)槠涓呖煽啃垣@得了青睞,以至于目前大部分航空

2022-12-21 02:26:00 1419

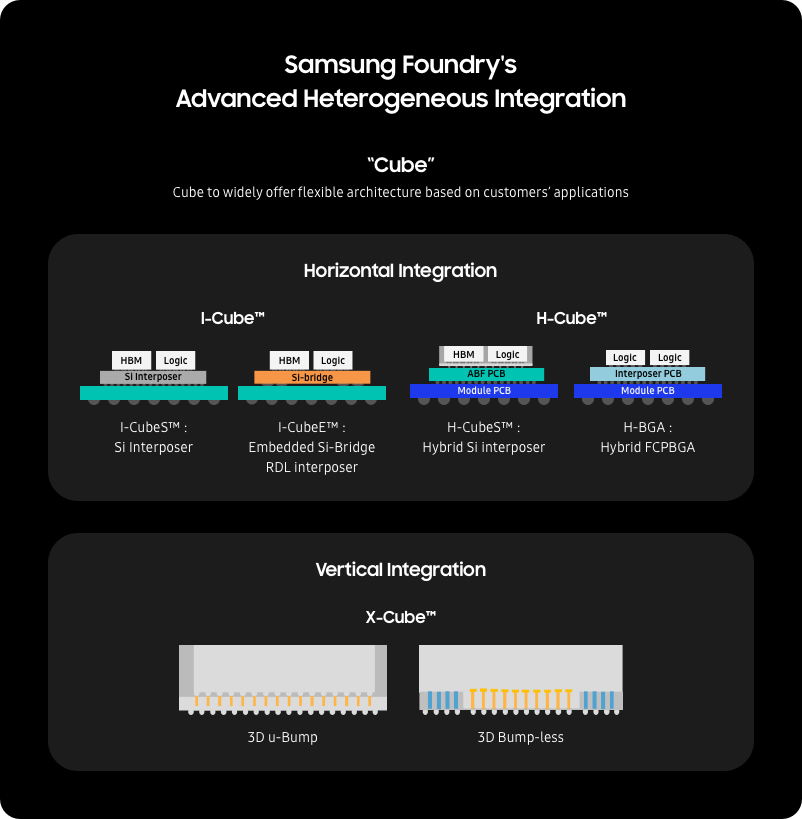

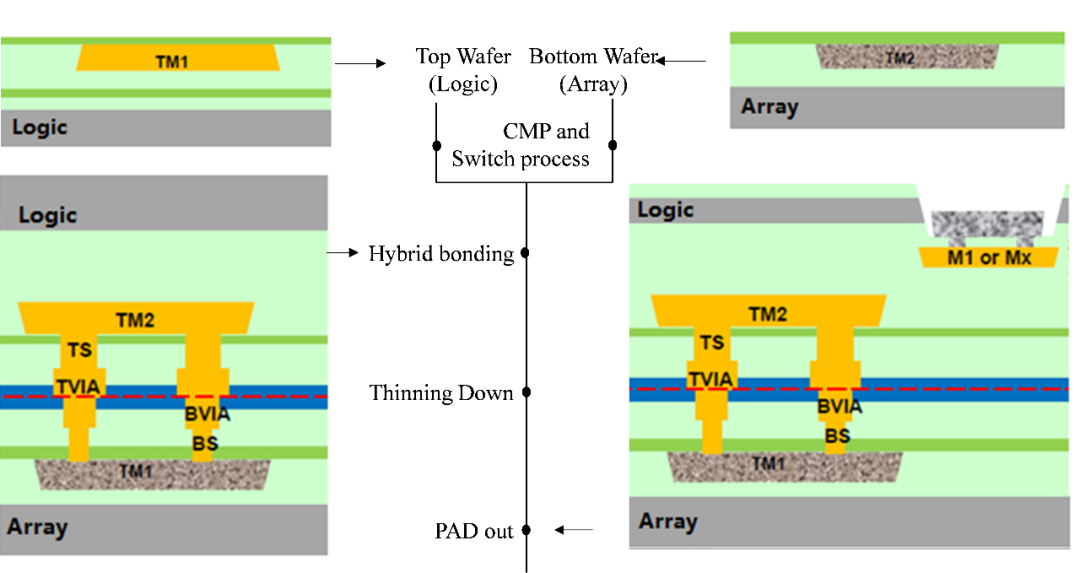

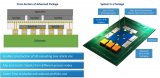

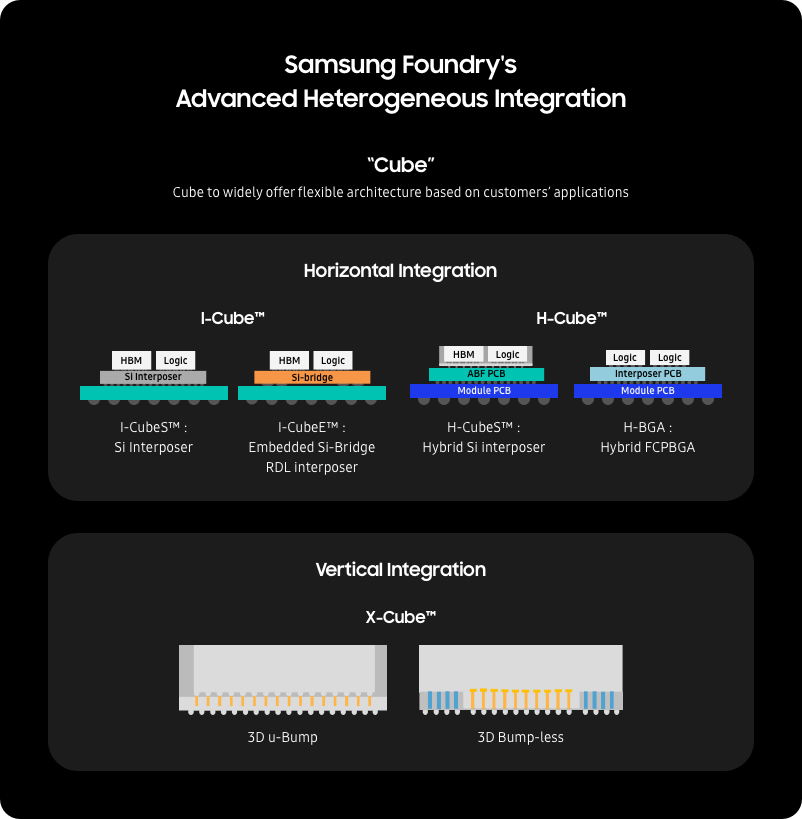

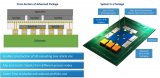

1419 ,絕大多數(shù)廠商會(huì)選擇異構(gòu)集成的方式,借助先進(jìn)封裝技術(shù)實(shí)現(xiàn)“超越摩爾”。諸如臺(tái)積電、英特爾等廠商,也都紛紛推出了3DFabric、Foveros之類的技術(shù),而三星也不甘落后,一并追求突破半導(dǎo)體技術(shù)的極限。 ? 為了進(jìn)一步發(fā)揮其先進(jìn)封裝技術(shù)

2023-11-21 00:13:00 1155

1155

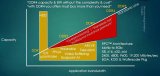

DRAM產(chǎn)能再大,也難以滿足全球龐大的市場需求。因此,應(yīng)該是技術(shù)層面的原因。技術(shù)才是高科技產(chǎn)業(yè)的核心競爭力。3D Flash目前技術(shù)在96層,但是技術(shù)路標(biāo)的能見度已至512層-3D Flash做為

2018-10-12 14:46:09

理,相比之下在SRAM存儲(chǔ)芯片上一個(gè)bit通常需要六個(gè)晶體管。因此DRAM擁有非常高的密度,單位體積的容量較高因此成本較低。 DRAM存儲(chǔ)原理 DRAM的每一位存儲(chǔ)單元采用一個(gè)晶體管和小電容來實(shí)現(xiàn)

2020-12-10 15:49:11

一種特定的類型:DRAM。DRAM(動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)是一種基于充電電容器的存儲(chǔ)技術(shù),實(shí)現(xiàn)起來非常快且便宜。它還允許高密度。但是DRAM并非沒有缺陷。DRAM中的一位可以存儲(chǔ)為電容器上是否存在電荷

2020-09-25 08:01:20

邏輯電路的糾錯(cuò)技術(shù)是如何實(shí)現(xiàn)的?糾錯(cuò)技術(shù)在邏輯電路中有什么作用?

2021-06-18 09:50:31

偏硬件:接口電路中的門組合電路;偏軟件:算法、接口控制器實(shí)現(xiàn)中的狀態(tài)機(jī)群或時(shí)序電路。隨著邏輯設(shè)計(jì)的深入,復(fù)雜功能設(shè)計(jì)一般基于同步時(shí)序電路方式。此時(shí),邏輯設(shè)計(jì)基本上就是在設(shè)計(jì)狀態(tài)機(jī)群或計(jì)數(shù)器等時(shí)序電路

2021-11-10 06:39:25

集成邏輯電路、組合邏輯電路實(shí)驗(yàn)?zāi)康?. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態(tài)門的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計(jì)和實(shí)現(xiàn)方法

2008-12-11 23:36:32

建設(shè)推動(dòng)共性、關(guān)鍵性、基礎(chǔ)性核心領(lǐng)域的整體突破,促進(jìn)我國軟件集成電路產(chǎn)業(yè)持續(xù)快速發(fā)展,由國家集成電路封測產(chǎn)業(yè)鏈技術(shù)創(chuàng)新戰(zhàn)略聯(lián)盟、深圳市半導(dǎo)體行業(yè)協(xié)會(huì)主辦,上海樂麩教育科技有限公司、中科院深圳先進(jìn)技術(shù)

2016-03-21 10:39:20

。第一個(gè)集成電路只有少數(shù)幾個(gè)器件,可能多達(dá)十個(gè)二極管,晶體管,電阻器和電容器,使得在單個(gè)器件上制造一個(gè)或多個(gè)邏輯門成為可能。至于增加每個(gè)集成電路的組件(或晶體管)數(shù)量,該技術(shù)的發(fā)展如下:小規(guī)模集成該技術(shù)

2022-03-31 10:46:06

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-18 07:33:04

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-27 08:01:28

業(yè)者猜測是DRAM技術(shù)的大革新。當(dāng)然,DRAM市場上還有一個(gè)不可小覷的力量——中國DRAM廠商,他們在這幾年來的成長越來越快,對全球市場的影響也與日俱增。據(jù)估計(jì),中國品牌約占DRAM市場的40%和閃存

2018-10-18 17:05:17

Imagination全新BXS GPU助力德州儀器汽車處理器系列產(chǎn)品實(shí)現(xiàn)先進(jìn)圖形處理功能

2020-12-16 07:04:43

的時(shí)鐘周期傳輸?shù)刂窋?shù)據(jù)。這樣就可以節(jié)省一半的針腳實(shí)現(xiàn)和SRAM的同樣功能,這種技術(shù)即多路技術(shù)(multiplexing)。可以完成同16K SRAM一樣的工作。DRAM減少地址引腳的主要原因是以下幾個(gè)

2010-07-15 11:40:15

可編程邏輯器件市場約為35億美元。固定邏輯器件市場約為120億美元。然而,近年來,PLD銷售額的增長速度已經(jīng)超過基于傳統(tǒng)門陣列技術(shù)的固定邏輯器件的銷售增長速度。而且,高性能FPGA現(xiàn)在已開始從采用最先進(jìn)

2009-05-29 11:36:21

電話網(wǎng)已有PBX的情況下,得到一個(gè)針對多種計(jì)算機(jī)電話集成技術(shù)業(yè)務(wù)的統(tǒng)一平臺(tái)。但是統(tǒng)一設(shè)計(jì)出開發(fā)計(jì)算機(jī)電話集成技術(shù)業(yè)務(wù)的平臺(tái),以便通過集成已有產(chǎn)品來保證用戶的投資,實(shí)現(xiàn)起來卻遠(yuǎn)非易事,其原因主要有兩個(gè)方面,一是技術(shù), 二是業(yè)務(wù)。

2019-09-10 10:42:17

智能電路是以物理電路為基礎(chǔ),集成了先進(jìn)的傳感量測技術(shù)、網(wǎng)絡(luò)技術(shù)、通信技術(shù)、分析決策技術(shù)、自動(dòng)控制技術(shù)與能源動(dòng)力技術(shù)的新型現(xiàn)代化電路。智能電路具有堅(jiān)強(qiáng)、自愈、兼容、經(jīng)濟(jì)、集成和優(yōu)化等特征,能夠實(shí)現(xiàn)

2020-04-22 07:36:18

電機(jī)對能耗的貢獻(xiàn)率在美國接近50%,因此降低電機(jī)能耗能有效地提高能源利用率,而采用先進(jìn)的微控制器(MCU)技術(shù)來實(shí)現(xiàn)電機(jī)控制是一種有效的方法。本文介紹了最新的電機(jī)控制MCU技術(shù)發(fā)展及其

2011-07-27 09:42:29

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見的接口電路的時(shí)序電路可以通過FPGA實(shí)現(xiàn),通過這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細(xì)闡述

2019-06-19 07:42:37

介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進(jìn)行直接數(shù)字頻率合成的VHDL源程序。

2021-04-30 06:29:00

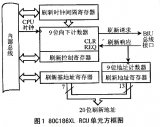

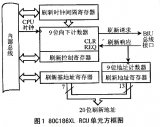

摘要:介紹怎樣在嵌入式CPU 80C186XL DRAM刷新控制單元的基礎(chǔ)上,利用CPLD技術(shù)和80C196XL的時(shí)序特征設(shè)計(jì)一個(gè)低價(jià)格、功能完整的DRAM控制器的方法,并采用VHDL語言編程實(shí)現(xiàn)

2011-02-24 09:33:15

您是否曾想在您的FPGA設(shè)計(jì)中使用先進(jìn)的視頻壓縮技術(shù),卻發(fā)現(xiàn)實(shí)現(xiàn)起來太過復(fù)雜?那么如何滿足視頻壓縮的需求?

2021-04-08 06:43:18

你好團(tuán)隊(duì)。有一些工具可以通過sparc了解intel homologos處理器。特別是m6謝謝你以上來自于谷歌翻譯以下為原文Hello team.There is some tool to know

2018-11-06 11:21:05

愛特梅爾公司 (Atmel? Corporation) 發(fā)布用于太空應(yīng)用的全新抗輻射SPARC? 處理器,在整個(gè)溫度和電壓范圍內(nèi),AT697之F版本在100 MHz 時(shí)達(dá)到90 MIPs性能,功耗僅為0.7W。

2019-08-28 08:02:21

機(jī)器人學(xué)代表了當(dāng)今集成度高、具有代表性的高技術(shù)領(lǐng)域,它綜合了多門學(xué)科。其中包括機(jī)械工程學(xué)、計(jì)算機(jī)技術(shù)、控制工程學(xué)、電子學(xué)、生物學(xué)等多學(xué)科的交叉與融合,體現(xiàn)了當(dāng)今實(shí)用科學(xué)技術(shù)的先進(jìn)水平。

2020-05-12 08:24:18

`哪位了解LCVD激光氣相沉積設(shè)備,想買一臺(tái)用來做補(bǔ)線用。如圖,沉積出寬10um左右的金屬線。求大神指點(diǎn)!`

2014-01-17 10:36:02

本文介紹了怎樣在嵌入式CPU 80C186XL DRAM刷新控制單元的基礎(chǔ)上,利用CPLD技術(shù)和80C196XL的時(shí)序特征設(shè)計(jì)一個(gè)低價(jià)格、功能完整的DRAM控制器的方法,并采用VHDL語言編程實(shí)現(xiàn)。

2021-04-28 07:10:38

模式也使得DRAM的集成度高于SRAM,一個(gè)DRAM的存儲(chǔ)單元僅需要一個(gè)晶體管和一個(gè)小電容,而每個(gè)SRAM單元需要四道六個(gè)晶體管和其它的零件,故DRAM在大容量以及價(jià)格上會(huì)有優(yōu)勢。 FlashFLASH

2019-09-18 09:05:09

。圖3 刮刀只有臺(tái)階的鋼網(wǎng)設(shè)計(jì)示意圖 (2)自動(dòng)點(diǎn)錫膏 自動(dòng)點(diǎn)錫膏(如圖4所示)成功地為通孔和異形組件沉積體積正確的錫膏,它提供了網(wǎng)板印刷可能無 法實(shí)現(xiàn)的大量錫膏沉積的靈活性和能力。現(xiàn)今,自動(dòng)點(diǎn)膠

2018-11-22 11:01:02

一種基于FPGA技術(shù)的虛擬邏輯分析儀的研究與實(shí)現(xiàn):邏輯分析儀的現(xiàn)狀" 發(fā)展趨勢及研制虛擬邏輯分析儀的必要性, 論述了基于FPGA技術(shù)的虛擬邏輯分析儀的設(shè)計(jì)方案及具體實(shí)現(xiàn)方法,介紹

2008-11-27 13:13:04 29

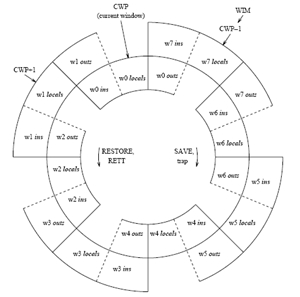

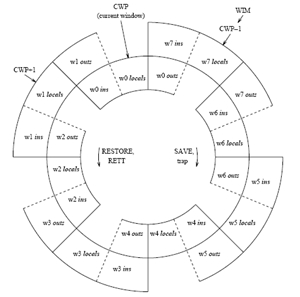

29 窗口寄存器作為SPARC 結(jié)構(gòu)中一個(gè)重要的概念在進(jìn)行基于SPARC 結(jié)構(gòu)的嵌入式實(shí)時(shí)系統(tǒng)移植時(shí),需要在任務(wù)切換函數(shù)中進(jìn)行與其相關(guān)的處理。本文簡單介紹了SPARC 的棧結(jié)構(gòu)、寄存器窗

2009-08-05 16:19:40 20

20 集成邏輯部件:本章主要分析和討論完成數(shù)字邏輯電路各種功能的基本邏輯部件——門電路的外特性及基本結(jié)構(gòu)。首先介紹目前廣泛應(yīng)用的TTL集成邏輯門電路,然后討論MOS集成邏輯電

2009-09-01 09:05:12 0

0 集成邏輯門電路邏輯功能的測試

一、實(shí)驗(yàn)?zāi)康?

2009-03-28 09:49:44 12285

12285

什么是SPARC處理器 1

2009-12-17 10:40:49 934

934 SPARC是一個(gè)開放的體系結(jié)構(gòu)標(biāo)準(zhǔn),它基于80年代加州大學(xué)伯克利分校對RISC微處理器的研究成果,現(xiàn)在已成為國際上流行的RISC微處理器體系架構(gòu)之一。本文介紹了SPARC微處理器的發(fā)展歷

2010-06-23 11:33:18 2399

2399

DRAM廠不堪虧損紛降低生產(chǎn)供給過剩的標(biāo)準(zhǔn)型DRAM,IC設(shè)計(jì)業(yè)也跟進(jìn),鈺創(chuàng)(5351)董事長暨執(zhí)行長盧超群昨表示,該公司正積極降低DRAM營收比重,朝開發(fā)整合邏輯IC的特殊DRAM產(chǎn)品發(fā)展;他認(rèn)為

2011-11-25 09:50:08 570

570 Mouser Electronics宣布在Mouser.com上推出其最新的技術(shù)網(wǎng)站,專注于可編程邏輯技術(shù)。 該全新網(wǎng)站有助于工程師了解有關(guān)不同類型可編程邏輯技術(shù)的更多信息和識(shí)別適用于特定應(yīng)用的理想元器件。

2013-06-14 10:53:57 843

843 實(shí)現(xiàn)在車內(nèi)集成和管理多種先進(jìn)無線技術(shù)。我們非常高興發(fā)布這一平臺(tái),在未來的汽車設(shè)計(jì)中提供最佳的先進(jìn)連接解決方案和服務(wù)。”

2016-06-13 09:45:54 782

782 基于SPARC的VxWorks異常處理研究_黃江泉

2017-03-17 08:00:00 1

1 邏輯門是數(shù)字電路的基礎(chǔ)。各種多姿多彩的邏輯門組合在一起,形成了數(shù)字電路的大千世界。實(shí)際上,邏輯門反映的是邏輯代數(shù)的幾種基本運(yùn)算,只要你能夠實(shí)現(xiàn)這樣的邏輯代數(shù)規(guī)則,你就能夠用其他設(shè)備來實(shí)現(xiàn)邏輯門的功能。

2017-09-19 14:19:18 23

23 的處理器具有指令系統(tǒng)簡單、采用硬布線控制邏輯、處理能力強(qiáng)、速度快、可靠性高等特點(diǎn),基于這些特點(diǎn),SPARC結(jié)構(gòu)處理器現(xiàn)在被廣泛地應(yīng)用于UNIX工作站、服務(wù)器等穩(wěn)定性要求很高的環(huán)境中。隨著SPARC V8

2017-10-31 15:40:42 1

1 SPARC(Scalable Processor ARChitecture)可擴(kuò)展處理器架構(gòu)是SUN公司在1985年提出的體系結(jié)構(gòu)標(biāo)準(zhǔn),它基于1980年到1982年間加州大學(xué)伯克利分校關(guān)于

2017-11-01 16:18:33 3

3 據(jù)報(bào)道,中國存儲(chǔ)產(chǎn)業(yè)正在急速的崛起,如今紫光國芯更是一大主力軍,據(jù)悉紫光國芯的DRAM芯片設(shè)計(jì)技術(shù)已經(jīng)是處于世界先進(jìn)水平,但是產(chǎn)量很小,市場份額還有待提升。

2018-01-23 11:31:43 2255

2255 合肥睿力集成電路,此前曾名合肥長鑫,這是中國的一家DRAM初創(chuàng)企業(yè),稱今年年底將完成前端設(shè)備組裝,并在2018年2月實(shí)現(xiàn)19nm DRAM量產(chǎn)。

2018-06-11 16:27:00 29316

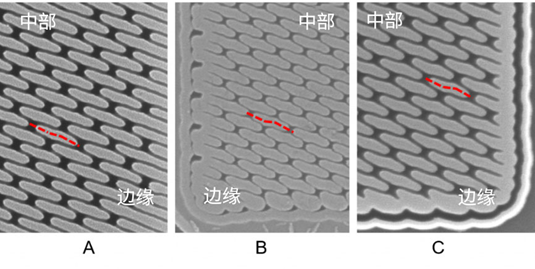

29316 出愈來愈廣泛的應(yīng)用。 高k閘極介電質(zhì)及金屬閘極的ALD沉積對于先進(jìn)邏輯晶片已成為標(biāo)準(zhǔn),并且該技術(shù)正用于沉積間隔定義的雙倍暨四倍光刻圖樣(SDDP、SDQP),用以推廣傳統(tǒng)浸潤式微影的使用以界定高密度邏輯暨記憶體設(shè)計(jì)的最小特征尺寸。

2018-02-13 03:16:00 25903

25903 本文主要圍繞DRAM、邏輯器件和NAND這三大尖端產(chǎn)品來進(jìn)行詳細(xì)介紹。

2018-04-21 08:19:00 11965

11965

E 系列能夠幫助存儲(chǔ)器芯片制造商應(yīng)對當(dāng)前所面臨的諸多關(guān)鍵挑戰(zhàn),從而推動(dòng)3D NAND 及 DRAM 器件尺寸持續(xù)縮小。這一基于泛林業(yè)界領(lǐng)先的存儲(chǔ)器制造產(chǎn)品組合的全新系統(tǒng)正逐步吸引全球市場的關(guān)注,在推出后已被全球主要3D NAND和DRAM生產(chǎn)商投入使用,并且被用于許多新技術(shù)和產(chǎn)品的研發(fā)。

2018-05-24 17:19:00 2398

2398 如果微處理器狀態(tài)信號(hào)無效,這個(gè)狀態(tài)則是一個(gè)T4狀態(tài),狀態(tài)機(jī)B從B1轉(zhuǎn)到B2.如果狀態(tài)是一個(gè)T4狀態(tài),并且RAS有效(DRAM訪問),則RAST4狀態(tài),并且RAS有效(DRAM訪問),則RAS邏輯

2018-08-18 09:25:03 814

814

DRAM在過去的幾十年里發(fā)展方向單一,以追求高密度存儲(chǔ)器為目標(biāo),但臺(tái)灣的鈺創(chuàng)科技沒有走傳統(tǒng)路線,而是開發(fā)全新的DRAM架構(gòu),稱為RPC (Reduced Pin Count) DRAM。

2019-02-11 09:16:11 4217

4217

繼臺(tái)積電、三星晶圓代工、英特爾等國際大廠在先進(jìn)邏輯制程導(dǎo)入極紫外光(EUV)微影技術(shù)后,同樣面臨制程微縮難度不斷增高的DRAM廠也開始評估采用EUV技術(shù)量產(chǎn)。三星電子今年第四季將開始利用EUV技術(shù)生產(chǎn)1z納米DRAM,SK海力士及美光預(yù)期會(huì)在1α納米或1β納米評估導(dǎo)入EUV技術(shù)。

2019-06-18 17:20:31 2438

2438 DRAM廠商在面對DRAM價(jià)格不斷下跌的困境下,已經(jīng)在考慮導(dǎo)入EUV技術(shù)用于制造DRAM,主要目的是為了降低成本。

2019-06-21 09:10:01 2047

2047 作為中國DRAM產(chǎn)業(yè)的領(lǐng)導(dǎo)者,長鑫存儲(chǔ)正在加速從DRAM的技術(shù)追趕者向技術(shù)引領(lǐng)者轉(zhuǎn)變,用自主研發(fā)的DRAM技術(shù)和專利,引領(lǐng)中國實(shí)現(xiàn)DRAM零的突破。

2019-09-19 10:26:00 463

463 sparc體系架構(gòu)的窗口寄存器的深入理解 1.概述 2.窗口寄存器的特性 3.程序的設(shè)計(jì) 4.sparc設(shè)計(jì)對于嵌入式編程的優(yōu)劣 1.概述 sparc這種架構(gòu)有著特殊的窗口寄存器,使用sparc芯片

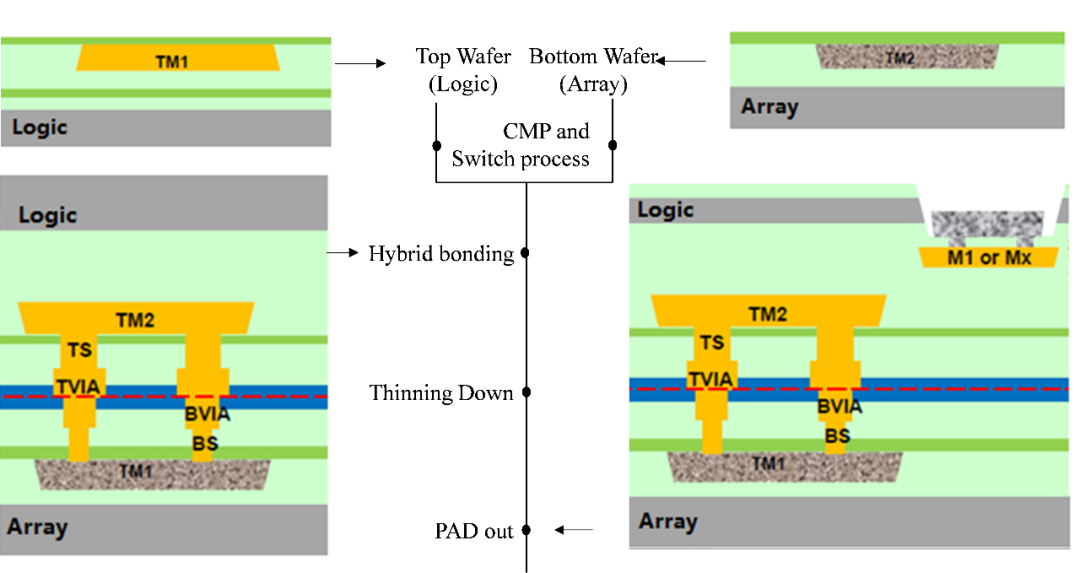

2021-01-07 10:39:59 3200

3200 /b能效接口的異質(zhì)集成嵌入式LPDDR4/LPDDR4X DRAM》(A Stacked Embedded DRAM Array for LPDDR4/4Xusing Hybrid Bonding 3D

2021-01-26 16:00:14 5546

5546

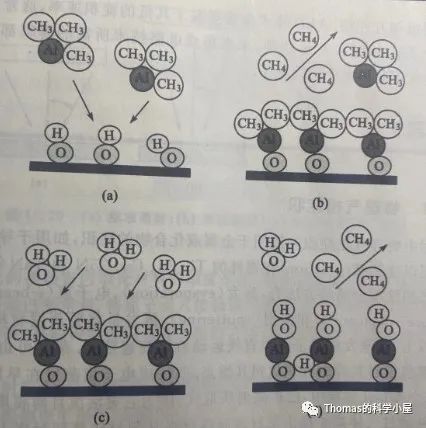

說明:若有考慮不周,歡迎留言指正。 原子層沉積在半導(dǎo)體先進(jìn)制程的應(yīng)用 隨著集成電路工藝技術(shù)的不斷提高,晶體管的特征尺寸及刻蝕溝槽不斷減小,溝槽及其側(cè)壁的鍍膜技術(shù)面臨嚴(yán)峻的挑戰(zhàn),物理氣相沉積(PVD

2021-04-17 09:43:21 16607

16607

MICRON最近宣布,我們正在發(fā)貨使用全球最先進(jìn)的DRAM工藝制造的存儲(chǔ)芯片。這個(gè)過程被神秘地稱為“1α”(1-alpha)。這是什么意思,有多神奇?

2021-09-15 17:00:52 1862

1862 Fraunhofer ISIT的PowderMEMS是一項(xiàng)新研發(fā)的創(chuàng)新技術(shù),用于在晶圓級(jí)上從多種材料中創(chuàng)建三維微結(jié)構(gòu)。該技術(shù)基于通過原子層沉積(ALD)工藝在空腔中將微米級(jí)粉末顆粒粘合在一起。

2022-03-17 09:46:23 2011

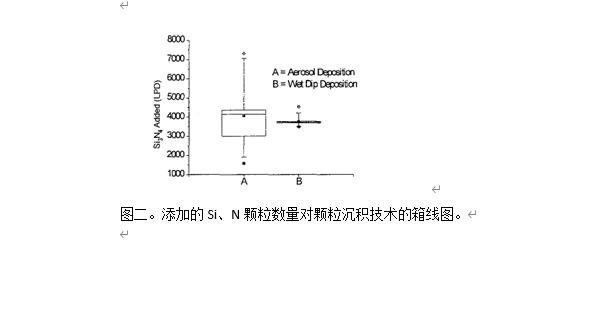

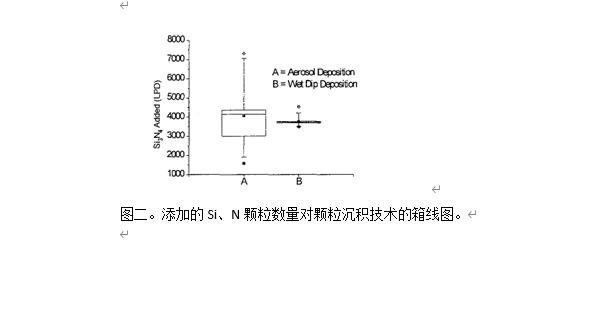

2011 評估各種清洗技術(shù)的典型方法是在晶片表面沉積氮化硅(Si,N4)顆粒,然后通過所需的清洗工藝處理晶片。國家半導(dǎo)體技術(shù)路線圖規(guī)定了從硅片上去除顆粒百分比的標(biāo)準(zhǔn)挑戰(zhàn),該挑戰(zhàn)基于添加到硅片上的“>

2022-05-25 17:11:38 1242

1242

在DRAM結(jié)構(gòu)中,電容存儲(chǔ)單元的充放電過程直接受晶體管所控制。隨著晶體管尺寸縮小接近物理極限,制造變量和微負(fù)載效應(yīng)正逐漸成為限制DRAM性能(和良率)的主要因素。而對于先進(jìn)的DRAM,晶體管的有源

2022-08-01 10:22:26 709

709

在一起。然而,隨著芯片特征變得更小,現(xiàn)有材料可能無法在所需厚度下實(shí)現(xiàn)相同性能,從而可能需要新的材料。 泛林集團(tuán)發(fā)明了一種名為 SPARC 的全新沉積技術(shù),用于制造具有改進(jìn)電絕緣性能的新型碳化硅薄膜。重要的是,它可以沉積超薄層,

2022-10-14 17:12:59 505

505

有限公司,納斯達(dá)克股票代碼:MU)今日宣布,其采用全球最先進(jìn)技術(shù)節(jié)點(diǎn)的1β DRAM產(chǎn)品已開始向部分智能手機(jī)制造商和芯片平臺(tái)合作伙伴送樣以進(jìn)行驗(yàn)證,并做好了量產(chǎn)準(zhǔn)備。美光率先在低功耗LPDDR5X移動(dòng)內(nèi)存上采用該新一代制程技術(shù),其最高速率可達(dá)每秒8.5Gb。該節(jié)點(diǎn)在性能、密度和能效方面都有

2022-11-02 11:31:27 494

494

2022 年?11 月?2 日;內(nèi)存與存儲(chǔ)解決方案領(lǐng)先供應(yīng)商 Micron Technology Inc.(美光科技股份有限公司,納斯達(dá)克股票代碼:MU)今日宣布,其采用全球最先進(jìn)技術(shù)節(jié)點(diǎn)

2022-11-02 11:50:51 578

578 2022年11月2日——中國上海——內(nèi)存與存儲(chǔ)解決方案領(lǐng)先供應(yīng)商 Micron Technology Inc.(美光科技股份有限公司,納斯達(dá)克股票代碼:MU)今日宣布,其采用全球最先進(jìn)技術(shù)節(jié)點(diǎn)

2022-11-02 17:27:48 724

724 以往,具備低漏電、高性能特性的先進(jìn)制程工藝多用于邏輯芯片,特別是PC、服務(wù)器和智能手機(jī)用CPU,如今,這些工藝開始在以DRAM為代表的存儲(chǔ)器中應(yīng)用,再加上EUV等先進(jìn)設(shè)備和工藝的“互通”,邏輯芯片和存儲(chǔ)器的制程節(jié)點(diǎn)和制造工藝越來越相近。

2022-11-17 11:10:08 1563

1563 電子發(fā) 燒友網(wǎng)報(bào)道(文/ 周凱揚(yáng) )軍事和特種工業(yè)裝備對于設(shè)備的要求往往較為獨(dú)特,尤其是在航空航天領(lǐng)域。在過去的航天設(shè)備電子系統(tǒng)中,SPARC架構(gòu)的處理器因?yàn)槠涓呖煽啃垣@得了青睞,以至于目前大部分

2022-12-21 07:30:05 768

768 內(nèi)存與存儲(chǔ)解決方案領(lǐng)先供應(yīng)商美光科技(Micron Technology Inc.)宣布,其采用全球最先進(jìn)技術(shù)節(jié)點(diǎn)的1βDRAM產(chǎn)品已開始向部分智能手機(jī)制造商和芯片平臺(tái)合作伙伴送樣以進(jìn)行驗(yàn)證,并做好了量產(chǎn)準(zhǔn)備。

2023-02-01 16:13:05 1914

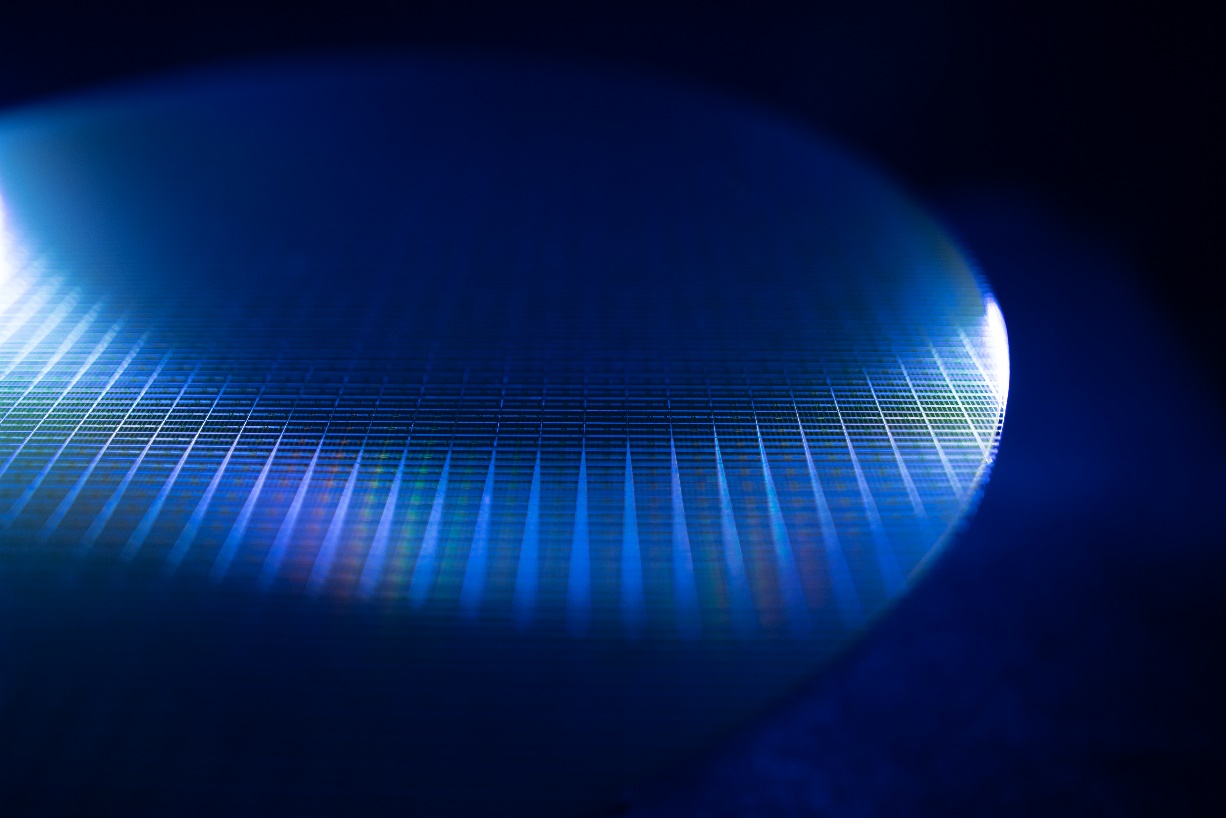

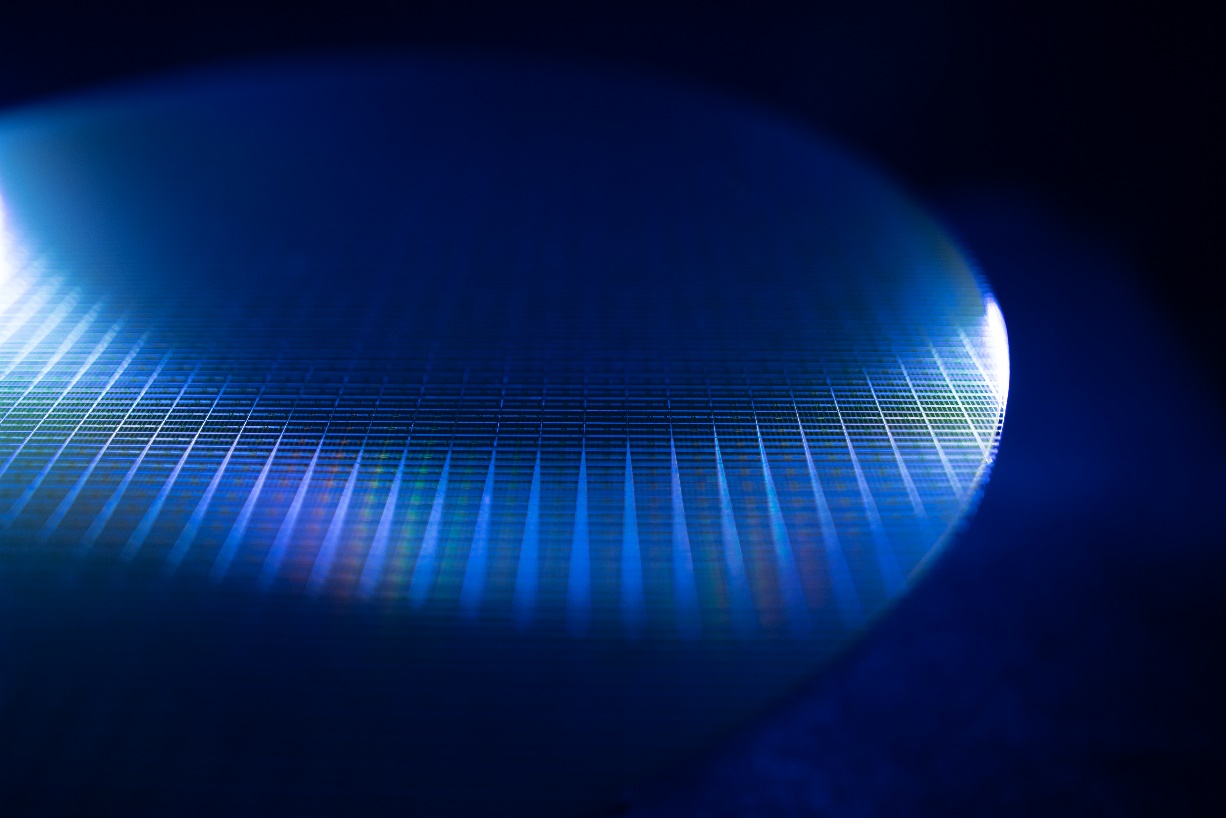

1914 薄膜沉積是晶圓制造的三大核心步驟之- - ,薄膜的技術(shù)參數(shù)直接影響芯片性能。

半導(dǎo)體器件的不斷縮小對薄膜沉積工藝提出了更高要求,而ALD技術(shù)憑借沉積薄膜厚度的高度可控性、優(yōu)異的均勻性和三E維保形性,在半導(dǎo)體先進(jìn)制程應(yīng)用領(lǐng)域彰顯優(yōu)勢。

2023-02-16 14:36:54 555

555 ALD技術(shù)是一種將物質(zhì)以單原子膜的形式逐層鍍在基底表面的方法,能夠實(shí)現(xiàn)納米量級(jí)超薄膜的沉積。

2023-04-25 16:01:05 2442

2442

。 PVD 沉積工藝在半導(dǎo)體制造中用于為各種邏輯器件和存儲(chǔ)器件制作超薄、超純金屬和過渡金屬氮化物薄膜。最常見的 PVD 應(yīng)用是鋁板和焊盤金屬化、鈦和氮化鈦襯墊層、阻擋層沉積和用于互連金屬化的銅阻擋層種子沉積。 PVD 薄膜沉積工藝需要一個(gè)高真空的平臺(tái),在

2023-05-26 16:36:51 1751

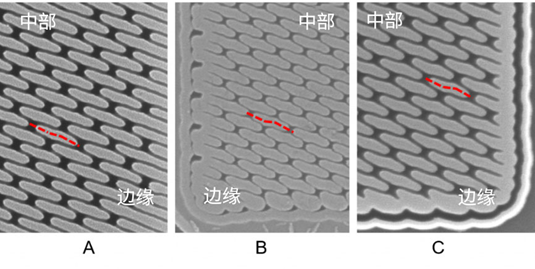

1751 中國科學(xué)院大學(xué)集成電路學(xué)院是國家首批支持建設(shè)的示范性微電子學(xué)院。為了提高學(xué)生對先進(jìn)光刻技術(shù)的理解,本學(xué)期集成電路學(xué)院開設(shè)了《集成電路先進(jìn)光刻技術(shù)與版圖設(shè)計(jì)優(yōu)化》研討課。在授課過程中,除教師系統(tǒng)地講授

2023-06-12 11:15:17 279

279

原子層沉積(Atomic layer deposition,ALD)是一種可以沉積單分子層薄膜的特殊的化學(xué)氣相沉積技術(shù)。

2023-06-15 16:19:21 2038

2038

芯片已經(jīng)無處不在:從手機(jī)和汽車到人工智能的云服務(wù)器,所有這些的每一次更新?lián)Q代都在變得更快速、更智能、更強(qiáng)大。

2023-07-12 11:19:31 352

352

薄膜沉積是指在基底上沉積特定材料形成薄膜,使之具有光學(xué)、電學(xué)等方面的特殊性能。

2023-07-13 09:10:48 7776

7776

TSV是2.5D和3D集成電路封裝技術(shù)中的關(guān)鍵實(shí)現(xiàn)技術(shù)。半導(dǎo)體行業(yè)一直在使用HBM技術(shù)將DRAM封裝在3DIC中。

2023-11-27 11:40:20 211

211

dram和nand的區(qū)別? DRAM和NAND是兩種不同類型的存儲(chǔ)器。DRAM(Dynamic Random Access Memory)是一種隨機(jī)存取存儲(chǔ)器,而NAND(Not AND)是一種邏輯

2023-12-08 10:32:00 3920

3920 共讀好書 魏紅軍 謝振民 (中國電子科技集團(tuán)公司第四十五研究所) 摘要: 電化學(xué)沉積技術(shù),作為集成電路制造的關(guān)鍵工藝技術(shù)之一,它是實(shí)現(xiàn)電氣互連的基石,主要應(yīng)用于集成電路制造的大馬士革銅互連電鍍工藝

2023-12-20 16:58:23 155

155

共讀好書 魏紅軍 謝振民 (中國電子科技集團(tuán)公司第四十五研究所) 摘要: 電化學(xué)沉積技術(shù),作為集成電路制造的關(guān)鍵工藝技術(shù)之一,它是實(shí)現(xiàn)電氣互連的基石,主要應(yīng)用于集成電路制造的大馬士革銅互連電鍍工藝

2023-12-11 17:31:18 234

234

先進(jìn)的封裝技術(shù)可以將多個(gè)半導(dǎo)體芯片和組件集成到高性能的系統(tǒng)中。隨著摩爾定律的縮小趨勢面臨極限,先進(jìn)封裝為持續(xù)改善計(jì)算性能、節(jié)能和功能提供了一條途徑。但是,與亞洲相比,美國目前在先進(jìn)封裝技術(shù)方面落后

2023-12-14 10:27:14 383

383

在太陽能電池的薄膜沉積工藝中,具有化學(xué)氣相沉積(CVD)與物理氣相沉積(PVD)兩種薄膜沉積方法,電池廠商在沉積工藝中也需要根據(jù)太陽能電池的具體問題進(jìn)行針對性選擇,并在完成薄膜沉積工藝后通過

2023-12-26 08:33:01 312

312

優(yōu)化硅的形態(tài)與沉積方式是半導(dǎo)體和MEMS工藝的關(guān)鍵,LPCVD和APCVD為常見的硅沉積技術(shù)。

2024-01-22 09:32:15 433

433

電子發(fā)燒友App

電子發(fā)燒友App

評論