本文主要圍繞DRAM、邏輯器件和NAND這三大尖端產(chǎn)品來進(jìn)行詳細(xì)介紹。

DRAM

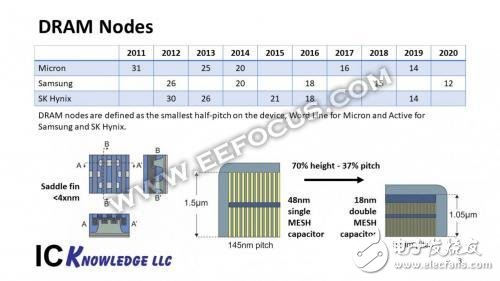

在DRAM章節(jié)的第一張幻燈片中,我按公司和年份呈現(xiàn)了DRAM工藝節(jié)點的變化。美光科技、三星和SK海力士是DRAM市場的主導(dǎo)廠商,所以我以這三家公司為代表展示了其各自的工藝節(jié)點。DRAM節(jié)點尺寸目前是由器件上最小的半間距來定義的,美光DRAM基于字線,三星和SK海力士則基于主動晶體管。

圖表下方在一定程度上展示了關(guān)鍵技術(shù)的發(fā)展情況。左側(cè)展示了具有掩埋字線的鞍形鰭片存取晶體管。具有掩埋字線的鞍形鰭片是目前存取晶體管的標(biāo)準(zhǔn)。在中間和右下角,顯示了DRAM電容器向更細(xì)節(jié)距-高長寬比結(jié)構(gòu)的演變。

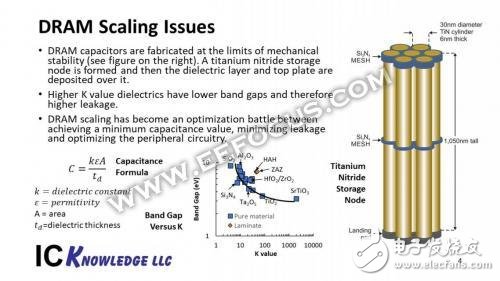

影響DRAM工藝縮減的主要問題是電容。為了可靠地存儲數(shù)據(jù),電容需要大于一定的閾值。要繼續(xù)制造出占用面積更小的電容,可以把電容做得更高,薄膜更薄,或者增加薄膜的K值。但是問題在于,雖然從機(jī)械穩(wěn)定性的角度還可以可靠地做出更高更薄的電容,但是隨著薄膜厚度的降低,漏電會增加,而且隨著薄膜K值的增加,帶隙減小也會導(dǎo)致漏電問題。當(dāng)前的標(biāo)準(zhǔn)是使用低漏電的鋁基氧化物薄膜和用于高k值的鋯基薄膜組成的復(fù)合膜,而且目前還不清楚是否還會有更好的替代方案。

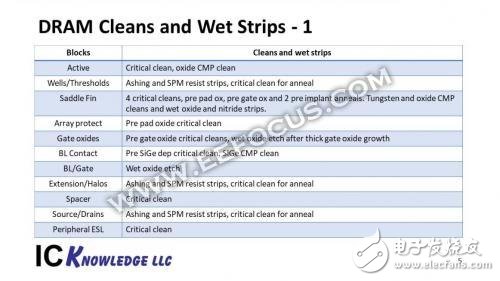

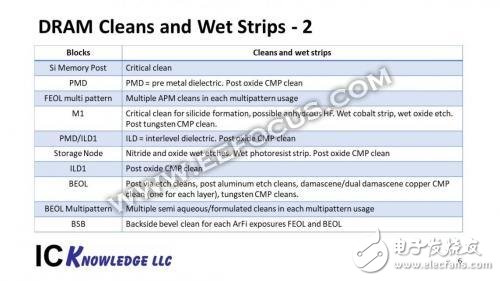

在第五張和第六張幻燈片中,我介紹了一些主要的DRAM工藝塊,并討論了DRAM工藝對清洗和濕條帶的需求。

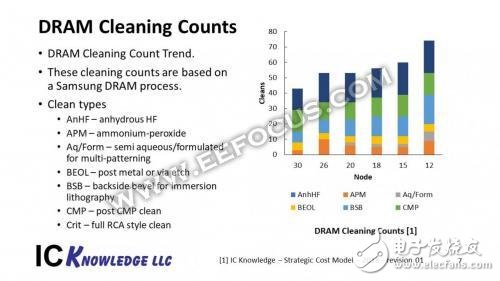

我在DRAM章節(jié)最后一張幻燈片中展示了三星工藝節(jié)點的清洗次數(shù)。可以看出,隨著工藝尺寸的縮減,DRAM清洗次數(shù)也在增加,這主要是因為在沉浸光刻步驟后需要進(jìn)行更多次背面斜面清潔,而且越來越復(fù)雜的多層圖案化方案也會造成多次清洗。

邏輯器件

在第八張幻燈片中,我介紹了格羅方德、英特爾、三星和臺積電的邏輯器件工藝節(jié)點。這四家廠商是邏輯器件工藝領(lǐng)域的領(lǐng)導(dǎo)廠商。應(yīng)當(dāng)特別指出的是,英特爾的節(jié)點通常等同于其他廠商下一代較小的工藝節(jié)點,比如英特爾的10nm和代工廠的7nm差不多。

幻燈片表格下方,左側(cè)顯示的是FinFET的橫截面,這是當(dāng)前先進(jìn)邏輯器件首選的工藝,右側(cè)顯示了納米線和納米片,預(yù)計將在4nm左右時替代FinFET。

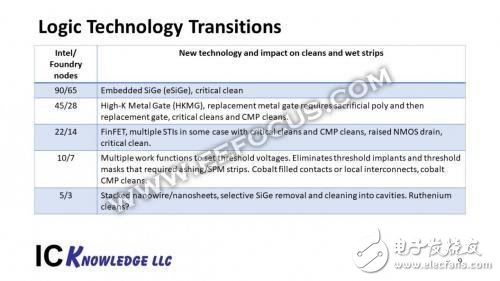

在幻燈片9中,我介紹了一些主要的邏輯器件工藝的演變。在這張幻燈片中,我以英特爾/代工廠的兩個數(shù)字展示工藝節(jié)點,如上所述,英特爾的工藝節(jié)點和代工廠較小尺寸的工藝節(jié)點類似。

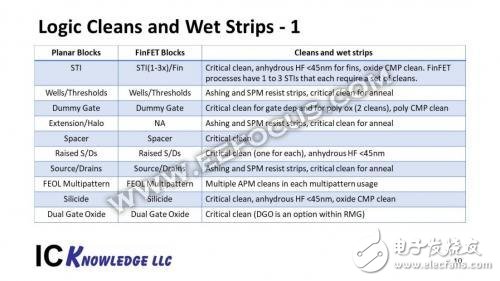

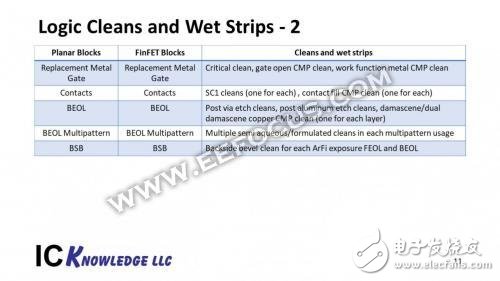

在第10張和第11張幻燈片中,我介紹了一些主要的邏輯工藝模塊,并討論了這些模塊對清洗和濕條帶的需求。

12號幻燈片是邏輯器件章節(jié)最后一張幻燈片,介紹了基于臺積電工藝節(jié)點的清洗步驟數(shù)量。當(dāng)工藝尺寸下降到第一代7nm工藝時,由于增加了掩膜層,再加上多重圖案化的復(fù)雜性,清洗次數(shù)一直在增加,在隨后的7nm+和5nm節(jié)點上,由于EUV將顯著降低光刻的復(fù)雜度,因此消除了許多清洗步驟。

NAND

3D NAND取代了2D NAND,成為NAND產(chǎn)品的技術(shù)選擇,現(xiàn)在3D NAND的比特出貨量也已經(jīng)超過了2D NAND。3D NAND尺寸的縮減是由層數(shù)進(jìn)行表征的,驅(qū)動力來自于層沉積和蝕刻取代了2D NAND中的光刻工藝。

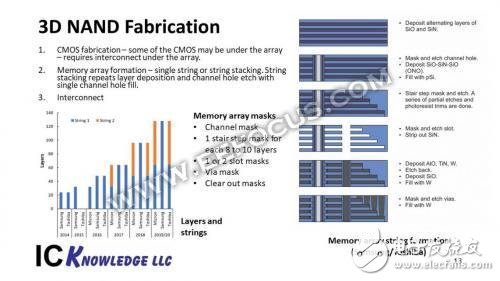

在第13張幻燈片中,我展示了3D NAND的三個主要制造步驟-CMOS制造、存儲陣列制造和互聯(lián)。三星和東芝(NAND產(chǎn)品的頭兩號供應(yīng)商)使用的基本存儲陣列工藝如右側(cè)圖所示。隨著層數(shù)的增加,存儲器陣列必須在“位串堆疊”階段拆分成多個段。左下圖顯示了三家領(lǐng)先供應(yīng)商的層數(shù)和位串。

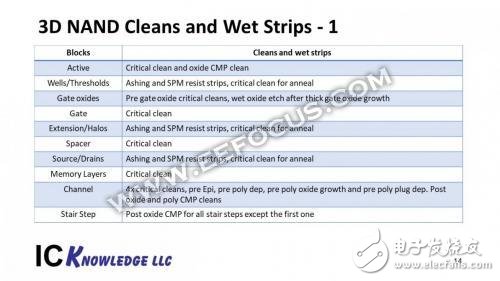

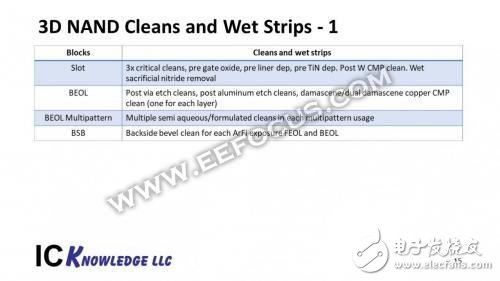

在第14張和第15張幻燈片中,我介紹了一些主要的3D NAND工藝模塊,并討論了這些模塊對清洗和濕條帶的需求。

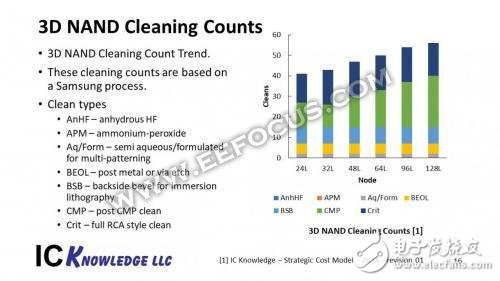

展示了3D NAND的總清洗次數(shù)與三星3D NAND工藝的層數(shù)。3D NAND清洗次數(shù)之所以隨著層數(shù)增加而增加,主要是因為階梯成型時的CMP清洗。在第一階梯掩模之后,每個后續(xù)掩模都需要在施加掩膜之前通過CMP清洗將層平坦化。

結(jié)論

DRAM工藝尺寸的縮減正在面臨基本的物理限制,目前還有沒有明確的解決方案,由于印刷需求的推動,DRAM的清洗復(fù)雜度也在增加。

隨著行業(yè)向5nm和3nm的推進(jìn),邏輯器件的工藝尺寸將持續(xù)縮減。納米線和納米片將對清洗帶來新的挑戰(zhàn)。隨著掩膜數(shù)量的則更加,以及多重圖案化方案越來越復(fù)雜,邏輯器件的清洗次數(shù)也在增長。

NAND工藝尺寸的縮減已經(jīng)完成落腳到了3D NAND層數(shù)的增加上。由于階梯成型需要CMP清洗,3D NAND器件的清洗次數(shù)也在不斷增加。

-

DRAM

+關(guān)注

關(guān)注

40文章

2326瀏覽量

183870 -

NAND

+關(guān)注

關(guān)注

16文章

1692瀏覽量

136471 -

邏輯器件

+關(guān)注

關(guān)注

0文章

88瀏覽量

20156

發(fā)布評論請先 登錄

相關(guān)推薦

【半導(dǎo)體存儲】關(guān)于NAND Flash的一些小知識

安世半導(dǎo)體推出微型無引腳邏輯IC

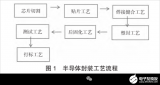

半導(dǎo)體行業(yè)工藝知識

一文看懂2025年功率半導(dǎo)體市場展望

一文解讀全球汽車半導(dǎo)體市場的未來發(fā)展

一文詳解半導(dǎo)體薄膜沉積工藝

功率半導(dǎo)體器件測試解決方案

半導(dǎo)體

閑談半導(dǎo)體封裝工藝工程師

半導(dǎo)體IC設(shè)計是什么?IC設(shè)計和芯片設(shè)計區(qū)別

一文看懂半導(dǎo)體工藝演進(jìn)對DRAM、邏輯器件、NAND的影響

一文看懂半導(dǎo)體工藝演進(jìn)對DRAM、邏輯器件、NAND的影響

評論