今天我們要介紹的時序分析基本概念是 wire load model . 中文名稱是線負載模型。是綜合階段用于估算互連線電阻電容的模型。

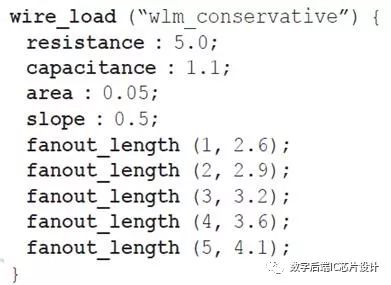

下圖就是一個比較常見的wire load model。該模型包含了互連線長度,電阻,電容,面積等信息。在綜合階段計算時序時,工具從lib文件中得到cell的延遲,而互連線的延遲則從線負載模型中的計算出來的RC信息得到。

怎么估算呢?我們來看上面這個例子,首先,我們通過線負載模型得到互連線的長度:假如我們需要知道一根扇出是6互連線的RC信息。

首先我們得知道互連線的長度,根據fanout_lenth的查找表:

互連線的長度 = 扇出5對應的互連線長度+(6-5)×slope(斜率)=4.1+0.5= 4.6

互連線電阻 = 互聯線長度 x 互聯線單位電阻值=4.6×5.0=23

互連線電容 = 互聯線長度 x 互聯線單位電容值=4.6×1.1=5.06

使用方法:

采用工藝庫lib1800中的wlm_conservative wire load model模型

set_wire_load_model -library lib1800 -name wlm_conservative

-

電容器

+關注

關注

64文章

6543瀏覽量

101880 -

電阻器

+關注

關注

21文章

4026瀏覽量

63247 -

時序分析

+關注

關注

2文章

127瀏覽量

22827 -

時序分析器

+關注

關注

0文章

24瀏覽量

5341

發布評論請先 登錄

IC設計基礎:說說wire load model

時序分析基本概念介紹<Operating Condition>

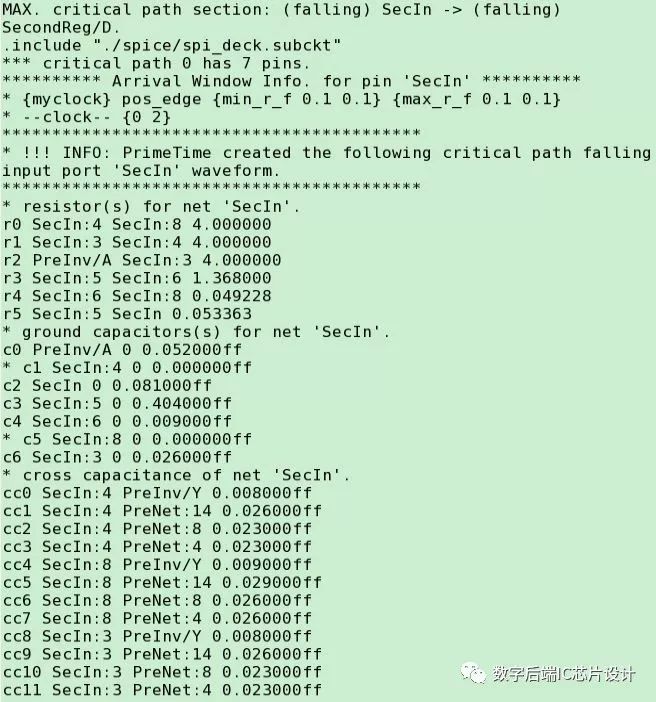

時序分析基本概念介紹&lt;spice deck&gt;

時序分析基本概念介紹&lt;generate clock&gt;

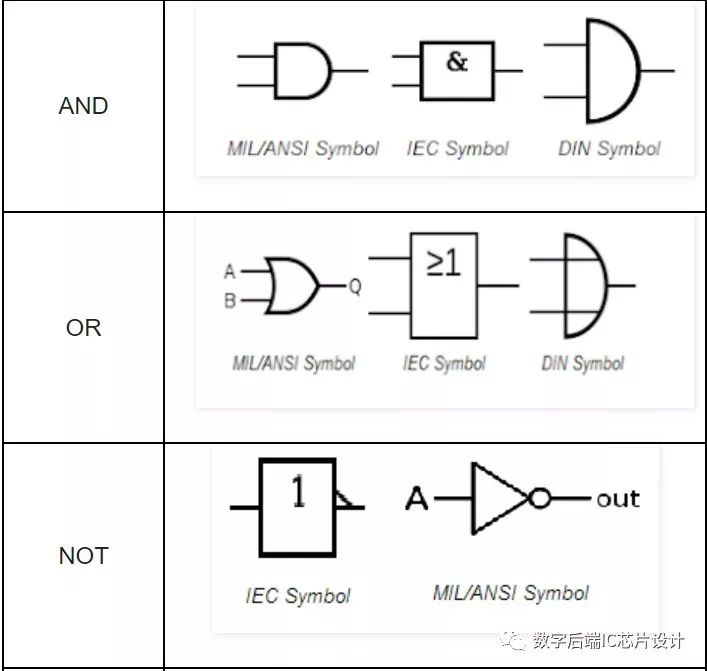

時序分析基本概念介紹&lt;Combinational logic&gt;

時序分析基本概念介紹<wire load model>

時序分析基本概念介紹<wire load model>

評論