Chiplet與異構(gòu)集成即將改變電子系統(tǒng)的設(shè)計(jì)、測(cè)試和制造方式。芯片行業(yè)的“先知”們相信這個(gè)未來(lái)是不可避免的。他們認(rèn)為,相比于最新的設(shè)計(jì)節(jié)點(diǎn),異構(gòu)、多chiplet的架構(gòu)可以降低成本和功耗。盡管這一預(yù)測(cè)得到了廣泛的接受,但問(wèn)題是,大家都準(zhǔn)備好了嗎?

前不久在舊金山的Semicon West上,Applied Materials舉行了異構(gòu)集成討論會(huì),由他們的半導(dǎo)體產(chǎn)品組的副總裁Vincent DiCaprio主持,討論了fabless芯片設(shè)計(jì)師、代工廠和生產(chǎn)設(shè)備公司開發(fā)的特定異構(gòu)集成策略。這場(chǎng)對(duì)話揭示出,在市場(chǎng)看到更廣泛的chiplet實(shí)現(xiàn)之前,還存在一些重大挑戰(zhàn)。

Chiplet的前景吸引了許多fabless公司,尤其是那些為高性能計(jì)算解決方案開發(fā)CPU和GPU的公司。然而,高昂的成本讓Qualcomm這樣重要的玩家望而怯步。異構(gòu)集成的一個(gè)大問(wèn)題是先進(jìn)的封裝技術(shù),wafer-to-wafer鍵合或die-to-wafer鍵合。

代工廠或是OSAT(outsourced semiconductor assembly and test),誰(shuí)來(lái)負(fù)責(zé)高級(jí)封裝技術(shù)是個(gè)大問(wèn)題。這兩方將何時(shí)開始合作,如何合作?最重要的是,由于缺乏計(jì)量工具,討論組的成員們紛紛表示,推動(dòng)chiplet的快速采用變得難以負(fù)擔(dān)。 小組討論包括AMD、Intel、Qualcomm、Besi和EV Group的代表。Besi是一家設(shè)計(jì)和制造半導(dǎo)體設(shè)備的荷蘭公司。總部位于奧地利的EV Group是晶圓鍵合和光刻設(shè)備供應(yīng)商。

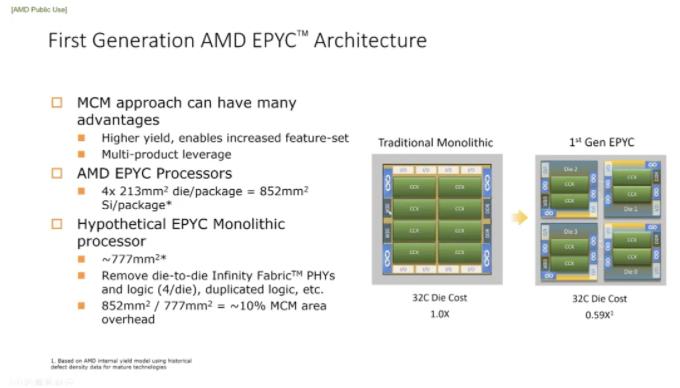

AMD:異構(gòu)集成的早期采用者

AMD是異構(gòu)集成的早期采用者。AMD的技術(shù)和產(chǎn)品工程高級(jí)副總裁Mark Fuselier將其描述為“跨越過(guò)去十年的旅程”。通過(guò)“將SoC解構(gòu)成多個(gè)片段,然后在封裝中重新組合起來(lái)”,AMD首先在數(shù)據(jù)中心設(shè)計(jì)了基于Zen的CPU。

但是,“當(dāng)我們開始熟悉chiplet時(shí),我們發(fā)現(xiàn)其中有更多的機(jī)會(huì)。”AMD的異構(gòu)集成第二代是“將內(nèi)存更靠近邏輯部分”。首先是在圖形空間中使用了HBM(high bandwidth memory)。Fuselier稱之為AMD的“一個(gè)轉(zhuǎn)折點(diǎn)”,他解釋說(shuō)最近正在讓SRAM更靠近CPU。

他指出,第三代更加令人興奮。AMD看到其未來(lái)在于“實(shí)現(xiàn)真正的異構(gòu)集成,優(yōu)化chiplet以適應(yīng)CPU或GPU計(jì)算。”它已經(jīng)成為了“一個(gè)架構(gòu)師的夢(mèng)想,能夠優(yōu)化每一個(gè)計(jì)算空間中的工作負(fù)載。”

Qualcomm:移動(dòng)領(lǐng)域中的chiplet?

當(dāng)AMD利用異構(gòu)集成服務(wù)于客戶端和數(shù)據(jù)中心時(shí),Qualcomm在移動(dòng)領(lǐng)域的定位又在哪里呢?

Qualcomm的副總裁兼研究員Chidambaram指出,“Qualcomm要想在智能手機(jī)市場(chǎng)上繼續(xù)生產(chǎn)更具競(jìng)爭(zhēng)力的超大批量產(chǎn)品,我們需要超越摩爾定律的創(chuàng)新。”

他說(shuō):“五年前,我知道GAA將是2022年的技術(shù)。但是從現(xiàn)在起五年后,我不確定我們會(huì)做什么。”他強(qiáng)調(diào),Qualcomm看到自己“走在橫軸和縱軸之間的二維空間里”,其中“吞吐量成為一個(gè)關(guān)鍵向量,而不是規(guī)模”。

盡管Qualcomm對(duì)chiplet思考很多,但Chidambaram表示,由于chiplet無(wú)法滿足Qualcomm的成本要求,所以還沒有相關(guān)產(chǎn)品。

盡管如此,隨著市場(chǎng)從5G轉(zhuǎn)向6G,Qualcomm看到了chiplet的潛力。他解釋說(shuō),從整體上看,一個(gè)系統(tǒng)有大量的射頻、電源管理和內(nèi)存。Chidambaram說(shuō):“插入損耗很大,功率放大器的性能必須非常接近系統(tǒng)芯片的其他部分。異構(gòu)集成成為將所有這些整合在一起的關(guān)鍵。”

智能手機(jī)并不是6G轉(zhuǎn)型唯一重要的領(lǐng)域。Chidambaram舉了十字路口的例子。“一旦你完全實(shí)施了6G,借助異構(gòu)集成將延遲從現(xiàn)有的7-8ms降低到1-2ms,你就可以讓路邊單元完全管理十字路口,人們甚至不需要停車。”

當(dāng)然。他承認(rèn),啟用這樣的功能需要“大量的基礎(chǔ)設(shè)施建設(shè),才能履行所有的延遲要求和承諾,以及在路邊單元上的連接數(shù)量。”

Intel:chiplet制造所需的關(guān)鍵技術(shù)

談到異構(gòu)集成,Intel擁有得天獨(dú)厚的優(yōu)勢(shì)。Intel的業(yè)務(wù)涵蓋了芯片設(shè)計(jì)、內(nèi)部制造和外部代工服務(wù)。

Intel的高級(jí)副總裁兼裝配/測(cè)試開發(fā)總經(jīng)理Babak Sabi說(shuō):“未來(lái),Intel看到了需要將大量的內(nèi)核與內(nèi)存結(jié)合……以絕對(duì)最低的延遲和最高的帶寬”,這一切都會(huì)歸結(jié)為“互連和封裝問(wèn)題”。

Sabi指出,可以通過(guò)混合鍵合來(lái)堆疊芯片,這有助于減少每比特的皮焦。除了這種物理連接,“橫向集成”也是必要的,Sabi強(qiáng)調(diào),以盡可能密集的方式連接芯片。他說(shuō),這一步需要?jiǎng)?chuàng)新,“超越我們?cè)诰A級(jí)裝配中已經(jīng)擁有的技術(shù)”。

這就是玻璃基板變得極其重要的地方。Sabi說(shuō):“它讓我們能夠?qū)⑦@些巨大的復(fù)合體組合在一起,你可以完全消除interposer。我知道大家都喜歡銅,但銅最終會(huì)耗盡高速通信的能量。”未來(lái)在于Sabi所說(shuō)的“光學(xué)領(lǐng)域”。

混合鍵合的現(xiàn)狀

無(wú)論是wafer-to-wafer還是die-to-wafer,混合鍵合都是實(shí)現(xiàn)chiplet高級(jí)封裝的關(guān)鍵。

BE Semiconductor Industries N.V.(Besi)的CEO Richard Blickman表示,混合鍵合中最關(guān)鍵的元素是“裝配、互連和前端之間的握手”。這個(gè)過(guò)程仍然“處于非常早期的階段”。

盡管不愿預(yù)測(cè)混合鍵合何時(shí)會(huì)在更大規(guī)模上被采用,但Blickman強(qiáng)調(diào),在過(guò)去的兩年里,已經(jīng)有了大批量chiplet設(shè)計(jì)的PoC。不過(guò),他回顧說(shuō),flip chips在23年前就已推出,但多年后才成為主流,因此他建議大家耐心等待。他指出,混合鍵合需要更精確的粒子,這是設(shè)備供應(yīng)商面臨的“最大的敵人之一”。設(shè)備本身必須更小。

EV Group的技術(shù)執(zhí)行總監(jiān)Paul Lindner指出,“我們將晶圓鍵合視為規(guī)模提升的推動(dòng)器……它提供了將有源層從一個(gè)晶圓轉(zhuǎn)移到另一個(gè)晶圓的可能性,從而進(jìn)入晶圓背面。”

Lindner指出,晶圓鍵合已經(jīng)得到了不同的實(shí)現(xiàn),包括SOI晶圓(鍵合晶圓)。另一個(gè)大量應(yīng)用的例子是BSI傳感器(backside illuminatedsensor),這種傳感器可以接觸到光電二極管的背面,而不會(huì)受到布線的阻礙。他解釋說(shuō),這提高了傳感器的靈敏度。Lindner還看到3D NAND閃存正在采用混合鍵合。

混合鍵合的挑戰(zhàn)????????

那么,怎樣才能加快混合鍵合的應(yīng)用并實(shí)現(xiàn)大批量生產(chǎn)呢?

AMD的Fuselier說(shuō),“混合鍵合的神奇之處真的在于它所能帶來(lái)的密度”,這為芯片設(shè)計(jì)者提供了更多選擇。

“作為一個(gè)架構(gòu)師,我們需要弄清楚如何最好地利用這種密度來(lái)應(yīng)對(duì)我們面臨的一些挑戰(zhàn),無(wú)論是logic to logic,還是interconnect logic to memory。”Fuselier解釋說(shuō),還需要出現(xiàn)更多的創(chuàng)新。為此,“我們需要開發(fā)工具集來(lái)推動(dòng)這種互連。”

他說(shuō),雖然晶圓廠有很多工具,但封裝方面的工具集不足以讓芯片設(shè)計(jì)者決定是否使用混合鍵合。

Intel的Sabi從制造角度闡述了混合鍵合的問(wèn)題。

他指出,晶圓廠和封裝供應(yīng)商之間的更緊密合作至關(guān)重要。像混合鍵合這樣的技術(shù)“真的打破了兩者之間的界限”。在眾多挑戰(zhàn)中,他指出,互連的密度是巨大的。“我們需要極端的粒子控制能力,才能使CMP工藝保持原狀”,這是在整個(gè)晶圓上實(shí)現(xiàn)這種機(jī)制所必需的。

根據(jù)Intel的說(shuō)法,圍繞混合鍵合的許多挑戰(zhàn)可歸結(jié)為計(jì)量工具。Sabi說(shuō),“我們強(qiáng)調(diào)計(jì)量工具。因?yàn)槲覀儽仨氁业絾?wèn)題,這樣才能解決它們。”

考慮到混合鍵合模糊了傳統(tǒng)的前端處理和后端裝配測(cè)試之間的界限,像Qualcomm這樣的fabless巨頭需要什么呢?

Chidambaram指出,這一切都與系統(tǒng)級(jí)集成有關(guān)。在討論公司內(nèi)部的系統(tǒng)集成時(shí),他說(shuō),“負(fù)責(zé)CPU的人和其他開發(fā)射頻的人對(duì)彼此的領(lǐng)域了解不深。”為了實(shí)現(xiàn)不同領(lǐng)域的“協(xié)同優(yōu)化”,“我們需要工具,以及人們可以在這些不同領(lǐng)域之間使用的語(yǔ)言。”

Chidambaram從三維層面詳細(xì)介紹了混合集成,他說(shuō),“你說(shuō)的是創(chuàng)造一種后端類型的集成。要做到這一點(diǎn),你需要所有的物理學(xué)來(lái)解決問(wèn)題,同時(shí)還需要解決多個(gè)芯片的電氣行為。你把一個(gè)模塊從頂部移動(dòng)到底部,它會(huì)改變你的熱行為、改變你的機(jī)械行為,你需要同時(shí)優(yōu)化所有這些東西。”

阻礙chiplet發(fā)展的最大問(wèn)題是工具集。現(xiàn)有的各種工具,可以分別解決一些特定的問(wèn)題。但這個(gè)行業(yè)需要投資并開發(fā)能夠從三維角度解決異構(gòu)集成問(wèn)題的工具。

審核編輯:劉清

-

傳感器

+關(guān)注

關(guān)注

2553文章

51407瀏覽量

756657 -

電源管理

+關(guān)注

關(guān)注

115文章

6193瀏覽量

144960 -

SoC芯片

+關(guān)注

關(guān)注

1文章

617瀏覽量

35046 -

CMP

+關(guān)注

關(guān)注

6文章

151瀏覽量

26100 -

chiplet

+關(guān)注

關(guān)注

6文章

434瀏覽量

12632

原文標(biāo)題:AMD、Intel與Qualcomm如何思考chiplet?

文章出處:【微信號(hào):Astroys,微信公眾號(hào):Astroys】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

Chiplet或改變半導(dǎo)體設(shè)計(jì)和制造

AMD即將推出的 Hawk Point Refresh“Ryzen 200”APU 將應(yīng)對(duì) Intel 的 Raptor Lake Refresh “Core 200”CPU

Chiplet技術(shù)有哪些優(yōu)勢(shì)

AMD數(shù)據(jù)中心業(yè)務(wù)逆襲,營(yíng)收首超Intel

AMD數(shù)據(jù)中心業(yè)務(wù)收入超越Intel

IMEC組建汽車Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

突破與解耦:Chiplet技術(shù)讓AMD實(shí)現(xiàn)高性能計(jì)算與服務(wù)器領(lǐng)域復(fù)興

AMD采用Chiplet架構(gòu),每年減排數(shù)萬(wàn)噸溫室氣體

AMD Chiplet小芯片架構(gòu)年減排數(shù)萬(wàn)噸溫室氣體

凌華科技提供基于Intel Bay Trail處理器的核心計(jì)算模塊

Intel處理器全球份額高達(dá)78%!是AMD的六倍還多!

Intel近日發(fā)布新版Wi-Fi 7無(wú)線網(wǎng)卡驅(qū)動(dòng) 依然和AMD系統(tǒng)不對(duì)付

Chiplet是否也走上了集成競(jìng)賽的道路?

AMD、Intel與Qualcomm如何思考chiplet?

AMD、Intel與Qualcomm如何思考chiplet?

評(píng)論