使用重離子可以形成源/漏擴展(SDE)淺結(見下圖),通常PMOSSDE使用BF;,而NMOSSDE管使用Sb+重離子或As+。

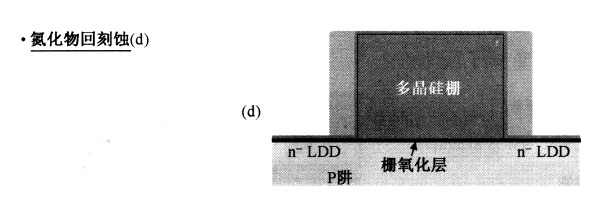

對于側壁間隔層的形成,經常使用氮化物和氧化物。如下圖所示,CVD沉積的氧化物作為刻蝕停止層,LPCVD氮化物形成側壁間隔層的主要部分。

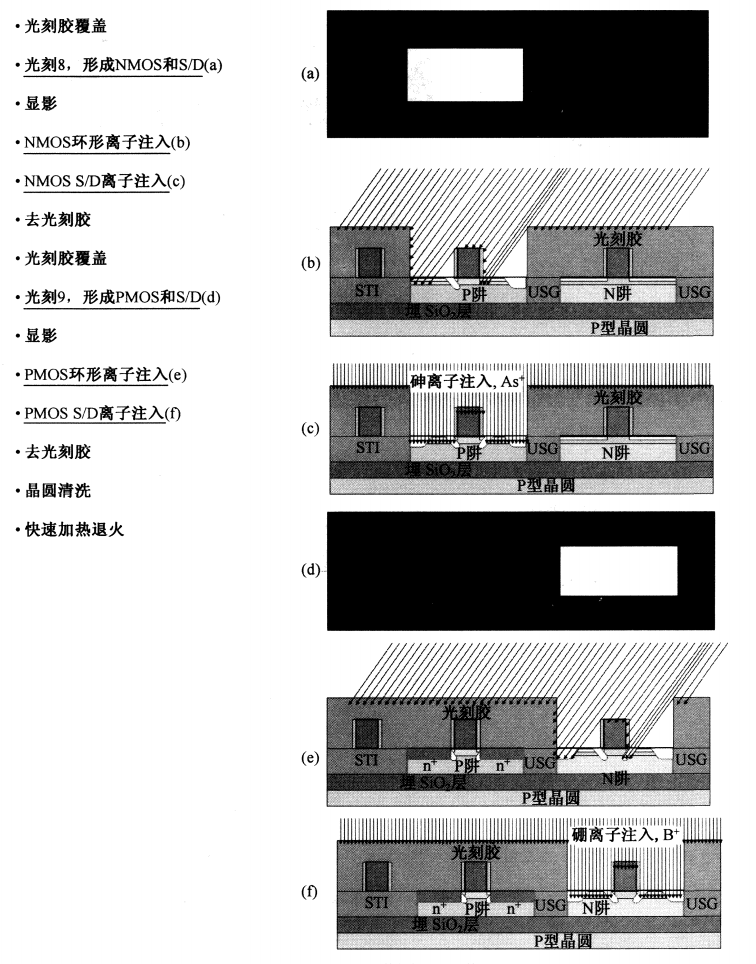

下圖顯示了CMOS形成的環形結和源/漏結。環形注入是一個大傾角離子注入過程,通常需要兩次或四次注入過程,這取決于MOSFET處于一個方向還是兩個方向。環形注入技術用于防止器件的串通。

為了獲得低的電阻,鈦硅化物的晶粒尺寸必須大于0.2um。當柵的寬度小于0.2um時,鈦硅化物的應用將受到挑戰。0.18um技術節點后,鈷硅化物開始取代鈦硅化物應用于柵極。由于鈷與空氣或濕氣接觸時,鈷很容易被氧化形成氧化鈷,所以使用氮化鈦覆蓋鈷防止其與濕氣接觸。利用集成配套工具,鈷和氮化鈦采用不同的PVD反應室沉積。

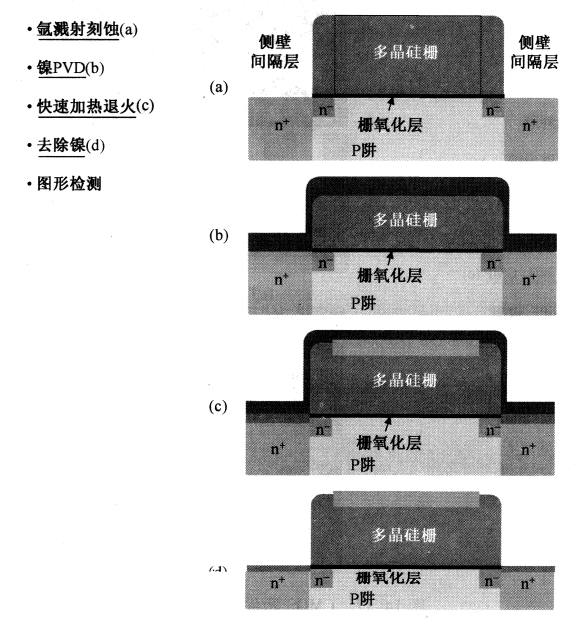

當器件尺寸進一步縮小到納米技術節點時,CoSi2的退火溫度(約750攝氏度)對于MOSFET微小的熱積存已經太高。鎳硅化合物(NiSi)可在溫度低于500攝氏度下形成,所以被廣泛用于65nm及更小的技術節點。

鎳沉積前,需要氯濺射刻蝕去除硅表面原生氧化層,否則,由于接觸電阻過高而導致IC芯片發生故障。由于NiSi熱穩定性不高,鎳容易與硅反應并穿通結面而引起漏電。在PVD靶材中,鉑(Pt)合金化并在晶圓表面形成NiPtSi以獲得更好的硅化物穩定性。可以使用電子束檢查(EBI)系統監測鎳擴散對成品率的影響。下圖顯示了硅化物形成工藝流程。

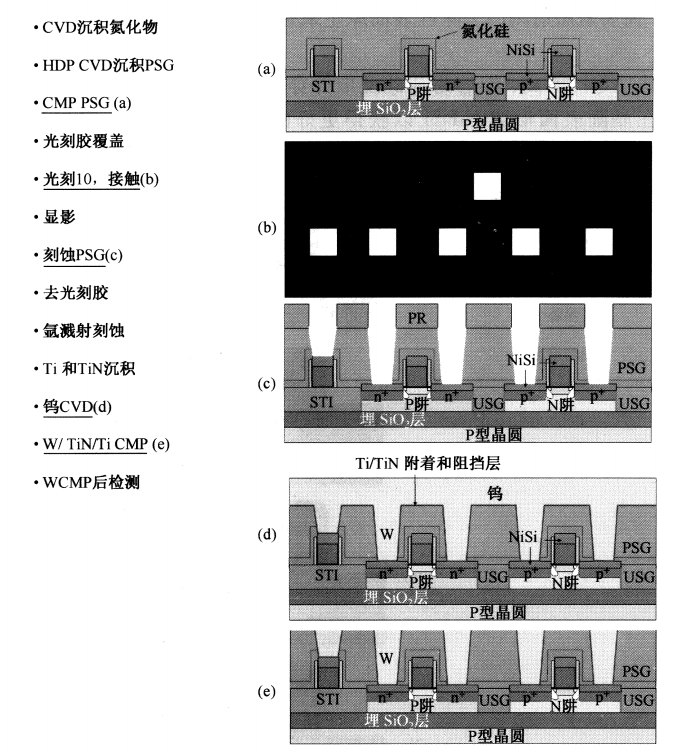

需要氮化物層防止磷從PSG中擴散到有源區。由于熱積存的限制,利用PECVD氮化硅在較低溫度(小于580攝氏度)下沉積取代LPCVD氮化物沉積(沉積溫度為750攝氏度)。對于小尺寸器件(小于0.18um),PMD熱再流動的熱積存很小,因此硅酸鹽玻璃中不再需要硼,PSG取代BPSG材料形成PMD。PSG利用CMP平坦化而不是熱再流動。鈣僅用于局部互連,以及源/漏、金屬與硅化物之間的栓塞。鈦和氮化鈦作為阻擋層和鎢附著層。

對于一些先進技術節點的CMOS工藝,USG用于ILD0,氮化物層用于應力緩沖層應變溝道,從而提高載流子的遷移率和MOSFET的性能。

接觸非常關鍵,因為它將晶圓表面上的器件和各層的金屬線互連。如果接觸孔刻蝕不完全,金屬導線將無法和器件相連,這將導致成品率下降。

PVD鈦廣泛用于減少接觸電阻,氮化鈦(TiN)作為鎊附著層。如果沒有TiN,鎢薄膜將不會與硅晶圓表面很好地附著,這將導致裂紋并使鈞薄膜從晶圓表面脫落,最后在晶圓上產生大量顆粒污染。TiN可以利用PVD和CVD沉積。當器件特征尺寸不斷縮小時,接觸孔的深寬比將變得很大,PVD工藝將不再提供足夠的臺階覆蓋,因此CVDTiN工藝更受歡迎。下圖顯示了CMOS器件接觸示意圖。

審核編輯:湯梓紅

-

CMOS

+關注

關注

58文章

6005瀏覽量

238540 -

MOSFET

+關注

關注

150文章

8455瀏覽量

219514 -

半導體

+關注

關注

335文章

28777瀏覽量

235333 -

ICT

+關注

關注

3文章

426瀏覽量

37068

原文標題:半導體行業(一百九十五)之ICT技術(五)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體行業制造工藝解析

半導體行業制造工藝解析

評論