來源:《半導(dǎo)體芯科技》期刊

半導(dǎo)體制造商如今擁有的新設(shè)備可達(dá)到最佳晶圓良率,這種新設(shè)備的兆聲波系統(tǒng)應(yīng)用了空間交變相位移(SAPS)和時序能激氣穴震蕩(TEBO)技術(shù)。

半導(dǎo)體芯片的特征尺寸正快速縮小。動態(tài)隨機(jī)存取存儲器(DRAM)制造商現(xiàn)在正在生產(chǎn)12納米級16GB芯片,電容器縱橫比為60:1。NAND結(jié)構(gòu)達(dá)到232層,蝕刻縱橫比更大。而邏輯電路正向3納米節(jié)點全環(huán)繞柵極(GAA)晶體管的第一階段邁進(jìn)。

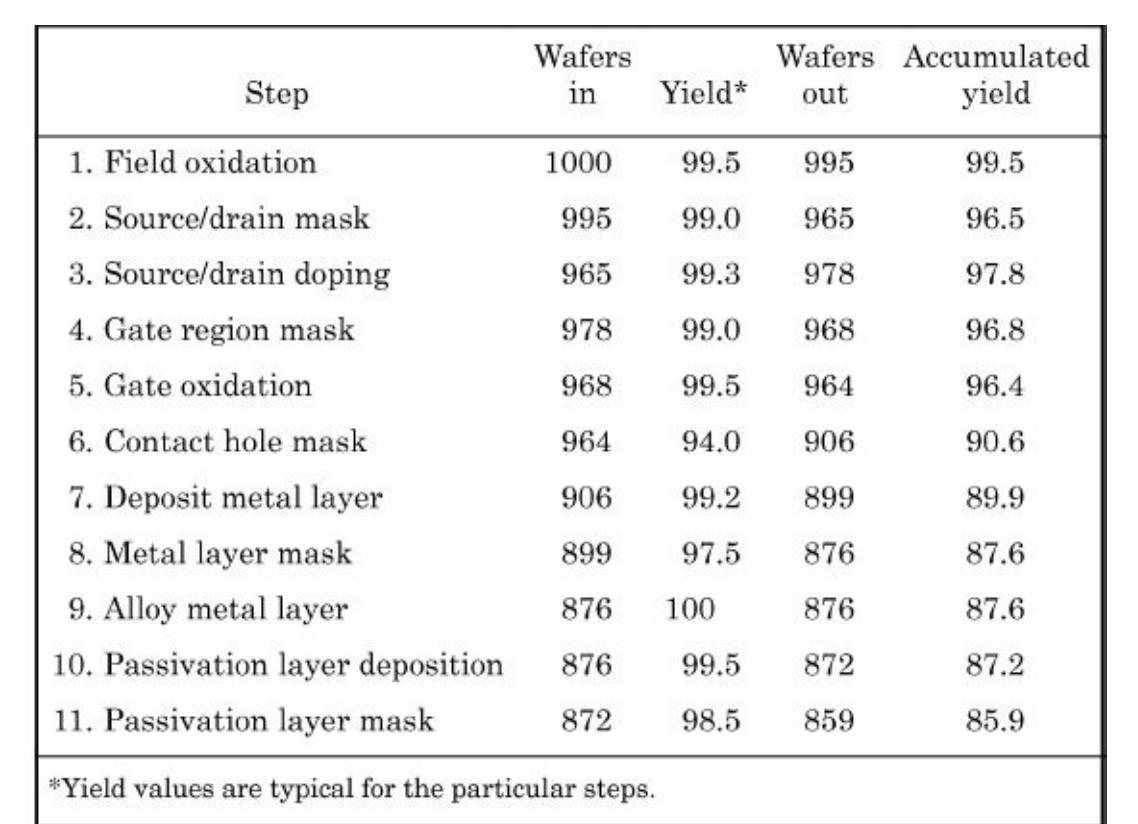

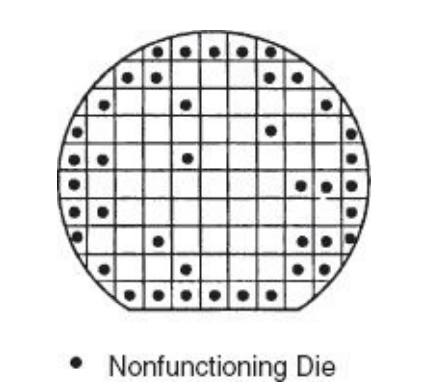

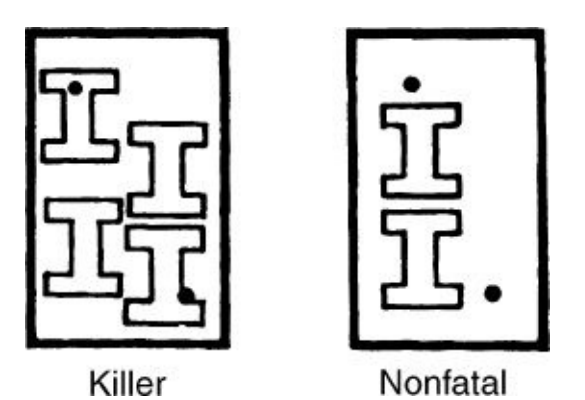

隨著結(jié)構(gòu)尺寸越來越小,工藝技術(shù)變得更具挑戰(zhàn)性,去除污染和隨機(jī)缺陷變得極其困難。當(dāng)特征尺寸和薄膜厚度達(dá)到10納米(100埃)級時,即使是1納米(10埃)微粒也可能成為導(dǎo)致晶體管失效的致命缺陷。隨著芯片特征尺寸不斷降低至10納米以下,如何去除微粒及其它污染物質(zhì)以獲得理想良率,將是半導(dǎo)體制造商所面臨的一項重大技術(shù)挑戰(zhàn)。

隨著結(jié)構(gòu)尺寸越來越小,工藝技術(shù)變得更具挑戰(zhàn)性,去除污染和隨機(jī)缺陷變得極其困難。當(dāng)特征尺寸和薄膜厚度達(dá)到10納米(100埃)級時,即使是1納米(10埃)微粒也可能成為導(dǎo)致晶體管失效的致命缺陷。隨著芯片特征尺寸不斷降低至10納米以下,如何去除微粒及其它污染物質(zhì)以獲得理想良率,將是半導(dǎo)體制造商所面臨的一項重大技術(shù)挑戰(zhàn)。

當(dāng)今的先進(jìn)技術(shù)使得特征尺寸更小更精細(xì),傳統(tǒng)的顆粒去除清洗技術(shù)因此面臨著挑戰(zhàn)。具體來說,噴淋清洗技術(shù)的壓力水平太強;物理力會損壞晶體管和電容器結(jié)構(gòu)的表面特征,有可能使其脫離晶圓。噴淋技術(shù)也無法深入到縱橫比很高的溝槽中。

由于能量不能均勻傳遞到深層結(jié)構(gòu)中,傳統(tǒng)兆聲波清洗很難處理小型深溝槽。傳統(tǒng)的兆聲波技術(shù)不能保證整個晶圓的均勻表面覆蓋,這往往會導(dǎo)致某些晶圓區(qū)域的清洗不足。這會導(dǎo)致良率下降。這些工藝還會造成表面粗糙、材料損耗等問題,當(dāng)1埃對芯片性能至關(guān)重要時,這些問題就會極大地影響這些先進(jìn)器件的性能。本質(zhì)上,兆聲波晶圓清洗方法和傳統(tǒng)清洗方法的水平都已達(dá)到極限,在不損壞芯片上的特征的情況下,不再能夠去除極其微小的致命缺陷。

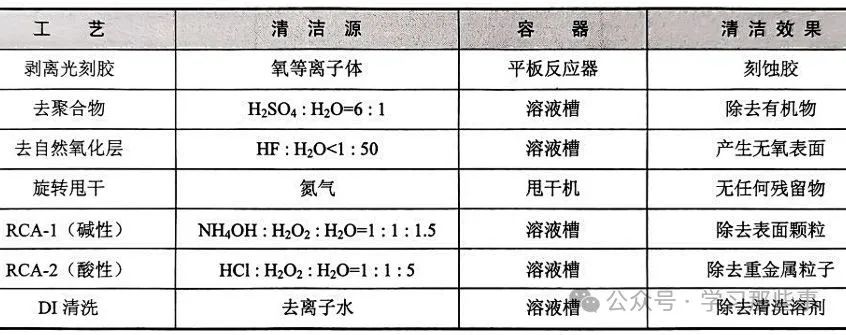

目前,從圖形化半導(dǎo)體中去除顆粒的方法正逐步成為一門重點科學(xué)。隨著芯片特征尺寸不斷縮小,并向立體化發(fā)展,使用刷洗設(shè)備、噴淋設(shè)備、超聲波和兆聲波進(jìn)行強力清洗的方式逐漸得以改良,以免損壞芯片結(jié)構(gòu)。新的單晶圓清洗工藝技術(shù)解決了清洗目前和下一代半導(dǎo)體芯片上圖案結(jié)構(gòu)的關(guān)鍵問題。

新一代清洗技術(shù)

為了解決半導(dǎo)體設(shè)備制造商面臨的清洗挑戰(zhàn),盛美開發(fā)了Smart Megasonix?——一套更具智能和創(chuàng)新性的單晶圓濕法清洗技術(shù),可以應(yīng)用于現(xiàn)有或未來工藝節(jié)點,在不影響器件特性的情況下,通過一系列工藝步驟,達(dá)到更加徹底、全面的清洗。這些專有技術(shù)可以控制兆聲波清洗的功率強度和分布范圍。

公司已經(jīng)開發(fā)了兩項關(guān)鍵技術(shù),以增強兆聲波清洗系統(tǒng)的清洗能力。第一項是空間交變相位移(SAPS?)晶圓清洗技術(shù)。SAPS技術(shù)是一種先進(jìn)的兆聲波工藝,這種工藝?yán)谜茁暡?a target="_blank">傳感器與晶圓間的空隙,使兆聲波相位發(fā)生變化。SAPS技術(shù)可以在晶圓旋轉(zhuǎn)的同時移動或傾斜傳感器,即使晶圓翹曲,也能在晶圓的每一點上均勻提供兆聲波能量。

這確保了最佳的能量輸送,當(dāng)與適當(dāng)?shù)南♂尰瘜W(xué)成分相結(jié)合時,為去除晶圓缺陷創(chuàng)造了合適的環(huán)境。SAPS技術(shù)精確度高,可有效地提高顆粒去除過程中的傳質(zhì)速率,及系統(tǒng)中顆粒去除效率。應(yīng)用SAPS技術(shù)可以提高生產(chǎn)效率,及顆粒去除效率,從而提高產(chǎn)能,降低晶圓生產(chǎn)成本。

兆聲波技術(shù)的第二項創(chuàng)新技術(shù)是時序能激氣穴震蕩(TEBO?)技術(shù)。傳統(tǒng)兆聲波技術(shù)通過空化效應(yīng)來產(chǎn)生氣泡,這些氣泡能夠有效進(jìn)行清洗。在傳統(tǒng)系統(tǒng)中,這些氣泡可能發(fā)生內(nèi)爆或破裂,進(jìn)而破壞精細(xì)圖形。采用TEBO技術(shù)后,空化效應(yīng)更加穩(wěn)定,不會產(chǎn)生氣泡內(nèi)爆或破裂。從而能夠在不損壞DRAM的高縱橫比電容器和3D NAND的高縱橫比溝槽和孔洞等精細(xì)圖形的前提下,成功地去除缺陷。該技術(shù)還能去除先進(jìn)的鰭式場效晶體管(FinFET)和GAA結(jié)構(gòu)的缺陷。隨著芯片特征尺寸不斷變小,縱橫比不斷增大,去除蝕刻、光刻膠的殘余物和化學(xué)機(jī)械研磨顆粒的挑戰(zhàn)變得更大。晶圓特征更易被破壞,原子作用力更大,這導(dǎo)致晶圓表面的瑕疵更難去除。對于先進(jìn)節(jié)點的加工而言,需要采用不會損壞關(guān)鍵特征的新型清潔化學(xué)成分和機(jī)械方法來去除缺陷。隨著SAPS和TEBO技術(shù)被引入兆聲波系統(tǒng),半導(dǎo)體制造商如今在力爭實現(xiàn)最佳的晶圓良率方面擁有了新的工具。

審核編輯:湯梓紅

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28902瀏覽量

237698 -

DRAM

+關(guān)注

關(guān)注

40文章

2348瀏覽量

185616 -

晶圓

+關(guān)注

關(guān)注

53文章

5161瀏覽量

129770 -

清洗技術(shù)

+關(guān)注

關(guān)注

0文章

18瀏覽量

6574

發(fā)布評論請先 登錄

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數(shù)據(jù)測量的設(shè)備

晶圓擴(kuò)散清洗方法

晶圓濕法清洗工作臺工藝流程

8寸晶圓的清洗工藝有哪些

8寸晶圓清洗槽尺寸是多少

先進(jìn)封裝技術(shù)-17硅橋技術(shù)(下)

晶圓切割技術(shù)知識大全

晶圓微凸點技術(shù)在先進(jìn)封裝中的應(yīng)用

先進(jìn)的清洗技術(shù)如何助力先進(jìn)節(jié)點實現(xiàn)最佳晶圓良率

先進(jìn)的清洗技術(shù)如何助力先進(jìn)節(jié)點實現(xiàn)最佳晶圓良率

評論