Microblaze是32位/64位 RISC軟核處理器,可以用作微處理器、實時處理器和應用處理器(Linux+MMU)。Microblaze作為FPGA的軟核,搭建硬件系統時有豐富的IP資源,軟件開發則有配套的SDK軟件。 目前Microblaze在工業、醫療、汽車、消費以及通信市場有著廣泛的應用。

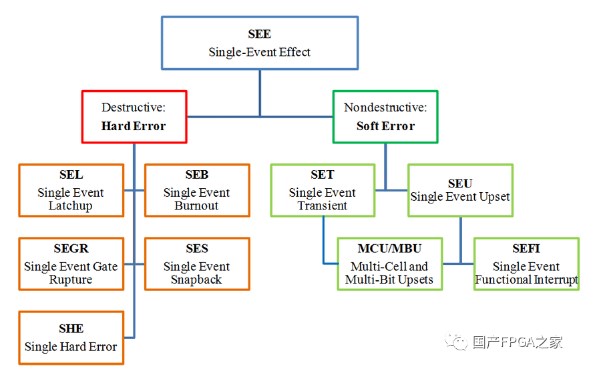

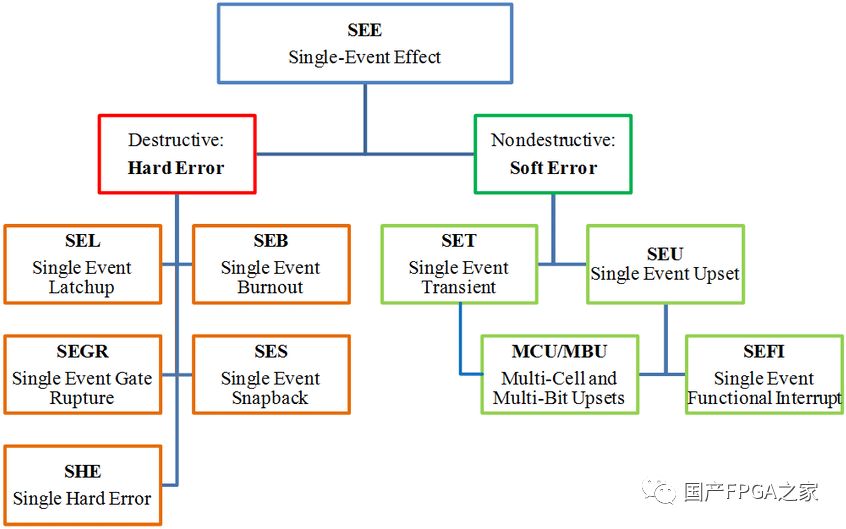

Microblaze有這么多優點,是否可以用在宇航市場上呢?空間環境中,FPGA會受到單粒子效應影響,Microblaze是使用FPGA內部的資源來實現的,可能會發生功能中斷或程序跑飛等情況,因此需要對Microblaze進行軟件層面的加固來降低SEE的影響。

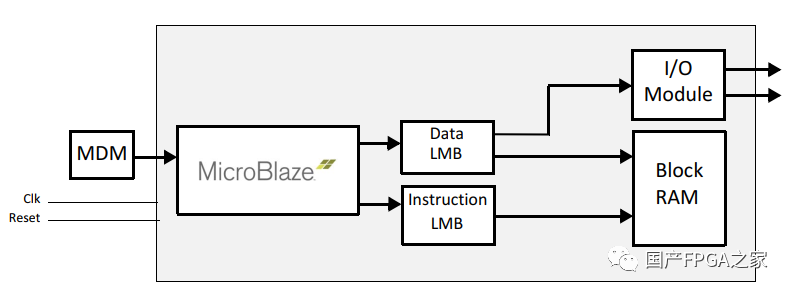

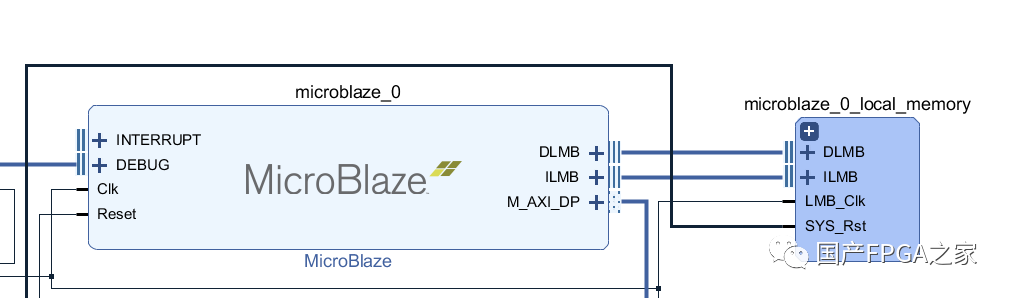

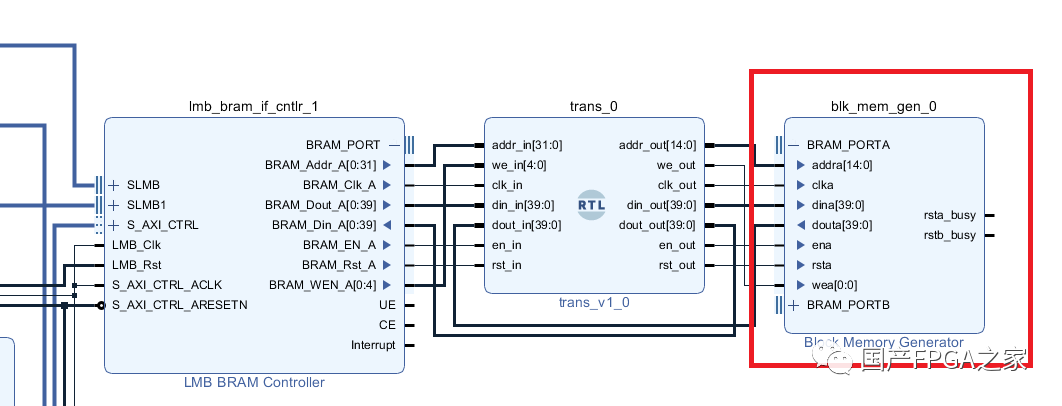

Microblaze最小系統的組成包括Clock Wizard,Processor System Reset,Microblaze IP,Data Local Memory Bus, Instruction Local Memory Bus,Data LMB BRAM Controller, Instruction LMB BRAM Controller和Block Memory。 今天貧道以Microblaze最小系統為例,簡單介紹一下PG268 Xilinx方案(Fault torelant和Fail safe),然后著重介紹高可靠加固方案、方案在TMR工具的實現和故障注入驗證結果,如圖1所示:

圖1 Microblaze最小系統

01

Xilinx 加固方案

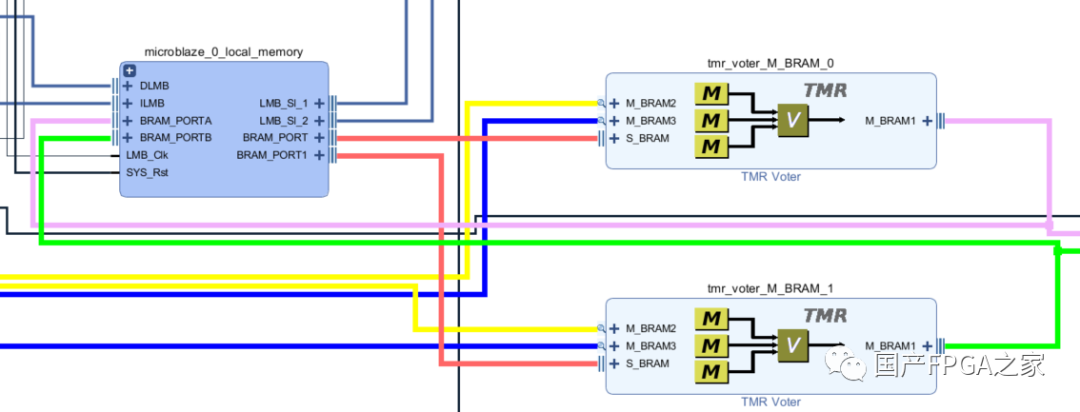

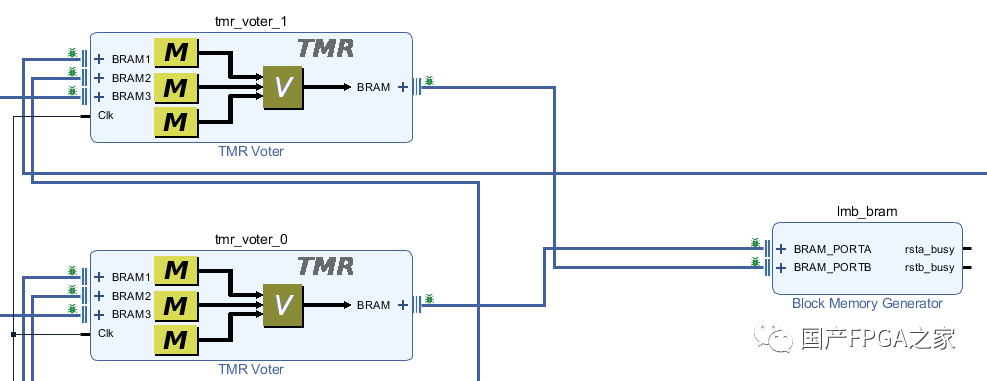

Fault-tolerant Type是對原系統整體復制兩份,并在關鍵的Data LMB Controller和Instruction LMB Controller增加判決器,并對IO接口增加判決器。假如單路MB由于SEE發生軟錯誤,那么通過判決器能夠把軟錯誤屏蔽掉。Fault-tolerant Type優點是實現簡單,只需要利用好TMR Manager的Run block Automation功能,就能一鍵實現加固。Fault-tolerant Type屬于粗粒度加固,因此缺點是可靠性提升有限。

圖2 Fault-tolerant默認框圖

圖3 TMR Voter插入位置 值得一提的是Fault-tolerant Type默認的方案是對BRAM做TMR,如果BRAM資源受限,那么可以更改設計對BRAM做ECC。

圖4 Fault-tolerant Type ECC實現

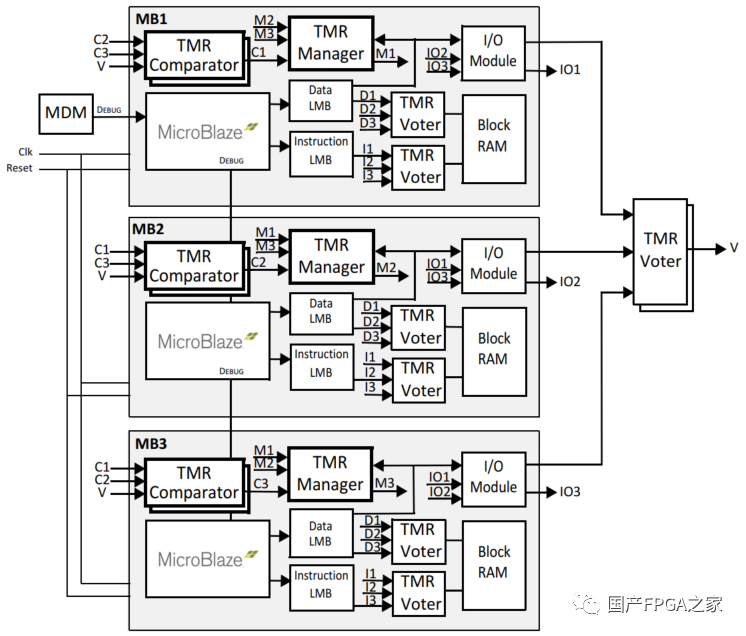

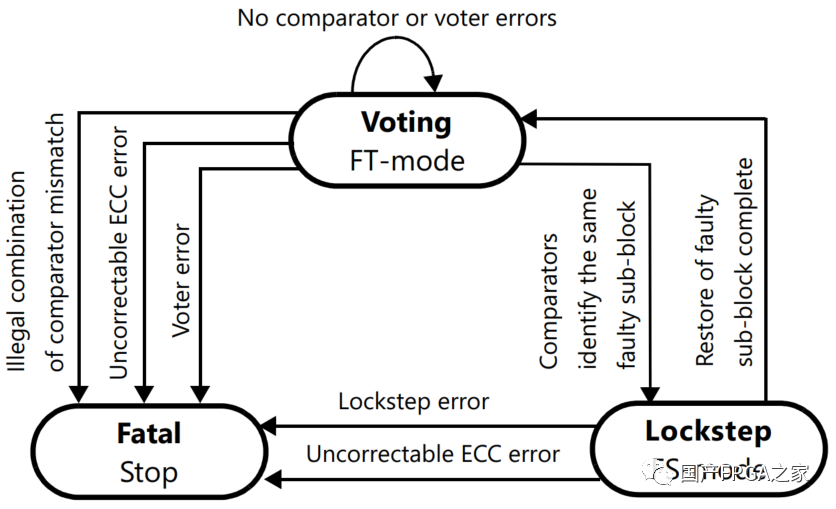

Fail-Safe Type加入了TMR Comparator,實時對三個sub block進行比較。當某一個sub block發生異常的時候,另外兩路正常的sub block進入到lock step模式。Lock step模式下,一旦發現兩路sub block數據不一致,那么就會進入到Fatal stop模式。

Fail-Safe Type的優點是可以在lock step模式下,通過APP嘗試進行恢復,恢復成功后重新返回到fault torelant模式。Fail-Safe Type的優點也是缺點,APP需要用戶自行開發,設計比較復雜。此外如果軟錯誤比較嚴重,會進入到Fatal stop模式,該模式沒法完成恢復,只能重新加載來解決軟錯誤。

圖5 Fail-Safe Type框圖

圖6 Fail-Safe Type故障模式轉換流程

02

高可靠加固方案

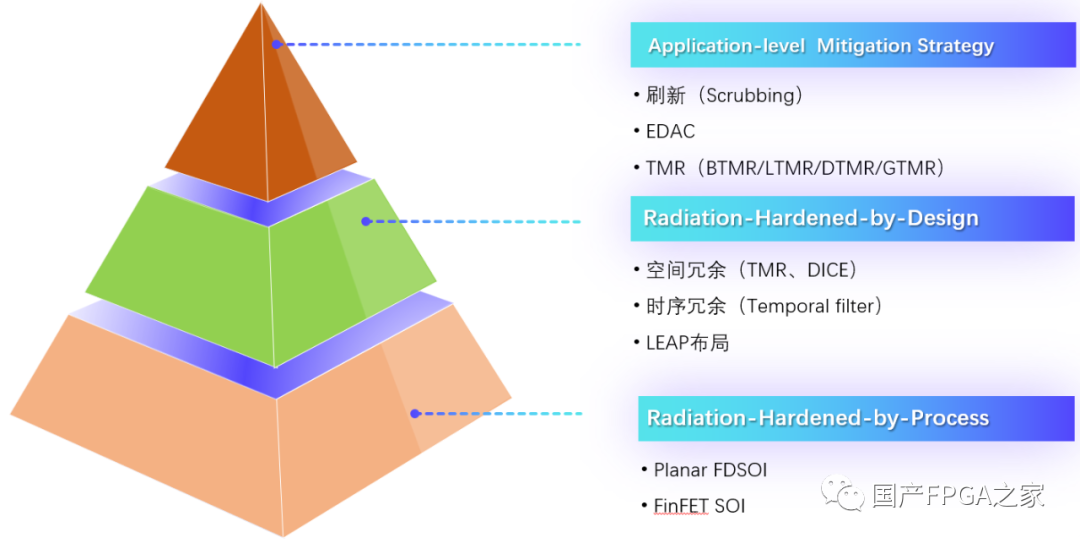

高可靠加固方案是把Microblaze當做一般的IP,在網表層面采用TMR工具進行細粒度加固。同時考慮Microblaze的特點,對存儲器BRAM進行TMR加固或者ECC加固。考慮到TMR或者ECC只能屏蔽錯誤,無法消除錯誤。因此為了更進一步提高可靠性,對儲存器采用ECC+回寫刷新,這樣可以消除錯誤。本文只討論Local Memory應用場景的加固方案和實現,下面將對實現部分做簡要的介紹。

1.1存儲器BRAM ECC實現

Microblaze默認的Local Memory結構如下圖所示,需要做的是展開microblaze_0_local_memory。

圖7 MicroblazeLocal Memory

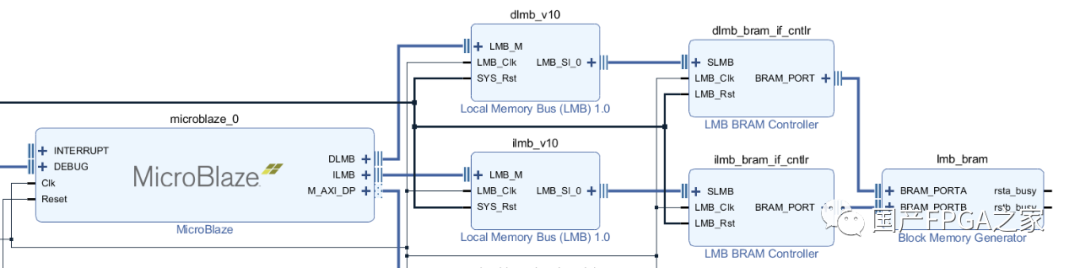

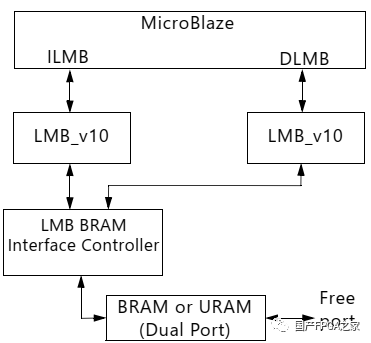

展開microblaze_0_local_memory,可以看到local_memory是由LMB Bus、LMB BRAM Controller和Block Memory組成。

圖8 LocalMemory結構

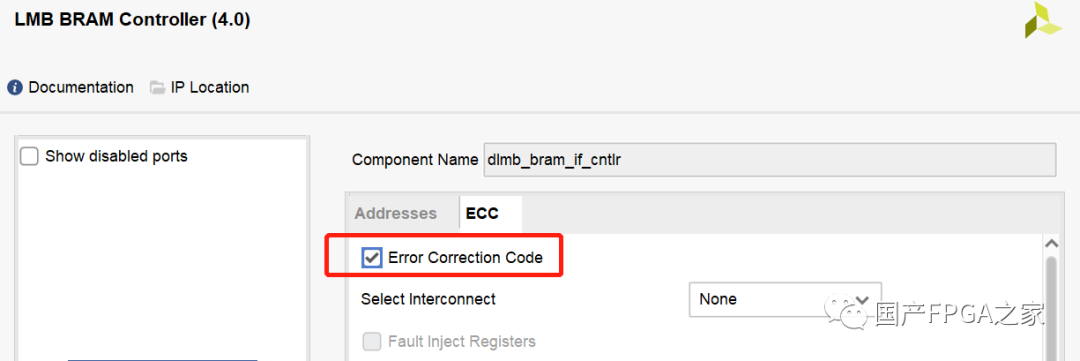

需要做的是打開LBM BRAM Controller,勾選Error Correction Code。

圖9 LMB BRAM Controller設置

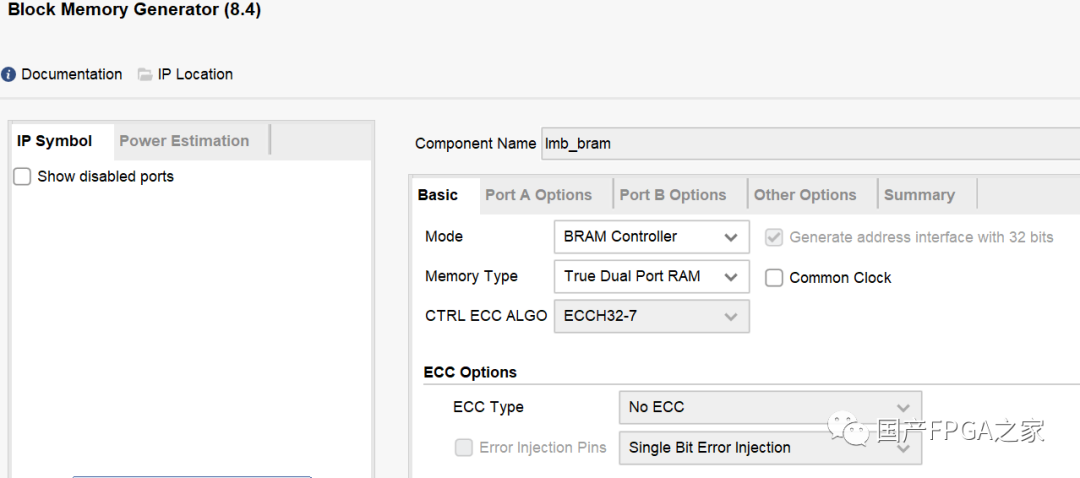

工具自動實現更改Block Memory屬性,使用Soft方式來實現BRAM的ECCH32-7編解碼。

圖10 Block Memroy ECC參數設置

2.1存儲器BRAMECC+自刷新邏輯

默認的Local Memroy結構里面,BRAM的兩個端口都被占用住,要想實現自刷新就得更改Local Memroy結構。Microblaze支持復用DLMB和ILMB的控制器,這樣兩個控制器就共用一個BRAM端口,另一個端口用于自刷新,如下圖所示:

圖11 共享memory結構

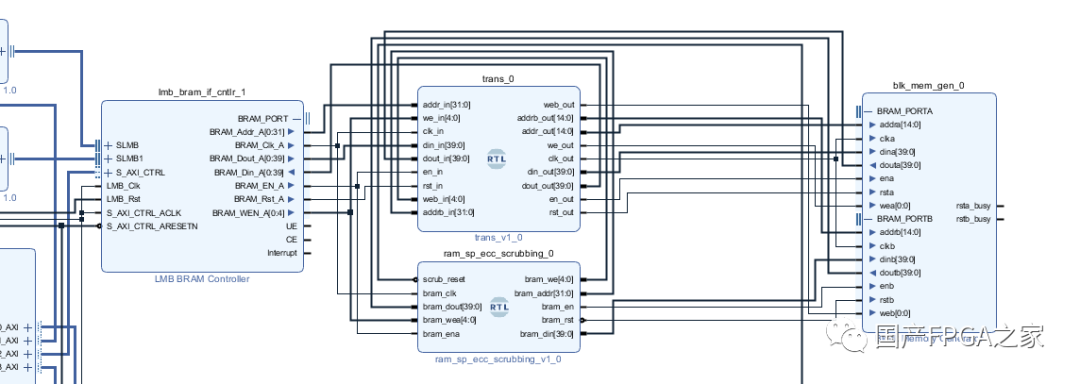

開發的自刷新模塊連接到Freeport上,對BRAM全地址循環遍歷,讀出數據(32bit)和校驗位(7bit)進行1bit錯誤糾錯。如果解碼過程出現1bit錯誤,把糾錯后的數據回寫到BRAM中。

圖12 自刷新結構

2.2MicroBlaze System TMR實現

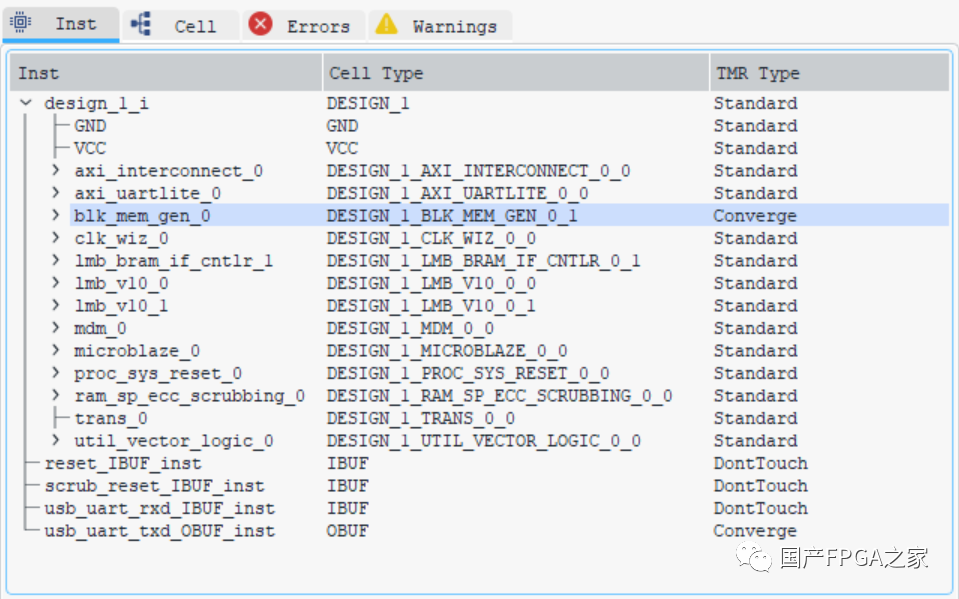

TMR工具可以對任意資源設置屬性,Block Memroy采樣ECC方案,因此屬性設置為Converge。

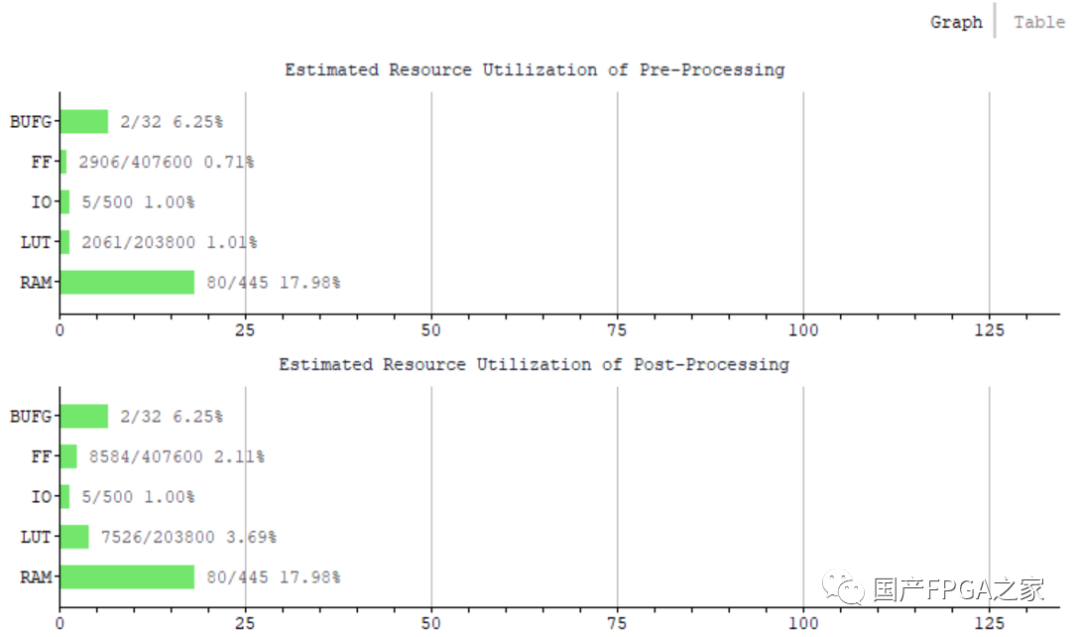

圖13 TMR工具Custom模式下參數自定義設置 TMR工具可以統計出加固前的資源消耗,以及預估加固后的資源消耗,便于設計師進行評估和迭代設計。

圖14TMR工具加固前資源統計和加固后資源預估

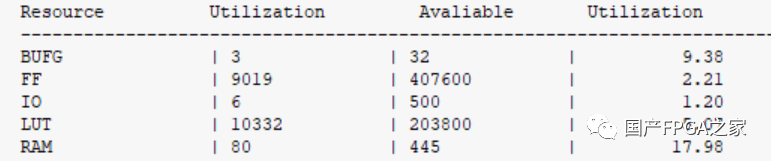

加固完成后,TMR工具可以統計出準確的資源使用情況。

圖15TMR工具加固后資源統計

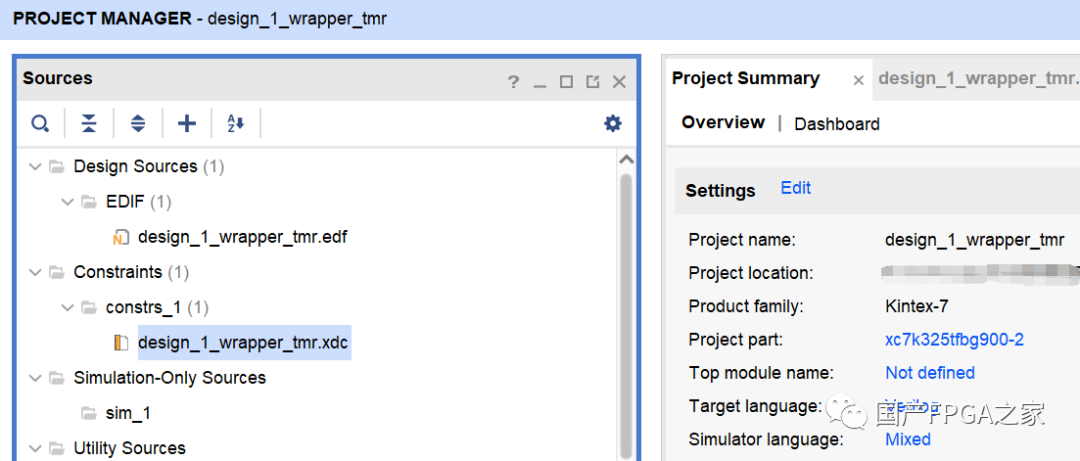

TMR工具自動創建加固后工程并自動添加約束文件。

圖16 TMR PSOT工程

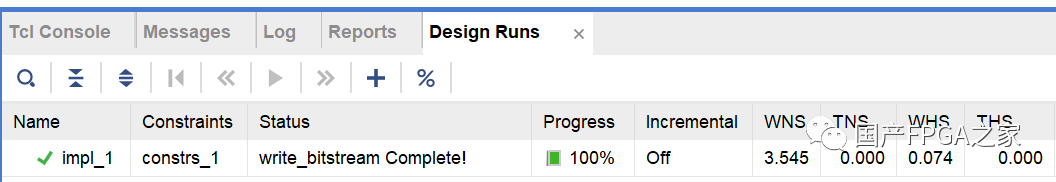

執行Implementation和Generate Bitstream。

圖17 POST工程完成IMPL和BITGEN

2.3故障注入驗證

Microblaze System采用TMR進行加固可靠性得到提升,TMR加固推薦采用DTMR/GTMR加固方式。Microblaze System中存儲器部分選擇的是ECC加固,需要針對Block Memroy進行故障注入驗證。

圖18 BRAM故障注入測試 故障注入驗證結果如下:

1)存儲區不加固,隨機注入70~100bit錯,系統異常

2)存儲區ECC糾錯,隨機注入700~800bit錯,系統異常

3)存儲區ECC糾錯+回寫,隨機注入10000bit錯,系統仍正常工作 Microblaze采樣高可靠方案進行加固后可靠性得到提升,采用ECC糾錯+自刷新措施可靠性最高。軟核除了在FPGA內部進行軟加固外,還應該采用外部Scrubber來消除CRAM的累積錯誤,這樣經過多種加固措施后的軟核應該能滿足大部分的空間應用需求。

審核編輯:劉清

-

FPGA

+關注

關注

1645文章

22028瀏覽量

617717 -

sram

+關注

關注

6文章

784瀏覽量

115864 -

微處理器

+關注

關注

11文章

2379瀏覽量

84105 -

TMR

+關注

關注

5文章

95瀏覽量

19462 -

BRAM

+關注

關注

0文章

41瀏覽量

11293

原文標題:論SRAM型FPGA軟核Microblaze抗單粒子加固

文章出處:【微信號:國產FPGA之家,微信公眾號:國產FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

單粒子翻轉引起SRAM型FPGA的故障機理闡述

軟錯誤防護技術在車規MCU中應用

用SOI技術提高CMOSSRAM的抗單粒子翻轉能力

基于MicroBlaze 軟核的FPGA 片上系統設計

基于MicroBlaze軟核的FPGA片上系統設計

基于MicroBlaze軟核的FPGA片上系統設計

如何使用MicroBlaze軟核進行FPGA片上系統設計

論SRAM型FPGA軟核Microblaze抗單粒子加固的方法

論SRAM型FPGA軟核Microblaze抗單粒子加固的方法

評論