增量綜合流程:

增量綜合的工作方式與增量實(shí)現(xiàn)流程相似,但僅適用于綜合階段,并且不會(huì)對(duì)緊隨其后的實(shí)現(xiàn)階段給予引導(dǎo)。

此流程需獨(dú)立的綜合參考文件(綜合后 DCP),因此您需完成初始綜合運(yùn)行以獲取首個(gè)綜合后 DCP 文件。增量運(yùn)行會(huì)復(fù)用設(shè)計(jì)中未更改的部分,并且僅對(duì)已更改的部分進(jìn)行重新綜合。復(fù)用的各部分會(huì)在分區(qū)級(jí)別予以保留。

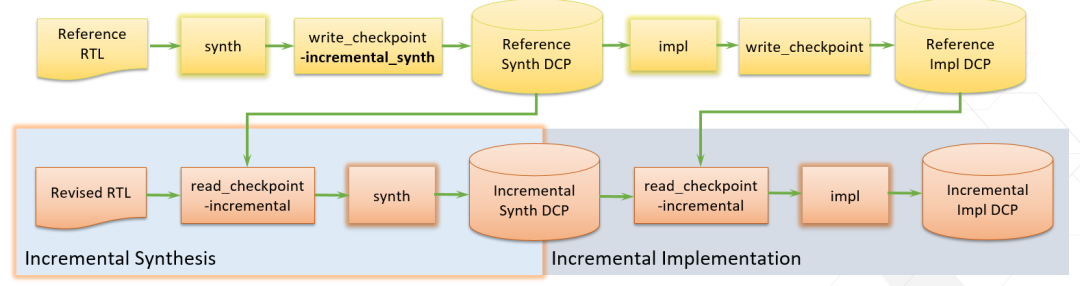

以下圖表顯示了含腳本的非工程流程:

圖:增量流程圖表

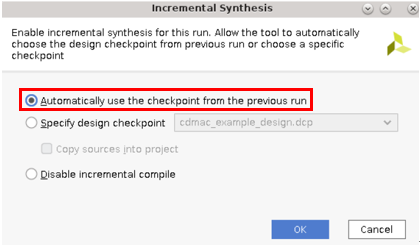

在 GUI 中支持通過以下兩種方法來指定參考檢查點(diǎn):

使用自動(dòng)增量參考檢查點(diǎn)(當(dāng)前僅在 GUI 中受支持)

使用用戶指定的參考檢查點(diǎn)

要在工程模式下啟用自動(dòng)模式,請(qǐng)打開綜合設(shè)置,并選中“Automatically use the checkpoint from the previous run”(自動(dòng)使用上一輪運(yùn)行的檢查點(diǎn))選項(xiàng)。

在此模式下,綜合運(yùn)行將把最近的綜合后網(wǎng)表自動(dòng)復(fù)制到工程目錄本地的 /project.srcs/utils_1/import/design 區(qū)域內(nèi)。

完成整個(gè)流程后,新布線的檢查點(diǎn)即可立即用作為下一輪運(yùn)行的參考檢查點(diǎn),并在運(yùn)行復(fù)位時(shí)進(jìn)行更新。 如不勾選自動(dòng)模式,也可輸入用戶指定的 DCP 作為參考檢查點(diǎn),以便引導(dǎo)后續(xù)輪次的運(yùn)行。

圖:設(shè)計(jì)運(yùn)行設(shè)置

何時(shí)采用此流程:

當(dāng)設(shè)計(jì)所含實(shí)例數(shù)量超過 50K 時(shí),始終建議啟用此流程。如果設(shè)計(jì)太小,由于改善的空間不夠大,將忽略增量模式,設(shè)計(jì)將以正常流程運(yùn)行。

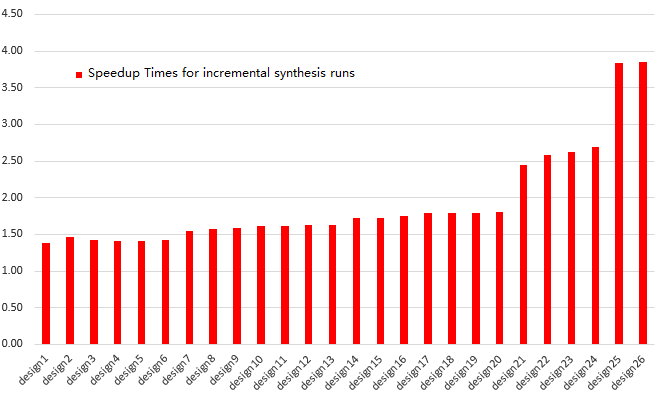

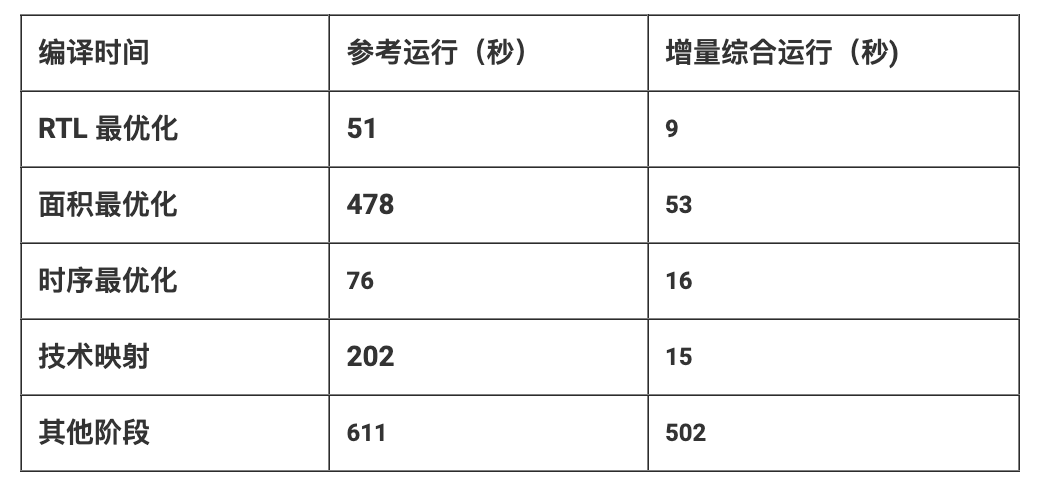

當(dāng)綜合運(yùn)行超過 20 分鐘時(shí),采用增量綜合流程前后的運(yùn)行時(shí)間平均比值為 2.06,改善顯而易見。下圖顯示了 26 個(gè)大型設(shè)計(jì)的加速趨勢(shì),在對(duì)設(shè)計(jì)進(jìn)行有限的更改時(shí),可節(jié)省大量編譯時(shí)間(低至更改前的四分之一)。

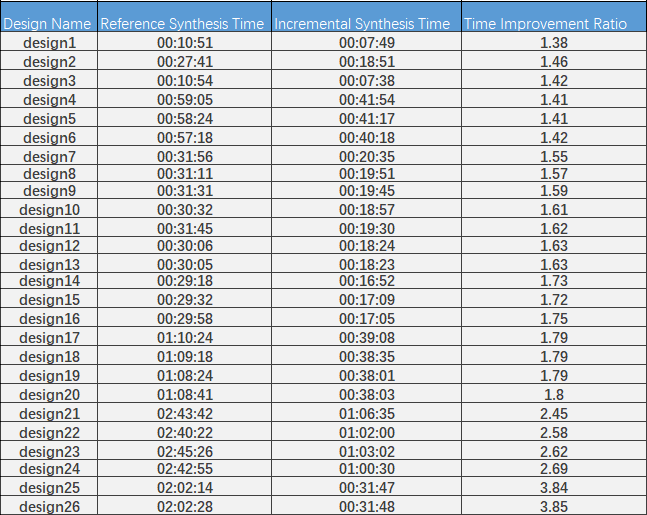

下表所示每項(xiàng)設(shè)計(jì)所耗用的時(shí)間也證明,小幅更改設(shè)計(jì)的前提下,參考運(yùn)行時(shí)間越長(zhǎng),通過增量運(yùn)行節(jié)省的時(shí)間就越多。因此,大型設(shè)計(jì)利用該流程獲益頗豐。

建議您始終為大型設(shè)計(jì)啟用自動(dòng)模式來運(yùn)行增量綜合。但要立即使用增量綜合,必須向參考檢查點(diǎn)寫入綜合數(shù)據(jù)。為此,可使用 write_checkpoint -incremental_synth 開關(guān)。

圖:部分設(shè)計(jì)示例中的編譯時(shí)間節(jié)省效果

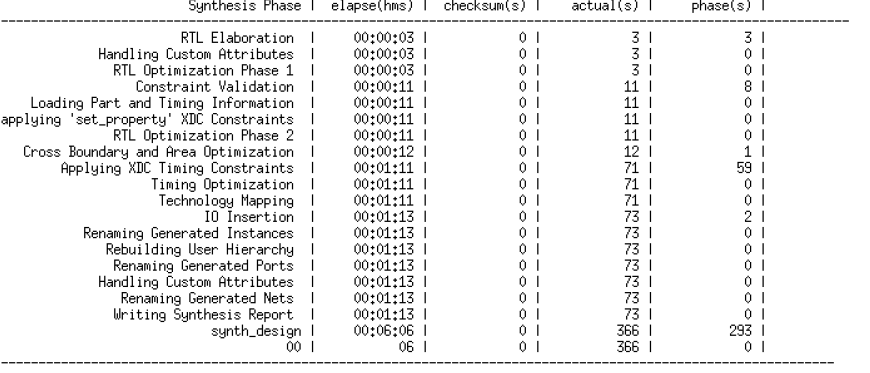

此處隨附的 getSynStepsRunTime.sh 腳本(請(qǐng)點(diǎn)擊閱讀原文查看)可用于為 synth_design 的每個(gè)階段生成時(shí)間剖析表。

要運(yùn)行該腳本,您可按如下示例所示使用此命令并為初始運(yùn)行和增量運(yùn)行生成表格。“actual”(實(shí)際)列和“phase”(階段)列中羅列了用于每個(gè)階段的時(shí)間和累計(jì)時(shí)間。

getSynStepsRunTime.sh ./vivado.log

增量綜合運(yùn)行期間,下列步驟的編譯時(shí)間都比參考運(yùn)行更短:“RTL Optimization”(RTL 最優(yōu)化)、“Area Optimization”(面積最優(yōu)化)、“Timing Optimization”(時(shí)序最優(yōu)化)和“Technology Mapping”(技術(shù)映射)。

下表顯示了用戶設(shè)計(jì)示例。請(qǐng)注意參考運(yùn)行與增量運(yùn)行中每個(gè)綜合階段所耗費(fèi)的時(shí)間。由于這些階段占用了大部分的參考編譯時(shí)間,因此對(duì)總體運(yùn)行時(shí)間影響尤為顯著。

增量綜合期間,“RTL Elaboration”(RTL 細(xì)化)、“Constraint Validation”(約束確認(rèn))、“Applying XDC Timing Constraints”(應(yīng)用 XDC 時(shí)序約束)、“I/O Insertion”(I/O 插入)、“Global Opt”(全局最優(yōu)化)、“Netlist Generation”(網(wǎng)表生成)等其他階段以及其余用于拼接的階段在時(shí)間上所呈現(xiàn)的改善較少。

注釋:非關(guān)聯(lián)流程 (out-of-context) 另有所用,它能讓子模塊像各 IP 一樣來運(yùn)作,因此需要更多手動(dòng)干預(yù),如創(chuàng)建模塊封裝文件和限定約束作用域。它也有助于改善編譯時(shí)間,如果您有靜態(tài)且無需更改的大型模塊,那么此流程能節(jié)省該模塊的最優(yōu)化時(shí)間。

可能影響增量綜合的因素:

采用此流程前,以下操作有助于您充分發(fā)揮增量流程的優(yōu)勢(shì):

選擇正確的檢查點(diǎn)。您需確保參考檢查點(diǎn)與受引導(dǎo)的設(shè)計(jì)處于同一器件內(nèi),綜合時(shí)采用的 Vivado 版本與當(dāng)前運(yùn)行采用的版本相同。不支持由不同版本生成的 DCP。最重要的是,參考 DCP 須在運(yùn)行同一綜合期間生成,并在 write_checkpoint 期間使用 -incremental_synth 開關(guān)來創(chuàng)建。

synth_design 設(shè)置應(yīng)始終保持不變,時(shí)序約束應(yīng)始終保持一致。

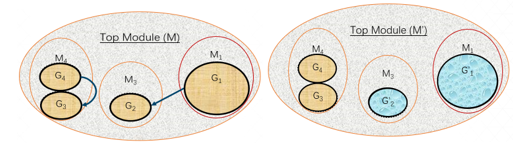

對(duì)受該流程影響的對(duì)象數(shù)量和跨邊界最優(yōu)化的數(shù)量加以限制,確保設(shè)計(jì)收斂的一致性和時(shí)序收斂。設(shè)計(jì)邏輯更改過多 (>50%) 可能導(dǎo)致更多模塊受到影響并且需要重新綜合,由此導(dǎo)致增加編譯時(shí)間或者引導(dǎo)的結(jié)果欠佳。

另外,如果少量設(shè)計(jì)更改引入了參考設(shè)計(jì)中不存在的新時(shí)序問題,則可能需要增加工作量和運(yùn)行時(shí)間,而且設(shè)計(jì)可能不滿足時(shí)序。下圖顯示了 M1 模塊和 M3 模塊間路徑因跨邊界最優(yōu)化而發(fā)生改變時(shí),這兩個(gè)模塊進(jìn)行重新綜合的方式。

盡可能將更改局限在單一模塊中,否則任何發(fā)生更改或消隱的分區(qū)都需重新綜合。另外,為了防止發(fā)生跨邊界最優(yōu)化,您可在層級(jí)模塊名稱上使用 PRESERVE_BOUNDARY 屬性,前提是您已寄存輸入/輸出模塊端口。例如:set_property BLOCK_SYNTH.PRESERVE_BOUNDARY 1 [get_cells [list {M1 M3}]]

圖:利用跨模塊最優(yōu)化情況下的綜合參考運(yùn)行對(duì)比增量運(yùn)行

如果在設(shè)計(jì)中多次例化某個(gè)設(shè)計(jì)模塊,那么該模塊中的任何小幅更改都會(huì)對(duì)模塊的例化次數(shù)產(chǎn)生巨大影響。在此情況下,就需要考量設(shè)計(jì)更改的總量。

就通過增量綜合可減少編譯時(shí)間的效果而言,大型設(shè)始終計(jì)比小型設(shè)計(jì)獲益更多。

生成增量編譯時(shí)間節(jié)省報(bào)告:

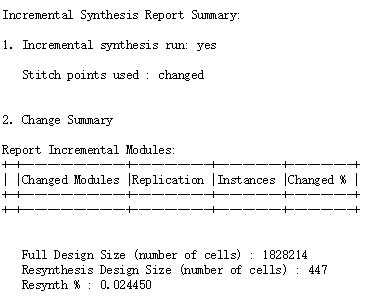

綜合運(yùn)行 log 日志中包含網(wǎng)表復(fù)用百分比的詳細(xì)信息。

在此示例中,僅對(duì)一個(gè)小型實(shí)例進(jìn)行了修改,如果更改發(fā)生在某個(gè)子模塊內(nèi),那么該表中也將列出該模塊的名稱。

總結(jié):

我們通過采用增量綜合流程可以快速完成綜合運(yùn)行的迭代。該流程設(shè)置方便,并且對(duì)于設(shè)計(jì)一致性和編譯時(shí)間節(jié)省都大有益處。

審核編輯:湯梓紅

-

DCP

+關(guān)注

關(guān)注

0文章

30瀏覽量

17513 -

編譯

+關(guān)注

關(guān)注

0文章

676瀏覽量

33788 -

GUI

+關(guān)注

關(guān)注

3文章

677瀏覽量

40811 -

腳本

+關(guān)注

關(guān)注

1文章

397瀏覽量

28365

原文標(biāo)題:開發(fā)者分享|節(jié)省編譯時(shí)間系列-使用增量綜合

文章出處:【微信號(hào):gh_2d1c7e2d540e,微信公眾號(hào):XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

淺析可提升Vivado編譯效率的增量編譯方法

fpga編譯綜合時(shí)間過長(zhǎng)?

誰能縮短大容量FPGA的編譯時(shí)間?增量式編譯QIC!

Vivado中的Incremental Compile增量編譯技術(shù)詳解

如何節(jié)省FPGA編譯時(shí)間?

Vivado Design Suite 2015.3新增量編譯功能介紹

引入增量編譯流程進(jìn)行調(diào)試的好處與步驟

Vivado 2015.3中的新增量編譯功能介紹

Vivado 2015.3的新增量編譯功能

講述增量編譯方法,提高Vivado編譯效率

Vivado綜合引擎的增量綜合流程

Vivadoz中增量編譯與設(shè)計(jì)鎖定

節(jié)省編譯時(shí)間系列-使用增量實(shí)現(xiàn)

Xilinx Vivado使用增量實(shí)現(xiàn)

Vivado那些事兒:節(jié)省編譯時(shí)間系列文章

使用增量綜合節(jié)省編譯時(shí)間

使用增量綜合節(jié)省編譯時(shí)間

評(píng)論