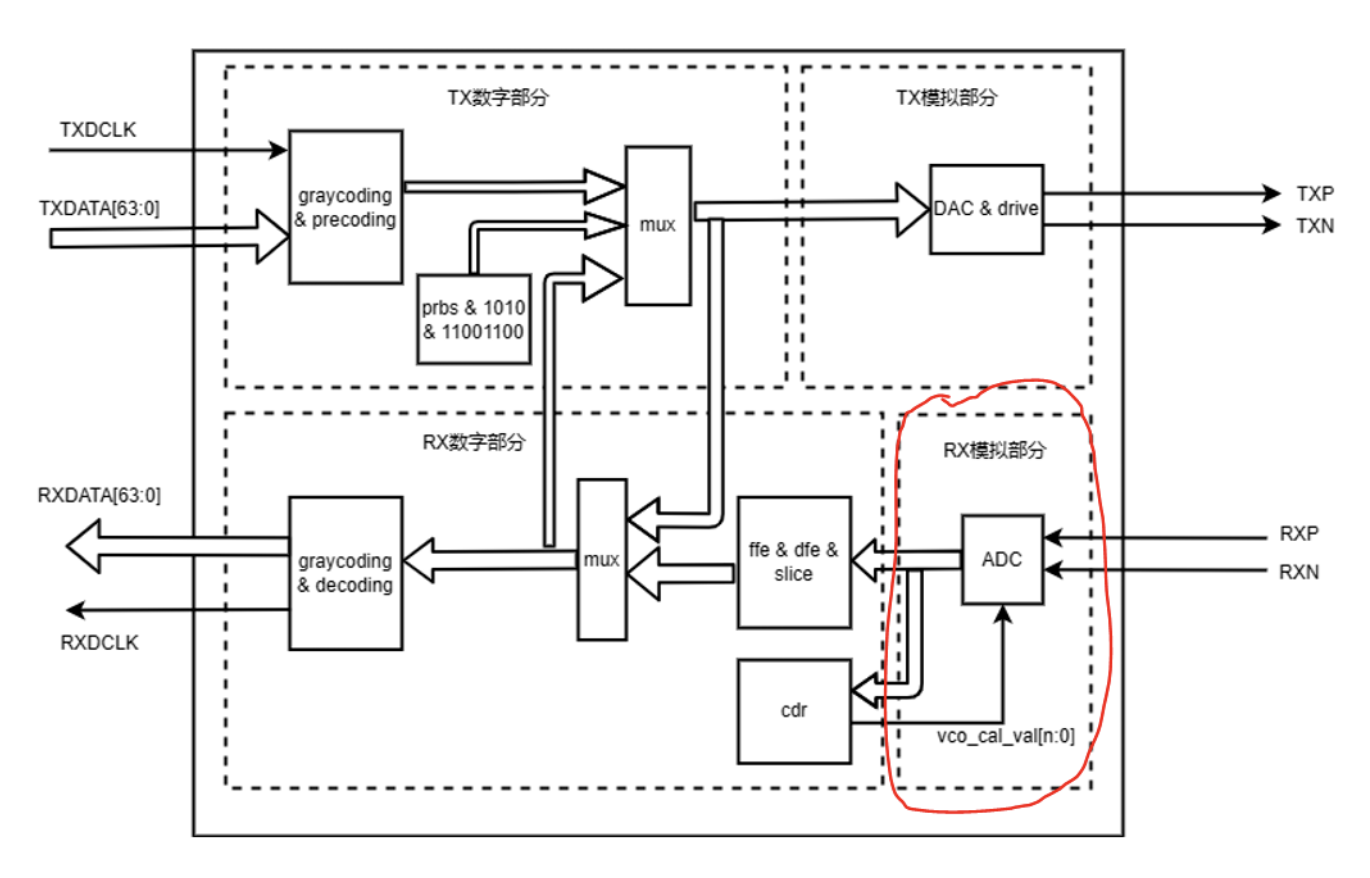

對于圖1所示TX/RX模擬部分的實現方式,大家是不是一直有這樣的疑問: Serdes在將并行data通過DAC串行發出去的時候,或者在接收端通過ADC進行串行data采樣的時候,是怎么實現的?比如56G的serdes就是用56G的ADC和DAC嗎?

答案是肯定不是,沒有那么高頻的ADC和DAC,通常ADC和DAC最大可以工作在1G頻率左右,再大的頻率無法實現精度的。所以采用多個ADC/DAC分時工作的模式。

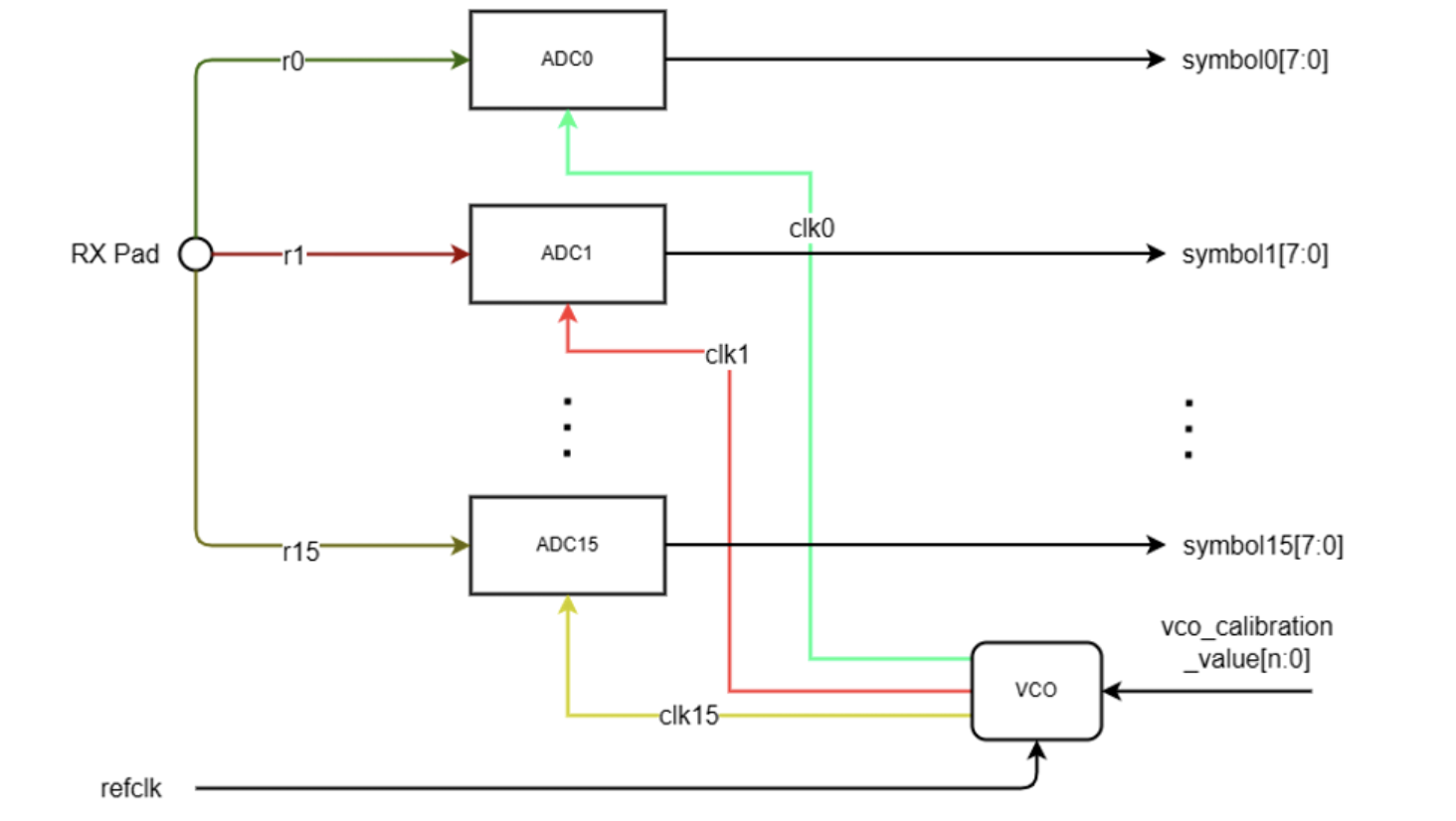

RX接收端采樣方式如下圖2,RX Pad連接到16個ADC上,后端要嚴格約束Pad到不同ADC之間的走線一樣長,可以通過繞線方式實現。

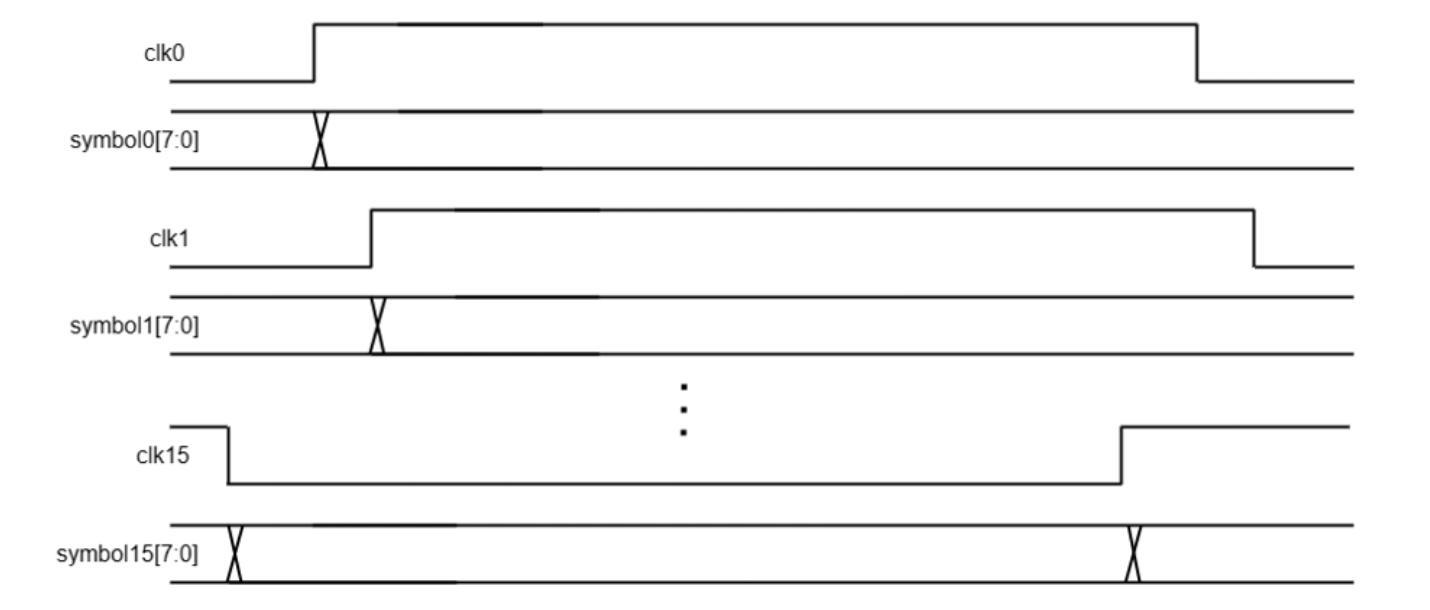

CDR的數字邏輯輸出vco_calibration_value[n:0]到模擬VCO實現相位調整。VCO輸出多路時鐘到多個ADC,如圖3所示,比如通過16個ADC分時采樣,VCO輸出的相鄰時鐘差90°/16。

ADC在時鐘上升沿進行采樣,然后模擬通過clk15將16個采樣symbol[7:0] pipe到數字邏輯,然后進行均衡判決。TX端的DAC發送端是相同的方式進行的。

圖1:serdes架構框圖

圖2:RX ADC采樣框圖

圖3:RX ADC采樣時鐘圖示

-

接收機

+關注

關注

8文章

1219瀏覽量

54261 -

adc

+關注

關注

99文章

6650瀏覽量

548388 -

時鐘信號

+關注

關注

4文章

466瀏覽量

29110 -

ADC采樣

+關注

關注

0文章

134瀏覽量

13142 -

VCO設計

+關注

關注

0文章

2瀏覽量

3544 -

SERDES接口

+關注

關注

0文章

28瀏覽量

3184

發布評論請先 登錄

從SerDes到SoC,全場景適配的FCom差分晶振設計全解

SERDES接口電路設計

FPGA SERDES接口電路怎么實現?

SERDES傳輸和引腳關聯

SerDes是怎么工作的

基于SERDES時鐘的頻率跟隨的設計

如何使用FPGA實現SERDES協議

serdes串行發送和接收是怎么實現的?serdes就是用56G的ADC和DAC嗎?

serdes串行發送和接收是怎么實現的?serdes就是用56G的ADC和DAC嗎?

評論