如果想用8層板甚至6層板的常規工藝完成LPDDR5 的設計,需要達到6400M 的速率,請問有什么好的優化建議?比如 PCB layout 及相關 SI/PI 的仿真。

答:1. 層次規劃——

如果只有6層板,盡量將信號層和電源層分開以減少干擾。8層板的話,還有更多的選擇,可以更好地分離信號和電源。

使用內層地層,通過地平面分割和補充來減少電磁干擾。

考慮使用分層板設計,以更好地管理信號的層間傳播。

2. 差分對與匹配——

確保差分對的長度匹配,以減少時序偏差。

使用差分對匹配的設計規則,以確保信號一致性。

考慮使用嵌套差分對,以減小差分對之間的互引。

3. 信號完整性——

使用信號完整性仿真工具——Sigrity Topology Workbench,Sigrity SystemSI 來仿真信號的傳輸和波形。

在設計中使用端接電阻和電容來控制信號的波形。

使用合適的阻抗確保信號傳輸路徑的阻抗連續性。

4. 電源完整性——

對于 LPDDR5,電源完整性至關重要。確保電源線路穩定,噪聲低。

使用適當的電源電容和電感來穩定電源供電。

5. 布局和連接——

盡量減少長距離的高速信號路徑。

為關鍵信號提供獨立的地線或電源線。

避免信號穿越分割平面。

6. 信號引腳和分層——

在 PCB 布局中,將關鍵信號引腳放置在靠近內部地層的位置,以減少信號的回流路徑。

使用分層布局,將不同的信號類別(如時鐘、數據、控制信號)放在不同的層上,以減小互引。

7. 串擾和 EMI 抑制——

使用差分信號和屏蔽層來減小串擾。

在設計中考慮電磁干擾(EMI)抑制,使用合適的濾波器和抑制措施。

8. 盡早進行仿真——

在PCB設計的早期階段就進行信號完整性和電源完整性的仿真,以發現潛在問題并進行修復。

9. 遵循 LPDDR5 規范——

詳細研究 LPDDR5 的規范,確保設計符合標準要求。

Q

BGA 的位置布局是否允許布置在板子的對角線交叉點上?

答:一般不能這樣做。BGA(Ball Grid Array)的位置布局并不一定不允許布置在板子的對角線交叉點上。BGA 是一種表面貼裝技術,其中芯片引腳以球狀焊點的形式排列在芯片的底部,然后與印刷電路板(PCB)上的焊盤相匹配。BGA 的布局通常是根據設計需求和特定應用來確定的。在某些情況下,將BGA布局在板子的對角線交叉點上可能是合理的,特別是當需要將多個 BGA 器件集中在一起并優化空間利用時。然而,這種布局可能會增加布線的復雜性,因為需要確保各個 BGA 器件之間的連接不會交叉干擾。

總之,BGA 的位置布局應根據具體的項目需求、信號完整性和電路布局來決定,沒有絕對的規定要求不允許將它們布置在板子的對角線交叉點上。設計工程師通常會根據特定的情況來選擇最合適的 BGA 布局方式。

Q

差分走線兩側必須要進行包地嗎?另外像 HDMI(High-Definition Multimedia Interface)、DP(DisplayPort)等里面的多組差分線之間有等長要求嗎?

答:差分信號的兩側通常需要進行包地,這有助于維護信號完整性,降低電磁干擾,以及提高抗干擾性能。包地是指在差分信號的兩側分別布置一個地層,這個地層通常與信號層平行,并與信號引腳或信號軌道之間保持一定的間距。包地可以幫助控制信號的返回路徑,減小信號引腳之間的串擾,提供更好的信噪比和抗干擾性。

對于像 HDMI 和 DP 等高速數字接口,通常有等長要求。等長要求是指差分對中的正信號和負信號在傳輸過程中需要保持大致相同的長度,以確保信號到達目的地時能夠正確對齊。這有助于減小信號引腳之間的時間差,降低時鐘抖動和串擾的風險。

要滿足等長要求,設計工程師通常需要采取以下措施:

確保差分信號的路徑長度相等,包括信號軌道、信號引腳的長度等。

使用特定的布線規則和技術,如微帶線或差分對的匹配線。

在PCB設計中考慮差分信號的路徑,避免彎曲和不必要的路徑延遲。

使用差分對的長度匹配工具來幫助設計等長的信號路徑。

綜上所述,包地和等長要求都是確保高速差分信號傳輸的關鍵因素,特別是在數字接口和高頻應用中。設計工程師應該仔細考慮這些要求,以確保信號完整性和可靠性。

Q

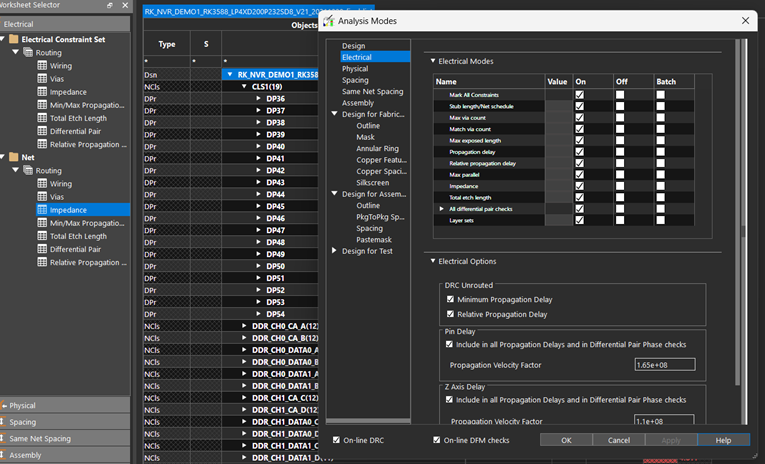

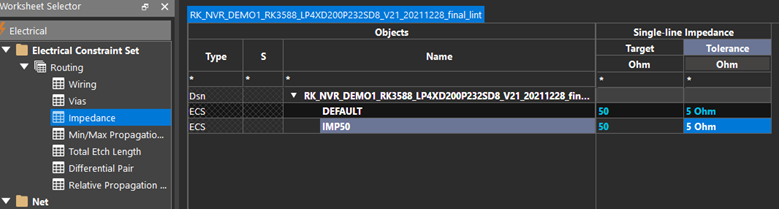

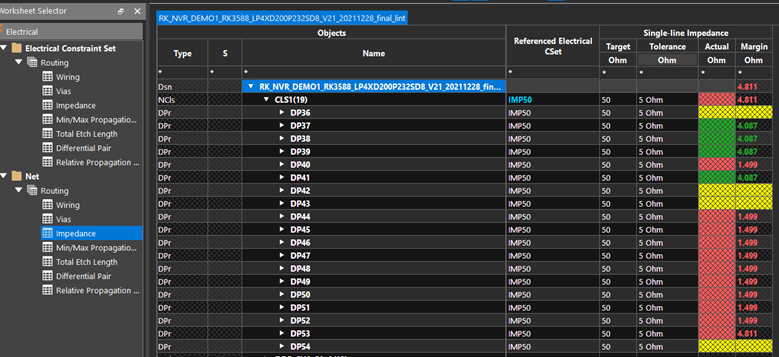

如何設置走線的阻抗匹配?

答:

設置設計規范:在開始走線之前,需要確定設計規范中所要求的阻抗值。這通常包括差分對和單端信號線的阻抗要求。

創建信號線類別:在 Allegro 中,可以為不同的信號線創建不同的類別,并為每個類別設置特定的阻抗值和寬度。可以在 Design Constraints Manager 中進行設置。

分配信號線到類別:將不同的信號線分配到相應的類別中。這可以通過在 PCB Editor 中選擇信號線并應用相應的類別進行實現。

設置差分對:對于差分信號線,需要在 PCB Editor 中設置差分對。選擇兩條差分信號線并指定它們是一個差分對。然后,可以為差分對設置特定的阻抗要求。

調整線寬和間距:根據設計規范中的阻抗要求,可以在 PCB Editor 中調整信號線的線寬和間距。Allegro 提供了自動線寬和間距計算的功能,可以根據所選的類別和阻抗要求進行計算和調整。

仿真和驗證:在完成布線后,可以使用 Allegro 中的仿真工具來驗證信號線的阻抗匹配情況,進行電磁仿真或者使用信號完整性工具來檢查阻抗是否滿足設計要求。

Q

等長蛇形布線如何實現?

答:

創建信號線:在 Allegro PCB Editor 中,選擇"Route"工具,并創建起始和終止點,即信號線的路徑。

設置布線規則:在 Design Constraints Manager 中,設置布線規則,包括信號線的最小間距、最小線寬和最小電子間距等。確保規則中沒有設置阻止使用蛇形布線的限制。

使用蛇形布線工具:在 PCB Editor 中,選擇"Route"工具,然后選擇蛇形布線工具。這通常在工具欄中有一個相應的圖標。或者通過右鍵單擊并選擇"Route"->"Snake"來啟用蛇形布線。

設置蛇形布線參數:在啟用蛇形布線后,可以設置一些參數,如蛇形的寬度、蛇形的間距、起始和終止點之間的連接方式等。根據設計需求和布線規則,調整這些參數以獲得所需的布線結果。

進行蛇形布線:選擇起始和終止點,并在 PCB Editor 中繪制信號線的路徑。根據所設置的蛇形布線參數,Allegro 會自動在路徑上生成等長的蛇形布線。

調整布線:根據需要,可以在完成蛇形布線后對信號線進行微調和調整,以保證布線的質量和滿足設計規范。

Q

走線如何設置能夠實現走線兩邊的等間距?

答:

打開 Allegro PCB Editor

設置間距規則:在Design Constraints Manager中,設置走線間距的規則。選擇"Placement" -> "Spacing",然后設置所需的間距值。確保選擇的規則適用于想要實現等間距的走線。

執行自動布線:選擇"Route"工具,并從工具欄中選擇適當的自動布線選項,如"Auto Route"或"Interactive Auto Route"。這將自動進行走線。

調整布線參數:在自動布線完成后,可以進一步調整布線參數以實現等間距。例如,可以選擇調整線寬、間距或其他布線設置來使兩邊的間距保持一致。

手動調整走線:如果自動布線不能滿足等間距要求,可以手動調整走線。使用"Route"工具,選擇要調整的走線,并使用拖動或拉伸的方式來調整走線的位置和間距。

驗證等間距:在完成布線后,使用Allegro中的驗證工具來確保走線兩邊的間距保持一致。可以使用信號完整性工具或進行電磁仿真來檢查等間距的走線是否滿足規范要求。

Q

弧度走線和切角走線在信號質量上有什么區別?什么信號必須走弧度線?

答:弧度走線:弧度走線是指在轉彎處使用圓弧來連接信號線的走線方式。它可以減少信號線的輻射損耗和反射,提高信號的傳輸質量。弧度走線可以平滑信號線的轉彎,減少信號在轉彎處的信號失真和耦合噪聲。因此,弧度走線可以改善信號的完整性和減少信號的傳輸損耗。

切角走線:切角走線是指在信號線的轉彎處使用直角或尖角的走線方式。切角走線相對于弧度走線來說,信號線在轉彎處會存在更多的輻射損耗和反射。這可能導致信號失真、串擾和信號完整性的問題。因此,在高速信號傳輸或對信號完整性要求較高的應用中,切角走線可能會對信號質量產生負面影響。

信號需要走弧度線:一般來說,在高速信號傳輸中,特別是對于高頻信號或差分信號,走弧度線可以提高信號的傳輸質量。這是因為走弧度線可以減少信號的輻射損耗、反射和串擾噪聲,從而減少信號失真和完整性問題。

Q

繞線線間距設置多少是最優?是否有計算線間距的公式或指導規范?

答:在 PCB 設計中,線間距的最優設置取決于許多因素,包括電壓等級、信號速度、環境條件和制造工藝等。沒有一個通用的公式或規范來確定最優線間距,因為每個設計都有其獨特的需求和約束。

然而,通常有一些常見的準則可以參考。例如,根據 IPC-2221 標準,對于一般電路板設計,常見的線間距可以設置為信號線寬度的3至5倍。這個范圍可以提供足夠的絕緣距離,以減少電氣干擾和串擾的風險。

此外,一些高速信號傳輸標準,如 USB、HDMI 和 Ethernet,也提供了特定的線間距要求。這些標準通常會考慮信號的特性和干擾抑制的需求,因此在設計這些類型的電路板時應該遵循相應的規范。

總之,為了確定最優的線間距,應該考慮設計的具體要求、標準規范和制造工藝,并與PCB制造商或專業工程師進行詳細討論和評估。

Q

軟硬結合板疊層如何設置?

答:

打開 Allegro 軟件,并創建一個新的設計文件。

在設計文件中,選擇“Design” -> “Stackup Editor”來打開疊層編輯器。

在疊層編輯器中,添加和編輯板層。點擊“Add Layer”按鈕來添加新的板層。

對于硬結合板,可以添加銅層、介質層和襯底層。對于軟結合板,可以添加柔性電路層、柔性介質層和柔性襯底層。

在每個層中,可以設置層的名稱、厚度、材料和其他屬性,并選擇預定義的材料或自定義材料。

對于硬結合板,還可以定義導線層、地平面層和其他特殊層。

通過拖放和調整層的順序,定義疊層中各個層的堆疊順序和位置。

完成疊層設置后,保存并關閉疊層編輯器。

請注意,設置軟硬結合板疊層時,應該根據設計要求、制造要求和供應商要求進行設置。確保疊層設置符合設計規范和標準,并能夠滿足電路板的電氣和機械性能要求。

Q

如何設置規則設置中 neck 的 min width 和 max width?

答:在 Allegro 軟件中,"neck"是指電路板中兩個不同寬度的導線之間的過渡區域。設置"neck"的最小寬度和最大寬度可以確保過渡區域的寬度在規定的范圍內,以滿足設計要求和制造能力。

要設置"neck"的最小寬度和最大寬度,請按照以下步驟進行操作:

在 Allegro 軟件中打開設計文件。

在軟件界面的菜單欄中,選擇"Setup" -> "Design Parameters",打開設計參數設置對話框。

在設計參數設置對話框中,選擇"Routing"選項卡。

在"Routing"選項卡中,找到"Minimum Neck Width"和"Maximum Neck Width"兩個參數。

輸入適當的數值以設置"neck"的最小寬度和最大寬度。這些數值應該根據設計要求和制造能力進行選擇。通常,最小寬度應該滿足電路板制造商的要求,并且最大寬度應該在可接受的范圍內以避免過度的寬度差異。

點擊"OK"按鈕保存設置并關閉設計參數設置對話框。

請注意,"neck"的最小寬度和最大寬度應該根據具體的設計要求和制造能力進行設置。這些數值可能會因設計規范、信號類型、板厚和制造工藝等因素而有所不同。

Q

SATA 信號線必須圓弧走線的好處是什么?

答:

信號完整性:圓弧走線可以減少信號線的反射和串擾干擾。通過使用圓弧走線,可以減少信號線邊緣的快速變化,降低信號的噪聲和失真,從而提高信號的完整性和穩定性。

信號匹配:圓弧走線可以提供更好的阻抗匹配,確保信號線和其周圍環境之間的阻抗一致。這有助于減少信號的反射和信號質量的損失,提高信號傳輸的可靠性和性能。

電磁兼容性:圓弧走線可以減少信號線之間的電磁耦合和輻射。通過合理設計圓弧走線,可以降低信號線之間的干擾,提高系統的抗干擾能力,減少電磁輻射對其他設備的影響。

機械可靠性:圓弧走線可以減少對信號線的應力和損壞。通過使用圓弧走線,可以減少信號線的彎曲和拉伸,降低信號線斷裂和損壞的風險,提高電路板的機械可靠性和壽命。

總之,圓弧走線在 SATA 信號線設計中可以提供更好的信號完整性、信號匹配、電磁兼容性和機械可靠性。這些優勢有助于確保 SATA 接口的高質量信號傳輸和可靠性。因此,在設計SATA接口時,建議使用圓弧走線來優化信號線的布局和傳輸性能

-

pcb

+關注

關注

4355文章

23436瀏覽量

407115 -

布線

+關注

關注

9文章

794瀏覽量

84929 -

布局

+關注

關注

5文章

272瀏覽量

25292

發布評論請先 登錄

時源芯微 PCB 布線規則詳解

如何布線才能降低MDDESD風險?PCB布局的抗干擾設計技巧

解決噪聲問題試試從PCB布局布線入手

串行接口PCB設計指南:優化布局與布線策略

高速ADC PCB布局布線技巧分享

PCB布局、布線、規則設計的高級技巧

PCB布局、布線、規則設計的高級技巧

評論