隨著薄膜晶體管液晶顯示器的迅速發展,產品高分辨率、廣視角、高響應速度 、 高開口率等需求對器件的顯示質量提出了更高的要求。而伴隨著像素尺寸變小, 線間距越來越小, 當信號線上有電流通過時,線間感應電場的千擾變得尤為突出,像素之間的合加劇,這些都會導致串擾現象的發生,大大影響了產品良率和顯示效果。所以串擾對來說,是一個急需解決的重大問題

串擾的定義及分類

在薄膜晶體管液晶顯示器中,人們將串擾定義為整個屏幕中某一區域的顯示會受到另一區域的影響,而造成畫面失真的一種顯示異常的現象。但是由于人眼對顯示屏幕不同亮度的敏感度不同,只有在某些灰階背景下,串擾現象才能夠較容易地觀察出來。

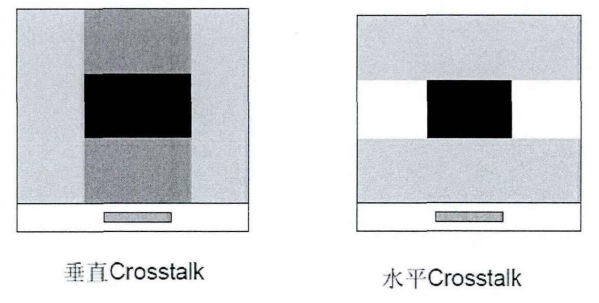

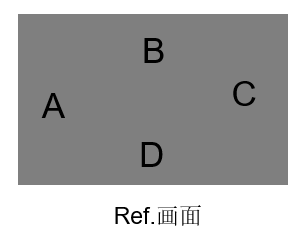

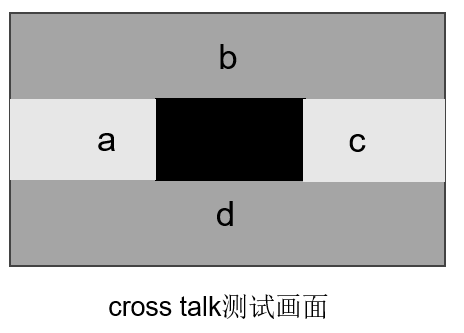

串擾常見的有兩種分別稱為垂直串擾和水平串擾。如下圖所示,背景為46 灰階,中間為黑色方塊。黑色方塊的周邊區域根據位置可以分為上、下、左、右四個區域。當上、下區域受到黑色區域的影響而變的比背景更暗時,稱為垂直串擾。同理,當左、右區域受到黑色區域的影響變的比背景更亮時,稱為水平串擾。

(串擾比較容易發生在列反轉、頓反轉、com反轉模式中,而在目前常用的點反轉模式中出現較少)

水平串擾產生的原因

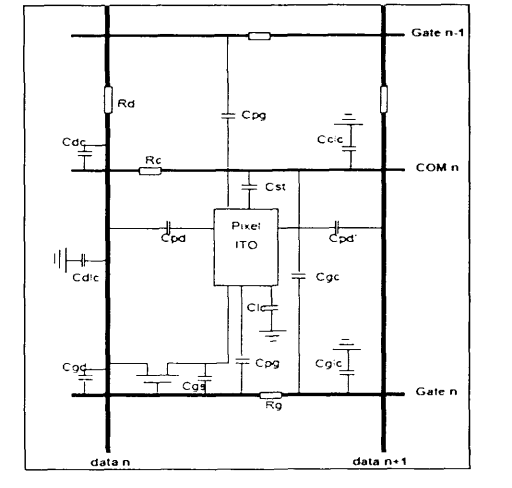

TFT面板在上板共電極與 TFT 面電容除了像素ITO與上板ITO電極形成的液晶電容以外,還有數據線和掃描線與上板電極形成的寄生電容,見下圖。

上板共電極其實是一個 RC 延時很大的電阻-電容網絡,當數據線電壓變化時,便會經由數據線與上極板形成的寄生電容,影響到上極板共電極電位,由于上極板電阻很大,沒辦法短時間內消除電位變化的影響,恢復不到設定的電壓,便會形成串擾。

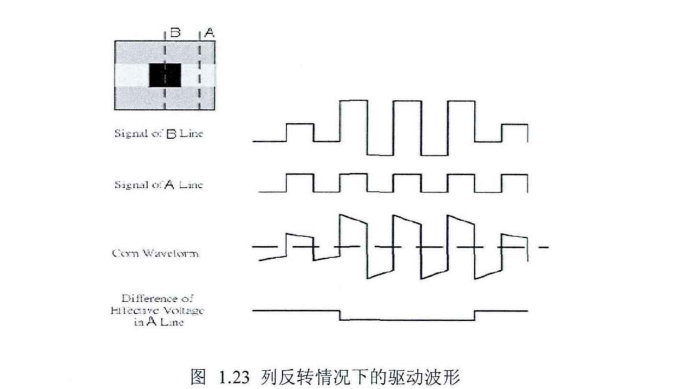

對列反轉的情況下,如圖 1.23。如果 A、B 兩條信號加的電壓不同,這時 B上的信號會通過 Com 電極合到A 信號線上,使得 A列的像素電壓異常,不能顯示正常灰階,導致水平串擾。

垂直串擾產生的原因

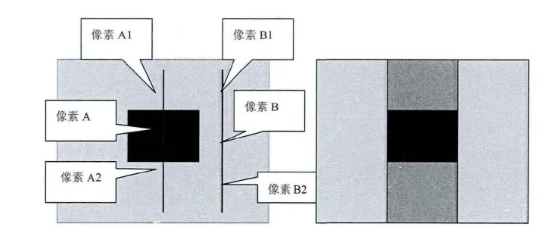

在共電極結構中,像素電極本身和下一條數據線間存在寄生電容,如下圖所示。數據線上信號的變化會經由這些電容耦合到下一個數據線,引起下一個數據線上連接的子像素行成串擾。

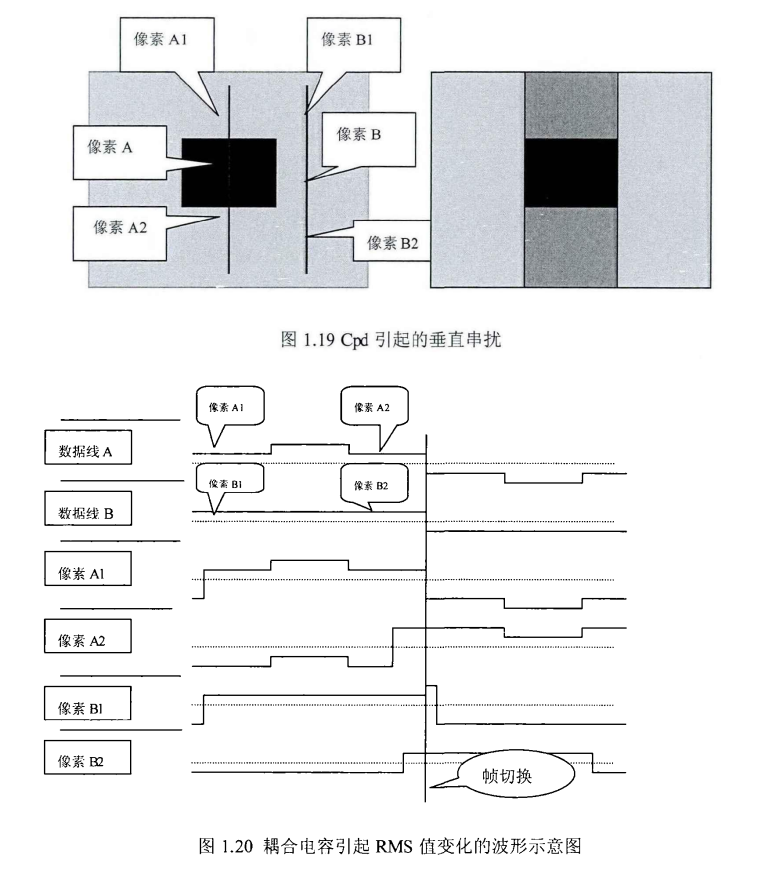

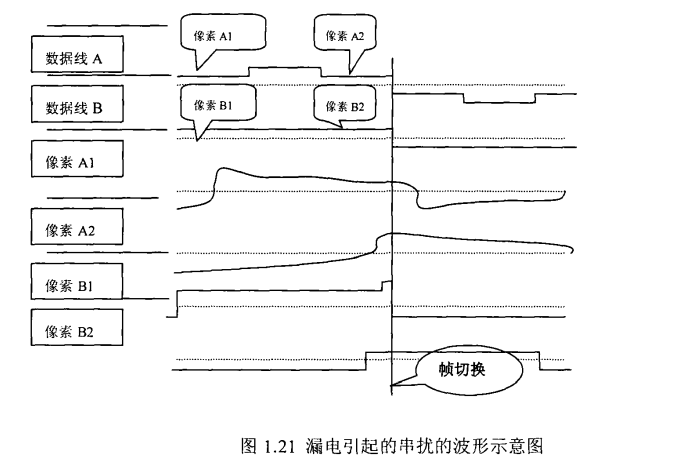

在幀反轉中,參考波形圖 1.20,像素 A1 和A2與B1和 B2上的電壓波形會有所差別。像素 B1、B2 顯示的灰階是相同的,但是 Vms 值比較會發現: A1會比B1的Vrms 值大,所以A1 會顯示的灰階比較深,而A2會比 B2的 Vms 值小,所以顯示的灰階值較淺。最終出現如圖 1.19 的串擾。

Vrms 也稱液晶的有效電壓,液晶屏的透過率和相應時間都是與它直接相關的。

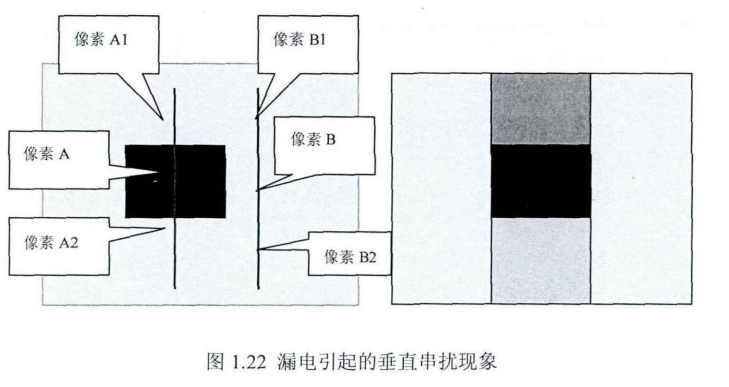

除了寄生電容能引起垂直串擾以外,還有一個因素也是不能忽略的,那就是漏電過大。不難想象,如果 TFT 漏電過大,加在存儲電容上的電壓會漏到信號線上而使存儲中容的電壓改變,但由于 A、B 兩列信號線上加的電壓不同,最后導致的像素電壓 Vms 值也會不同,造成串擾現象,信號波形描述示意圖如圖 1.21

水平串擾的改善方法

水平串擾的主要原因是共電極的延遲,參考共電極延遲的計算公式可知,可以從減小共電極電阻及共電極耦合電容兩方面來對水平串擾進行改善。

降低共電極的電阻,可以采用如下方法:

1.在布線空間允許情況下,將 Vcom ITO線寬做到最大

2增加Vcom ITO電極的膜厚;

3.采用具有更小Rs的透明材料取代ITO 材料,如IZO

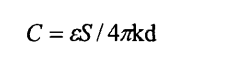

電容方面,已知平板電容的決定式為:

其中S為兩板正對面積,ε為介電常數,k為靜電常量,d為兩極板之間的距離從該公式可知,減小電容需從減小交疊面積S和增大兩極板距離d兩方面進行。

垂直串擾的改善方法

造成垂直擾的主要因素是數據線對像素電極的合電容Cpd 以及像素 TFT 的漏電。因此,要改善垂直串擾,就需要找到數據線與像素電極之間的最佳距離,在不損失開口率的情況下降低數據線對像素電極的耦合影響;同時從TFT的開關特性出發,控制影響TFT 電的因素。

減小Cpd耦合電容:

(1)從設計上,需保證數據線與像素 ITO之間的距離為 6um 以上(其中包含了 2.5m 的工藝波動),對 IPS型TFT-LCD,還需讓 Vcom ITO到數據線的距離在 3.5um 以上(其中包含了25um的工藝波動)。而針對不同的生產線,設計人員需要綜合考慮所在產線的工藝波動、S/D 及 ITO線寬和位置的波動,從而敲定這兩個距離的大小。

然而,隨著分辨率和開口率的提高,且顯示屏的邊框越來越窄,設計時無法給數據線和像素ITO之間留出足夠的距離,因此需考慮能夠更好地屏蔽數據線對像素ITO電場干擾的方法。

對于IPS 型TFT-LCD,可以在 S/D 層上增加一層樹脂(Resin)層,該 Resin 層同樣可以起到屏蔽數據線電場干擾的作用。另外,也可以在掃描線下方增加一條Vcom金屬線,該層金屬與掃描線為同一層,并與TFT基板上的VcomITO導通。像素ITO 與該 Vcom 金屬有交疊,因此可以形成存儲電容 Cst。這樣將Cst進一步增大,降低合電容 Cpd在總電容 Cta中的比例,減小因 Cpd而造成的影響,從而規避串擾不良的產生。

減小漏電流:

(1)在設計上,需要減小有源層面積,使其被包裹在柵極基臺內,避免受到光照和溫度的影響。將柵極關斷電壓設置在-10.5V 左右。另外也可以采用雙有源層結構、雙柵結構來提高 TFT 的關態特性。

(2)在工藝上,可以減小有源層厚度來優化 TFT 關態特性,同時也必須提高對位精度,嚴格管控有源層在工藝上的偏移。

串擾的計算方法

Cross talk計算公式:MAX(abs((A-a)/A);abs((B-b)/B);abs((C-c)/C);abs((D-d)/D))

選取最大值為最終測試結果。

注:Abs為絕對值函數。

審核編輯:劉清

-

lcd

+關注

關注

34文章

4520瀏覽量

171643 -

TFT

+關注

關注

10文章

399瀏覽量

112599 -

寄生電容

+關注

關注

1文章

299瀏覽量

19801 -

薄膜晶體管

+關注

關注

1文章

30瀏覽量

9980 -

VMs

+關注

關注

0文章

5瀏覽量

5316

原文標題:LCD串擾(Crosstalk)基礎知識

文章出處:【微信號:心植桂冠,微信公眾號:心植桂冠】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

LCD串擾的定義及分類 垂直串擾產生的原因有哪些

LCD串擾的定義及分類 垂直串擾產生的原因有哪些

評論