本文章是接上期《鎖相環(huán)中的相位噪聲建模、仿真和傳播(一)》的第二部

本文要點(diǎn)

該文章是關(guān)于頻率合成器的設(shè)計(jì)和分析的,重點(diǎn)討論了相位噪聲和頻率噪聲的測(cè)量和分析方法。

文章介紹了PLL頻率合成器的一般設(shè)計(jì)過(guò)程,包括選擇電路配置、選擇元件和開環(huán)傳遞函數(shù)的建立。

接下來(lái)的步驟包括模擬器和實(shí)際電路的搭建與測(cè)試,并對(duì)模型和實(shí)際性能進(jìn)行比較和調(diào)整。

本文摘要

本篇文章是關(guān)于相位鎖定環(huán)(PLL)頻率合成器的設(shè)計(jì)和分析,重點(diǎn)討論了相位噪聲和頻率噪聲的測(cè)量、建模和仿真方法。文章以設(shè)計(jì)一個(gè)假想的PLL頻率合成器為例,詳細(xì)介紹了設(shè)計(jì)過(guò)程和步驟。從規(guī)格選擇、電路配置到元件選擇和相噪模型的建立,文章提供了一套完整的設(shè)計(jì)流程。通過(guò)建模和仿真,可以評(píng)估設(shè)計(jì)的性能并進(jìn)行優(yōu)化。最后,文章還介紹了如何根據(jù)模型和實(shí)測(cè)數(shù)據(jù)進(jìn)行參數(shù)調(diào)整,以實(shí)現(xiàn)設(shè)計(jì)的要求和性能。

如第 一 部分所述,鎖相環(huán) (PLL) 在當(dāng)今的高科技世界中無(wú)處不在。幾乎所有商業(yè)和軍用產(chǎn)品都在其運(yùn)行中使用它們,并且相位(或 PM)噪聲是一個(gè)主要問(wèn)題。頻率(或 FM)噪聲密切相關(guān)(瞬時(shí)頻率是相位的時(shí)間導(dǎo)數(shù)),通常被認(rèn)為是在相位噪聲的范疇內(nèi)(也許兩者都可能被視為“角度噪聲”)。幅度(或 AM)噪聲是另一個(gè)考慮因素。

雖然兩者都會(huì)影響 PLL 性能,但幅度噪聲通常是自限性的,不會(huì)產(chǎn)生任何后果。因此,PLL 輸出和 RF 組件的相位噪聲是主要問(wèn)題。當(dāng)然,輸出相位噪聲是最終關(guān)注的問(wèn)題,并且很大程度上取決于每個(gè)組件的相位噪聲。造成組件相位噪聲的因素有很多,例如電源、EMI 和半導(dǎo)體異常等,了解這些因素使我們能夠?qū)嵤┙M件相位噪聲的緩解策略,并最終實(shí)現(xiàn)輸出相位噪聲的緩解策略。

第 1 部分討論了相位噪聲的簡(jiǎn)要理論和典型測(cè)量及其分析(建模、仿真和傳播),并展示了大多數(shù)計(jì)算機(jī)輔助設(shè)計(jì) (CAD) 應(yīng)用程序使用的方法。第 2 部分深入研究用于分析的假設(shè) PLL 頻率合成器的設(shè)計(jì)。

8 至 12 GHz 輸出/50 MHz 步進(jìn) PLL 頻率合成器的設(shè)計(jì)

為了演示第 1 部分中回顧的概念和方法,我們?cè)O(shè)計(jì)了一個(gè)假設(shè)的單環(huán) 8 至 12 GHz/50 MHz 步長(zhǎng)(通道間隔)整數(shù)合成器,具有 25 MHz 參考(50 MHz 是可實(shí)現(xiàn)的最小步長(zhǎng),因?yàn)椋雇磥?lái),我們將使用固定模數(shù)除以 2 預(yù)分頻器)。它將通過(guò)在 10 GHz 中頻輸出處實(shí)現(xiàn)最低相位噪聲來(lái)設(shè)計(jì),以實(shí)現(xiàn)整個(gè)頻段內(nèi)最低的平均輸出相位噪聲。我們遵循標(biāo)準(zhǔn)的設(shè)計(jì)程序:

1. 審查規(guī)格。

對(duì)于此示例,唯一的規(guī)范是如上所述的相位噪聲(對(duì)于此示例明確的不切實(shí)際的過(guò)度簡(jiǎn)化)。

2. 選擇電路配置、類型、順序和環(huán)路濾波器拓?fù)洹?/strong>

離散(而不是 I2C 或混合)配置、類型 2、二階和一階有源 PI 環(huán)路濾波器(因其簡(jiǎn)單和流行而選擇)。

3. 選擇組件。

參考:著名電子制造商的 100 MHz OCVCXO (圖 5 和 6

5. 制造商提供的 8 至 12 GHz 輸出/50 MHz 步進(jìn) PLL 頻率合成器的參考 (100 MHz OCVCXO) 數(shù)據(jù)表。

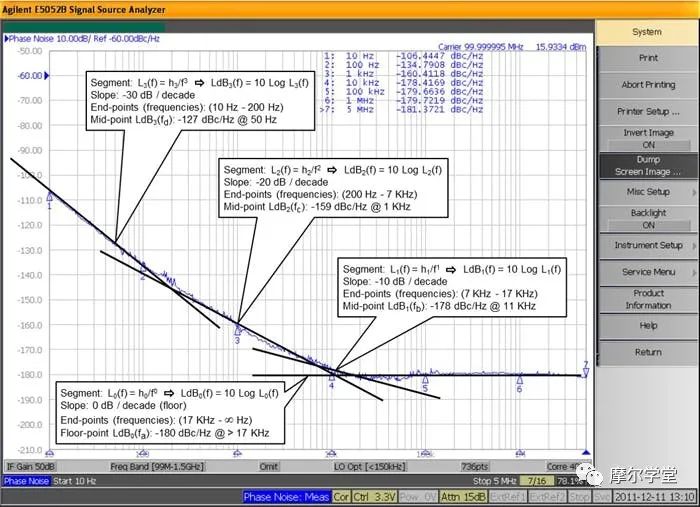

6. 參考 (100 MHz OCVCXO) 相位噪聲圖(圖 5)與通用相位噪聲模型(第 1 部分中的圖 3)適合 8 至 12 GHz 輸出/50 MHz 步進(jìn) PLL 頻率合成器的圖。

參考分頻器:著名電子制造商的可編程整數(shù)分頻器,范圍 K r(= 1/R) = 1/1 至 1/17 (R = 1 至 17) 編程為:

在所有 GHz 下 R = 4。

反饋分頻器:著名電子制造商的可編程整數(shù)/小數(shù)分頻器,用于整數(shù)模式,范圍 K m(= 1/M) = 1/32 至 1/1048575 (M = 32 至 1048575) 編程為:

8 GHz 時(shí) M = 160

9 GHz 時(shí) M = 180

10 GHz 時(shí) M = 200

11 GHz 時(shí) M = 220

12 GHz 時(shí) M = 240

預(yù)分頻器:著名電子制造商的固定模數(shù)除以 2 預(yù)分頻器,K p(= 1/P) = 1/2 (P = 2) 給出總反饋因子 Kn(=1/N) = 1/MP (N =MP) 生產(chǎn):

在所有 GHz 下 P = 2

N = MP = 320(8 GHz)

N = MP = 360(9 GHz)

N = MP = 400(10 GHz)

N = MP = 440(11 GHz)

12 GHz 時(shí) N = MP = 480。

VCO:著名電子制造商的 8 至 12.5 GHz 低噪聲 VCO 11,具有:

8 GHz 時(shí)Kv= 900 MHz/V [5.7(109) rad/S/V]

9 GHz 時(shí)Kv= 825 MHz/V [5.2(109) rad/S/V]

10 GHz 時(shí)Kv= 725 MHz/V [4.6(109) rad/S/V]

11 GHz 時(shí)Kv= 540 MHz/V [3.4(109) rad/S/V]

12 GHz 時(shí)Kv= 375 MHz/V [2.4(109) rad/S/V]

相位檢測(cè)器:著名電子制造商的相位/頻率檢測(cè)器 (PFD),帶有增益控制電路,可補(bǔ)償整個(gè) VCO 頻段的Kv變化(保持 KψKv= 恒定),從而產(chǎn)生有效的:

Kφ= 0.134 V/rad(8 GHz)

9 GHz 時(shí)Kφ = 0.147 V/rad

10 GHz 時(shí)Kφ = 0.166 V/rad

11 GHz 時(shí)Kφ= 0.225 V/rad

12 GHz 時(shí)Kφ= 0.318 V/rad

環(huán)路濾波器/誤差放大器:著名電子制造商的運(yùn)算放大器(具有足夠的增益、精度、噪聲、帶寬、穩(wěn)定性、電源要求和輸出電壓/電流驅(qū)動(dòng)能力)。

4. 開發(fā)射頻組件的相位噪聲模型。

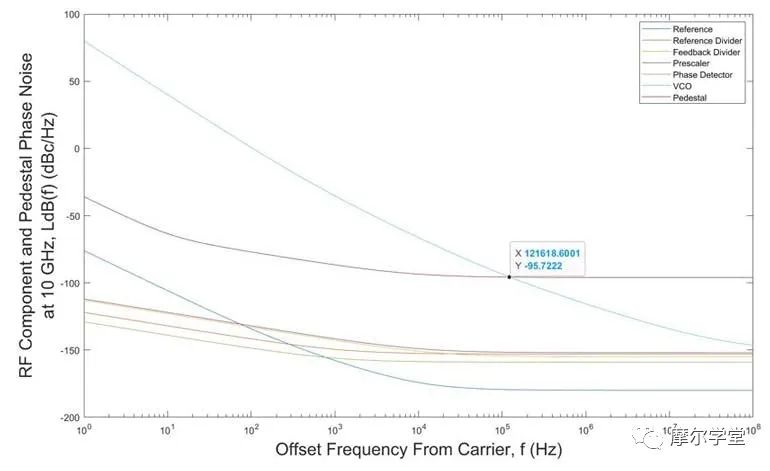

我們使用相位噪聲分析程序(第 1 部分)的步驟 1 至 6 來(lái)開發(fā) RF 組件相位噪聲模型并在圖 7中對(duì)其進(jìn)行仿真。我們展示了參考的完整開發(fā)過(guò)程,包括適合其數(shù)據(jù)表相位噪聲圖(圖 5 和 6)的通用相位噪聲模型(圖 3,第 1 部分)以及其計(jì)算和生成的特定相位噪聲模型。

7. 10 GHz 中頻輸出處的 RF 分量和基座相位噪聲顯示了8 至 12 GHz 輸出/50 MHz 步進(jìn) PLL 頻率合成器的 VCO/基座交叉處的最佳環(huán)路帶寬 fg 。

對(duì)于其他組件,為了簡(jiǎn)潔起見,我們僅顯示它們的計(jì)算和由此產(chǎn)生的特定相位噪聲模型(此外,為了簡(jiǎn)單起見,沒(méi)有對(duì)環(huán)路濾波器/誤差放大器進(jìn)行建模,因?yàn)樗皇巧漕l組件,并且其分析比射頻組件1):

A. 參考(100 MHz)

相位噪聲模型點(diǎn)LdBj(fk),從將通用相位噪聲模型擬合到數(shù)據(jù)表圖:

地板段:0 dB/dec (17 kHz - ∞ Hz)

底點(diǎn):LdB 0(fa) = ?180(17 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-18.0(17 kHz) (伏特比2/Hz)

閃爍段:?10 dB/dec (7 kHz - 17 kHz)

中點(diǎn):LdB 1(fb) = ?178(11 kHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-17.8(11 kHz) (伏特比2/Hz)

閃爍段:?20 dB/dec (200 Hz - 7 kHz)

中點(diǎn):LdB 2(fc) = ?159(1 kHz) (dBc/Hz)

L2(fc) = 10LdB2/10= 10-15.9(1 kHz) (伏特比2/Hz)

閃爍段:?30 dB/dec (10 Hz - 200 Hz)

中點(diǎn):LdB 3(fd) = ?127(50 Hz) (dBc/Hz)

L3(fd) = 10LdB3/10= 10-12.7(50 Hz) (伏特比2/Hz)

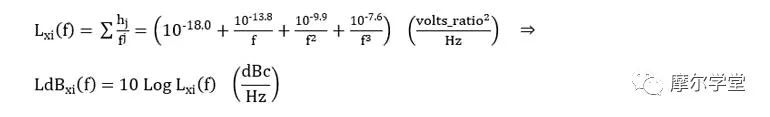

來(lái)自上述相位噪聲模型點(diǎn)的相位噪聲模型系數(shù) hj :

h0= L0fa0= 10-18.0(伏特比2Hz-1)

h1= L1fb1= (10-17.8)[11(103)]1= 10-13.8(伏特比2)

h2= L2fc2= (10-15.9)(103)2= 10-9.9(伏特比2Hz)

h3= L3fd3= (10-12.7)[5(101)]3= 10-7.6(伏特比2Hz2)

相位噪聲模型 LdBxi(f),根據(jù)上述系數(shù):

模擬圖 7中的LdBxi(f)。

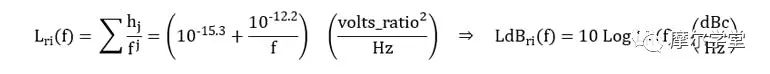

B. 參考分頻器(與頻率無(wú)關(guān))

相位噪聲模型點(diǎn)LdBj(fk),來(lái)自將通用相位噪聲模型擬合到數(shù)據(jù)表圖(未顯示):

地板段:0 dB/dec (3 kHz - ∞ Hz)

底點(diǎn):LdB 0(fa) = ?153(3 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.3(3 kHz) (伏特比2/Hz)

閃爍段:?10 dB/dec (100 Hz - 3 kHz)

中點(diǎn):LdB 1(fb) = ?150(600 Hz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-15.0(600 Hz) (伏特比2/Hz)

來(lái)自上述相位噪聲模型點(diǎn)的相位噪聲模型系數(shù) hj :

h0= L0fa0= 10-15.3(伏特比2Hz-1)

h1= L1fb1= (10-15.0)[6(102)]1= 10-12.2(伏特比2)

相位噪聲模型 LdBri(f),根據(jù)上述系數(shù):

仿真圖 7中的LdBri(f)。

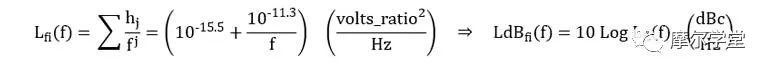

C. 反饋分頻器(與頻率無(wú)關(guān))

相位噪聲模型點(diǎn)LdBj(fk),來(lái)自將通用相位噪聲模型擬合到數(shù)據(jù)表圖(未顯示):

地板段:0 dB/dec (10 kHz - ∞ Hz)

底點(diǎn):LdB 0(fa) = ?155(10 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.5(10 kHz) (伏特比2/Hz)

閃爍段:-10 dB/dec (100 Hz - 10 kHz)

中點(diǎn):LdB 1(fb) = ?143(1 kHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-14.3(1 kHz) (伏特比2/Hz)

來(lái)自上述相位噪聲模型點(diǎn)的相位噪聲模型系數(shù) hj :

h0= L0fa0= 10-15.5(伏特比2Hz-1)

h1= L1fb1= (10-14.3)(103)1= 10-11.3(伏特比2)

相位噪聲模型 LdBfi(f),根據(jù)上述系數(shù):

模擬圖 7 中的LdBfi (f)。

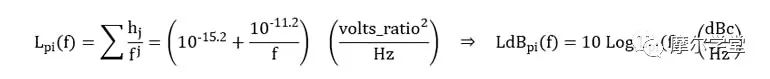

D. 預(yù)分頻器(與頻率無(wú)關(guān))

相位噪聲模型點(diǎn)LdBj(fk),來(lái)自將通用相位噪聲模型擬合到數(shù)據(jù)表圖(未顯示):

地板段:0 dB/dec (10 kHz - ∞ Hz)

底點(diǎn):LdB 0(fa) = ?152(10 KHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.2(10 kHz) (伏特比2/Hz)

閃爍段:?10 dB/dec (100 Hz - 10 kHz)

中點(diǎn):LdB 1(fb) = ?142(1 kHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-14.2(1 kHz) (伏特比2/Hz)

來(lái)自上述相位噪聲模型點(diǎn)的相位噪聲模型系數(shù) hj :

h0= L0fa0= 10-15.2(伏特比2Hz-1)

h1= L1fb1= (10-14.2)(103)1= 10-11.2(伏特比2)

相位噪聲模型 LdBpi(f),根據(jù)上述系數(shù)

模擬圖 7中的LdBpi(f)。

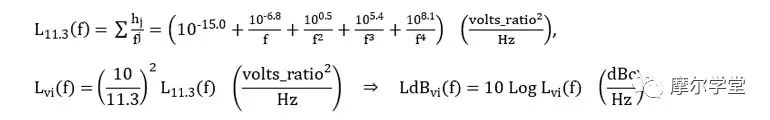

E. VCO(10 GHz 時(shí)從數(shù)據(jù)表中給出的 11.3 GHz 縮放)

相位噪聲模型點(diǎn)LdBj(fk),來(lái)自將通用相位噪聲模型擬合到 11.3 GHz 數(shù)據(jù)表圖(未顯示):

地板段:0 dB/dec (100 MHz - ∞ Hz)

底點(diǎn):LdB 0(fa) = ?150(100 MHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.0(100 MHz) (伏特比2/Hz)

閃爍段:-10 dB/dec (10 MHz - 100 MHz)

中點(diǎn):LdB 1(fb) = ?143(30 MHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-14.3(30 MHz) (伏特比2/Hz)

閃爍段:?20 dB/dec (40 kHz - 10 MHz)

中點(diǎn):LdB 2(fc) = ?111(600 kHz) (dBc/Hz)

L2(fc) = 10LdB2/10= 10-11.1(600 kHz) (伏特比2/Hz)

閃爍段:?30 dB/dec (1 kHz - 40 KHz)

中點(diǎn):LdB 3(fd) = ?59(6 kHz) (dBc/Hz)

L3(fd) = 10LdB3/10= 10-5.9(6 kHz) (伏特比2/Hz)

閃爍段:?40 dB/dec (100 Hz - 1 kHz)

中點(diǎn):LdB 4(fe) = ?18(300 Hz) (dBc/Hz)

L4(fe) = 10LdB4/10= 10-1.8(300 kHz) (伏特比2/Hz)

相位噪聲模型系數(shù) hj,來(lái)自上述 11.3 GHz 處的相位噪聲模型點(diǎn):

h0= L0fa0= 10-15.0(伏特比2Hz-1)

h1= L1fb1= (10-14.3)[3(107)]1= 10-6.8(伏特比2)

h2= L2fc2= (10-11.1)[6(105)]2= 100.5(伏特比2Hz)

h3= L3fd3= (10-5.9)[6(103)]3= 105.4(伏特比2Hz2)

h4= L4fe4= (10-1.8)[3(102)]4= 108.1(伏特比2Hz3)

相位噪聲模型 LdBvi(f),來(lái)自上述系數(shù) [數(shù)據(jù)表中給出的 11.3 GHz 時(shí)的 L11.3(f) 縮放至 10 GHz 時(shí)的 Lvi(f)]:

模擬圖 7中的LdBvi(f)。

F. 鑒相器(25 MHz)

相位噪聲模型點(diǎn)LdBj(fk),來(lái)自將通用相位噪聲模型擬合到數(shù)據(jù)表圖(未顯示):

地板段:0 dB/dec (1 kHz - ∞ Hz)

底點(diǎn):LdB 0(fa) = ?159(1 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.9(1 kHz) (伏特比2/Hz)

閃爍段:?10 dB/dec (100 Hz - 1 kHz)

中點(diǎn):LdB 1(fb) = ?154(300 Hz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-15.4(300 kHz) (伏特比2/Hz)

來(lái)自上述相位噪聲模型點(diǎn)的相位噪聲模型系數(shù) hj :

h0= L0fa0= 10-15.9(伏特比2Hz-1)

h1= L1fb1= (10-15.4)[3(102)]1= 10-12.9(伏特比2)

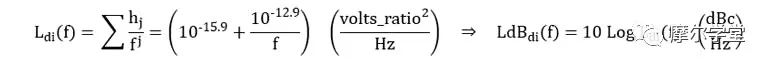

相位噪聲模型 LdBdi(f),根據(jù)上述系數(shù):

模擬圖 7中的LdBdi(f)。

G. 環(huán)路濾波器/誤差放大器(頻率不適用)

如前所述,未建模,因?yàn)樗皇蔷哂泄逃邢辔辉肼暤纳漕l組件。對(duì)其有效相位噪聲進(jìn)行建模以及計(jì)算影響輸出相位噪聲的傳播動(dòng)態(tài),比射頻組件更為復(fù)雜。1

5.通過(guò)在 10 GHz 中帶輸出處實(shí)現(xiàn)最低相位噪聲,根據(jù)整個(gè)頻段的最低平均輸出相位噪聲的唯一規(guī)范來(lái)確定環(huán)路帶寬fg 。

環(huán)路最佳帶寬 fg由 10 GHz 中帶輸出處的 VCO 和基座(參見下面的定義)相位噪聲曲線的交點(diǎn)確定。

10 GHz 時(shí)的 VCO 相位噪聲模型,LdBvi(f),曲線如前述第 4 節(jié) E 部分所示。

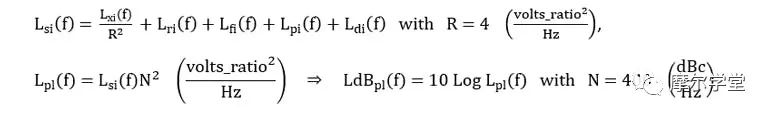

10 GHz 處的基準(zhǔn)相位噪聲模型、LdBpl(f) 和曲線,其中基準(zhǔn)定義為所有 RF 組件(VCO 除外)相位噪聲模型 Lsi(f) 乘以輸出的總和傳遞函數(shù)(稍后討論)直流增益平方,N2:

仿真圖 7中的LdBpl(f)。

然后通過(guò)數(shù)學(xué)或圖形方式確定環(huán)路帶寬,結(jié)果為 fg= 121.6 kHz。

6. 確定標(biāo)準(zhǔn)參數(shù)fn和z。

我們根據(jù)經(jīng)驗(yàn)法則 fn= fg / 1.55 確定 fn,其中 ze = 0.707(參考文獻(xiàn) 2),并根據(jù)其他規(guī)格確定 ze(未給出其他規(guī)格,因此保留 ze = 0.707 作為默認(rèn)值)。這些被發(fā)現(xiàn)是:

fn =78.5kHz

ρ = 0.707

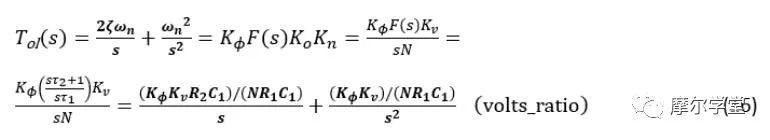

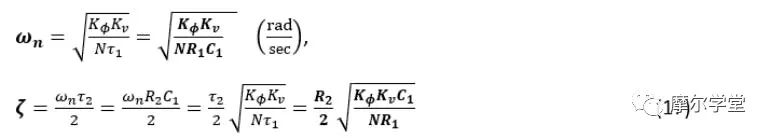

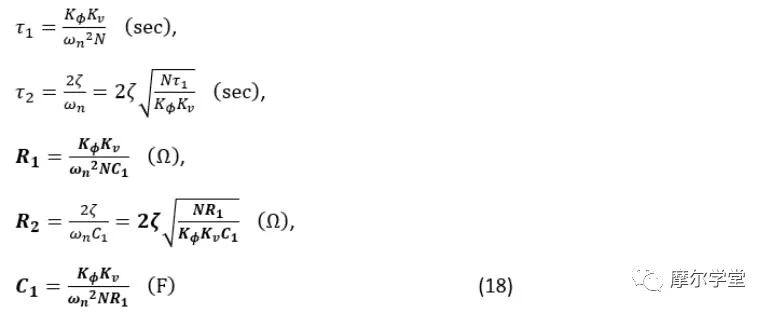

7. 將開環(huán)傳遞函數(shù)Tol的二階形式(粗體)等同于電路常數(shù)形式(粗體),從而根據(jù)電路常數(shù)R1、R2和C給出標(biāo)準(zhǔn)參數(shù)fn和ze1.

(轉(zhuǎn)換為ωn= 2πfn)

這給出了所需的關(guān)系(粗體):

8. 確定電路常數(shù) R1、R2和C1(粗體)作為標(biāo)準(zhǔn)參數(shù)fn和δ對(duì)于 10 GHz 中頻輸出 (N= 400) 并計(jì)算任何其他感興趣的量;將理論值修改為最接近的 EIA 5% 標(biāo)準(zhǔn)值。

(轉(zhuǎn)換回fn=ωn/2π)。

注意,R1、R2和C1不是唯一確定的,因此必須絕對(duì)選擇其中之一,通常是C1。對(duì)于這種情況,選擇C1,然后計(jì)算R1和R2(均適用于諧振頻率fn= 78.5 kHz 和阻尼系數(shù)z= 0.707),其中選擇C1是為了保持R1和R2相對(duì)較低。因此,電阻噪聲相對(duì)于誤差放大器(運(yùn)算放大器)噪聲來(lái)說(shuō)是微不足道的,并且在實(shí)際限制內(nèi):12,13

C1= 0.015 μF(已經(jīng)是標(biāo)準(zhǔn)值的 5%)

R1= 522.9Ω(5%標(biāo)準(zhǔn)值為510Ω)

R2= 191.1Ω(5%標(biāo)準(zhǔn)值為200Ω)

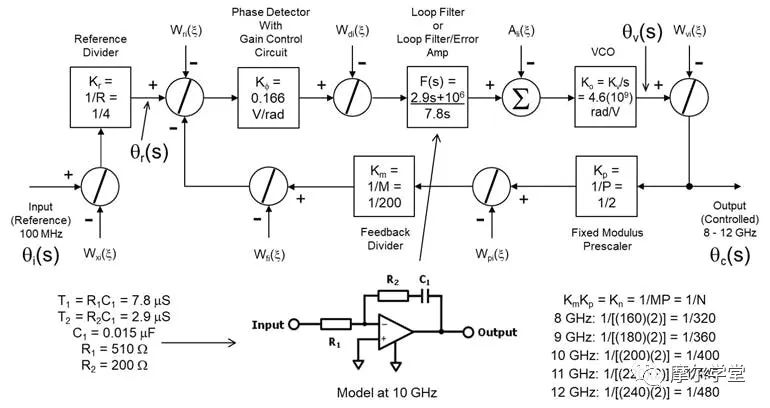

使用這些標(biāo)準(zhǔn)值,通過(guò)將通用PLL 框圖和相位噪聲傳播模型(圖 4,第 1 部分)應(yīng)用于我們的具體案例,形成特定 PLL 框圖和相位噪聲傳播模型,完成設(shè)計(jì)并配置系統(tǒng)示例 PLL 的 10 GHz 中頻輸出(圖 8)。14

8. 8 至 12 GHz 輸出/50 MHz 步進(jìn) PLL 頻率合成器的 10 GHz 中頻輸出下的特定 PLL 框圖和相位噪聲傳播模型。

9. 對(duì) PLL 開環(huán)/閉環(huán)動(dòng)態(tài)和輸出相位噪聲進(jìn)行建模,并使用適當(dāng)?shù)慕?仿真工具來(lái)仿真性能。

根據(jù)需要調(diào)整模型理論(標(biāo)準(zhǔn)值)電路常數(shù)和開環(huán)增益,以使仿真和計(jì)算的環(huán)路動(dòng)態(tài)之間最接近,以及由于計(jì)算和仿真性能之間的差異而導(dǎo)致的輸出相位噪聲。

10. 構(gòu)建并測(cè)試 EDM 單元。

使用調(diào)整后的電路常數(shù)構(gòu)建并測(cè)試 EDM 單元。由于模擬和 EDM 性能之間存在差異,請(qǐng)根據(jù)需要進(jìn)一步調(diào)整 EDM 電路常數(shù),以獲得適當(dāng)?shù)男阅堋?/p>

11. 根據(jù)模型和 EDM 單元之間的協(xié)議需要調(diào)整模型開環(huán)增益。

因此,使用步驟 8 中確定的理論(標(biāo)準(zhǔn)值)電路常數(shù)完成了設(shè)計(jì)。然后將根據(jù)步驟 9、10 和 11 細(xì)化這些值,但由于我們不是為我們的示例構(gòu)建 EDM,理論值完成了設(shè)計(jì)。

審核編輯:湯梓紅

-

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

598瀏覽量

89693 -

頻率合成器

+關(guān)注

關(guān)注

5文章

296瀏覽量

32842 -

仿真

+關(guān)注

關(guān)注

52文章

4290瀏覽量

135911 -

pll

+關(guān)注

關(guān)注

6文章

889瀏覽量

136456 -

相位噪聲

+關(guān)注

關(guān)注

2文章

187瀏覽量

23317

原文標(biāo)題:鎖相環(huán)中的相位噪聲建模、仿真和傳播(二)

文章出處:【微信號(hào):moorexuetang,微信公眾號(hào):摩爾學(xué)堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

多環(huán)鎖相頻率合成器的設(shè)計(jì)

基于DDS的頻率合成器設(shè)計(jì)介紹

如何利用FPGA設(shè)計(jì)PLL頻率合成器?

什么是寬帶頻率合成器件的相位校準(zhǔn)和控制?

單環(huán)鎖相頻率合成器,單環(huán)鎖相頻率合成器是什么意思

集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

基于DDS驅(qū)動(dòng)PLL結(jié)構(gòu)的寬帶頻率合成器的設(shè)計(jì)與實(shí)現(xiàn)

ADF4193:低相位噪聲、快速建立PLL頻率合成器數(shù)據(jù)表

CN0369 低相位噪聲的轉(zhuǎn)換鎖相環(huán)頻率合成器

pll頻率合成器工作原理與pll頻率合成器的原理圖解釋

關(guān)于相位鎖定環(huán)(PLL)頻率合成器的設(shè)計(jì)和分析

關(guān)于相位鎖定環(huán)(PLL)頻率合成器的設(shè)計(jì)和分析

評(píng)論