大規(guī)模的芯片設(shè)計(jì)的關(guān)注點(diǎn):

如何實(shí)現(xiàn)自上而下的設(shè)計(jì)流程

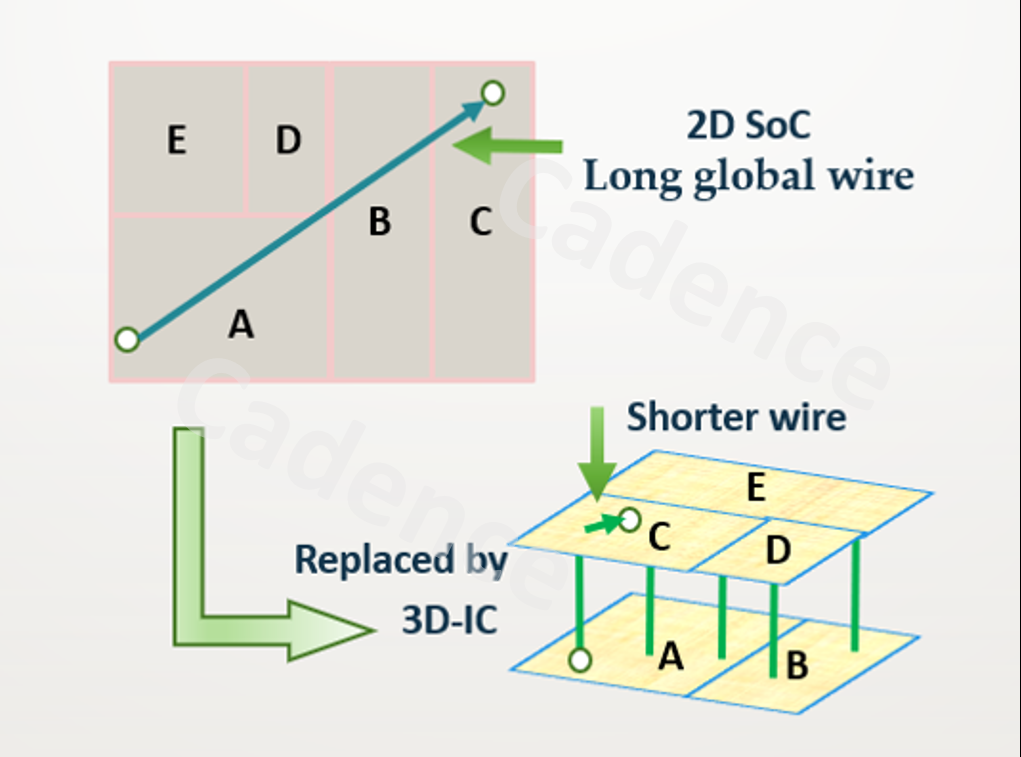

如何把一個(gè)二維集成電路的網(wǎng)表進(jìn)行切分得到三維集成電路的網(wǎng)表

如何控制不同層芯片之間互連信號(hào)的數(shù)目

如何規(guī)劃每個(gè)模塊在三維布局中的位置和形狀

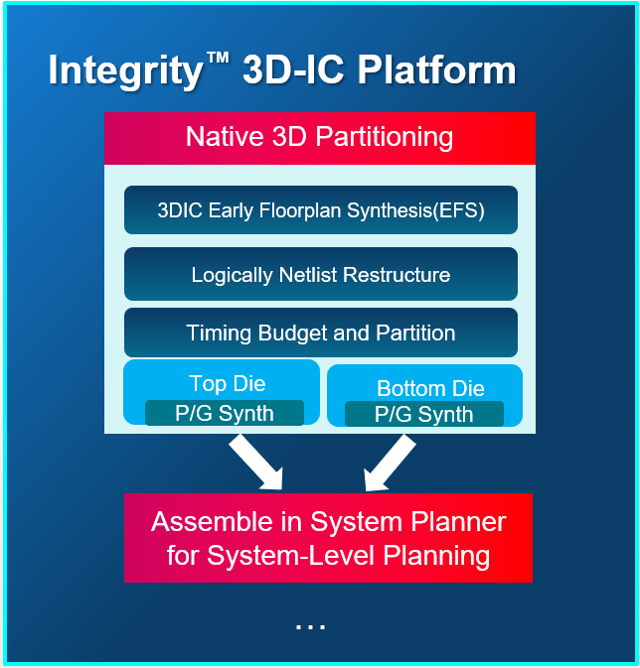

Integrity 3D-IC 早期三維布圖綜合功能,可以幫助用戶(hù)實(shí)現(xiàn)三維集成電路自動(dòng)的模塊布局、模塊形狀優(yōu)化和網(wǎng)表切分,對(duì)三維布局做快速的探索,將以往層次化設(shè)計(jì)中手動(dòng)工作幾周的時(shí)間縮短為幾個(gè)小時(shí)。

今天我們主要介紹 Integrity 3D-IC 的特色功能之一:

早期三維布圖綜合以及層次化設(shè)計(jì)方法

1. Integrity 3D-IC 早期三維布圖綜合

? 早期布圖綜合(Early Floorplan Synthesis,EFS)

? 三維布圖綜合

? 線網(wǎng)長(zhǎng)度與芯片間互連信號(hào)數(shù)目的折中

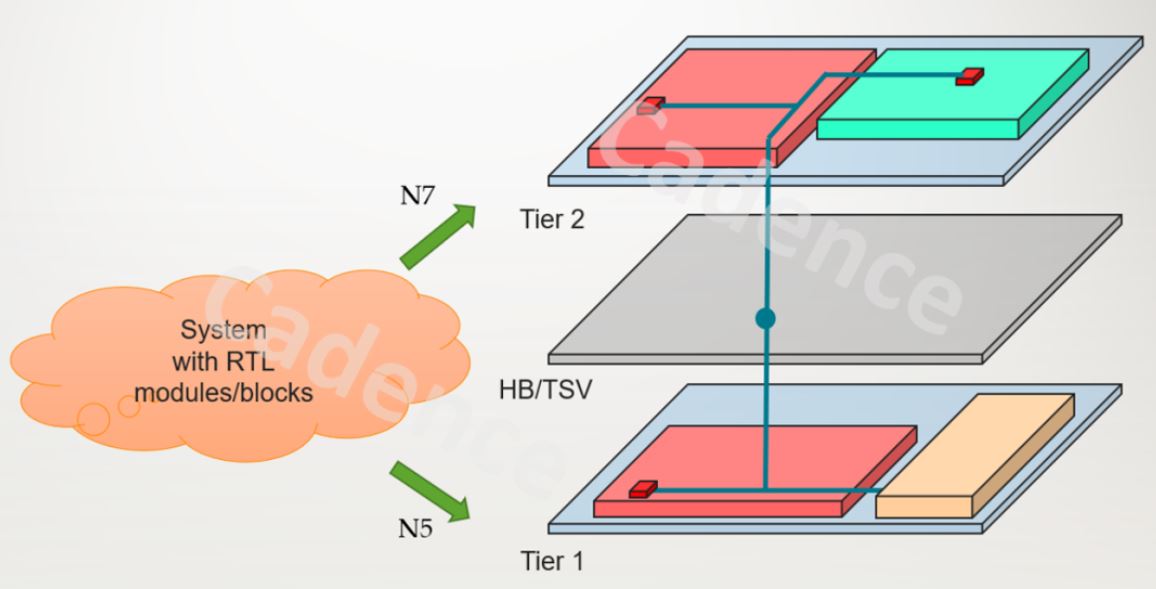

? 異構(gòu)芯片的堆疊

早期布圖綜合(Early Floorplan Synthesis,EFS)

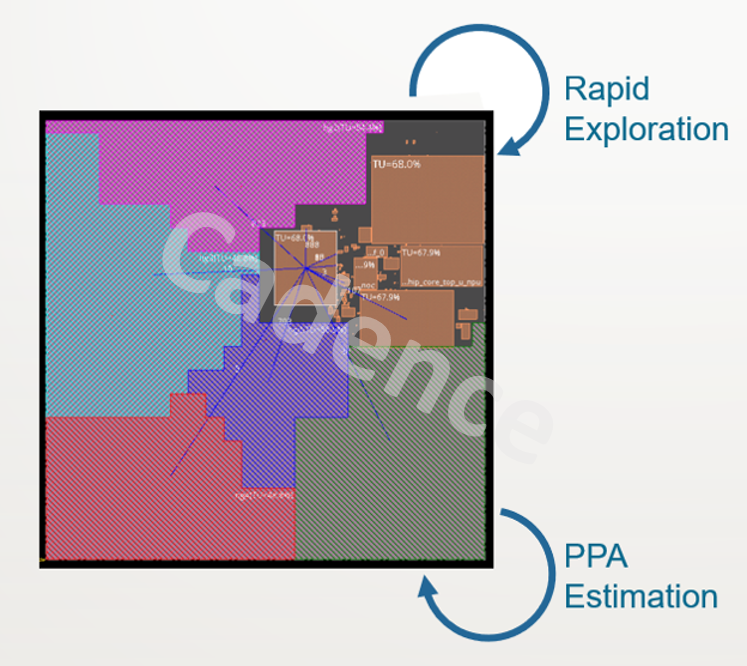

對(duì)于大規(guī)模的芯片設(shè)計(jì),各個(gè)模塊的布局布線會(huì)在 RTL 開(kāi)始了一段時(shí)間之后進(jìn)行,而芯片頂層的設(shè)計(jì)規(guī)劃需要在網(wǎng)表成熟之前就開(kāi)始,這個(gè)階段的頂層規(guī)劃往往很難創(chuàng)建,尤其是這個(gè)時(shí)候各個(gè)模塊還在不斷地優(yōu)化。所以我們提供了早期布圖綜合這樣一個(gè)功能,去自動(dòng)且快速地進(jìn)行模塊布局,幫助用戶(hù)在有完整網(wǎng)表、部分網(wǎng)表、甚至還沒(méi)有網(wǎng)表的時(shí)候,對(duì)布局進(jìn)行一系列的探索。

使用 EFS,工具可以做時(shí)序驅(qū)動(dòng)的模塊布局,優(yōu)化模塊的形狀,在滿(mǎn)足模塊的利用率的前提下,盡量壓縮減小芯片面積。同時(shí) EFS 也支持其他約束,包括模塊的寬長(zhǎng)比、利用率、是否允許直通(feedthrough),以及布線通道的寬度等。

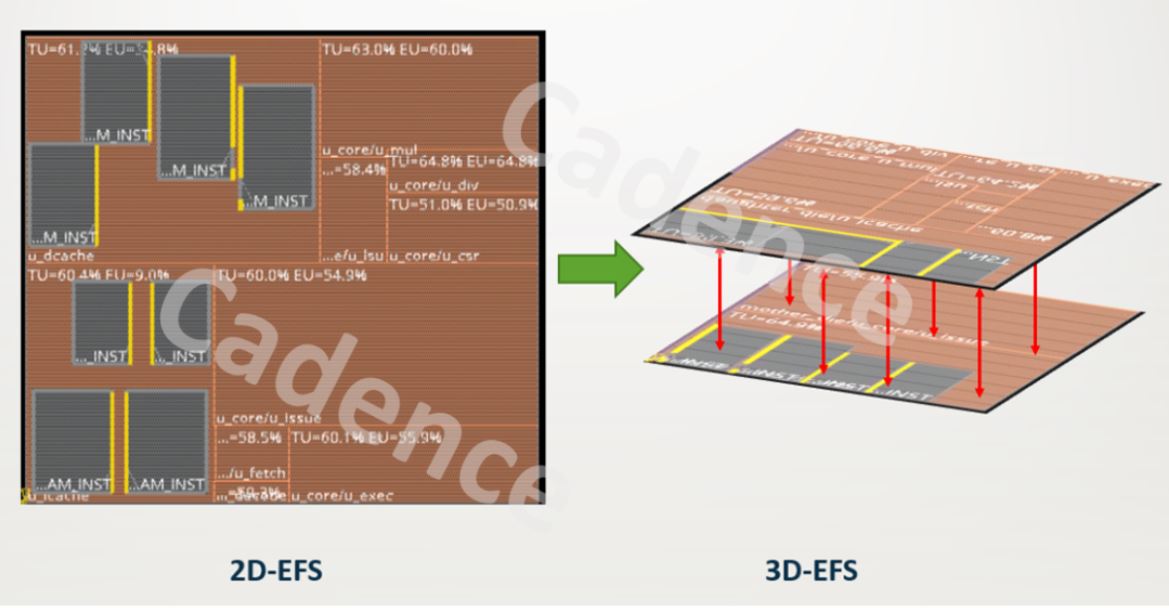

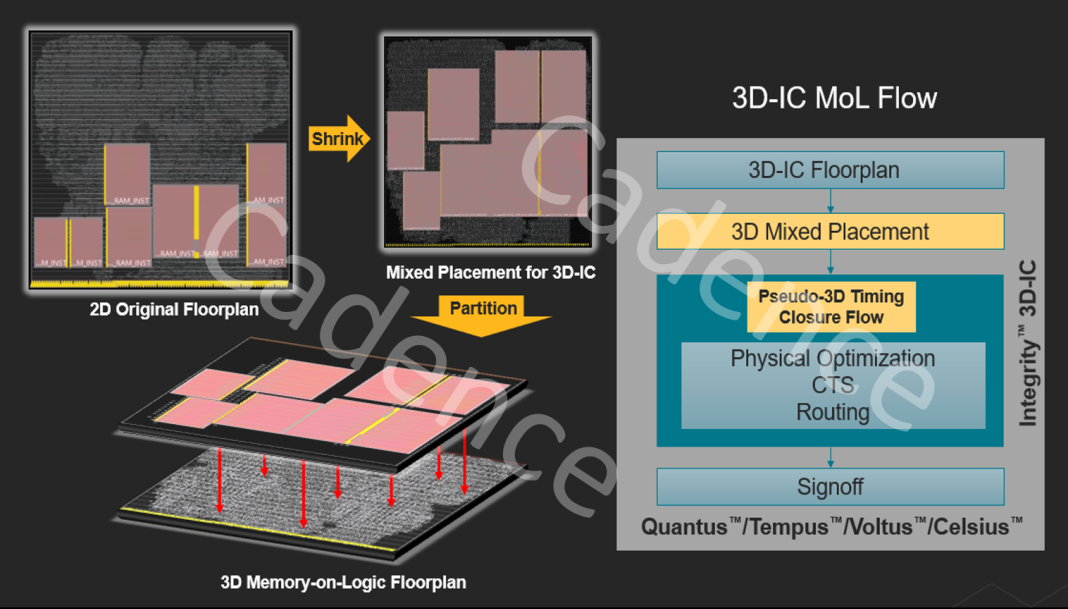

三維布圖綜合

芯片層數(shù)的增加擴(kuò)大了解空間,使得三維集成電路布圖規(guī)劃更加困難。

基于 EFS,Integrity 3D-IC 進(jìn)一步增強(qiáng)并推出了三維布圖綜合功能,在三維空間內(nèi)對(duì)模塊進(jìn)行自動(dòng)布局,并且進(jìn)行各模塊的形狀調(diào)整,從而優(yōu)化芯片面積,線網(wǎng)長(zhǎng)度和層間過(guò)孔數(shù)據(jù)。另外,Integrity 3D-IC 還支持用戶(hù)預(yù)分配模塊到某層芯片或者預(yù)擺放到某個(gè)位置。

線網(wǎng)長(zhǎng)度與芯片間互連信號(hào)數(shù)目的折中

減小系統(tǒng)線網(wǎng)長(zhǎng)度會(huì)不可避免地增加芯片間的互連信號(hào)數(shù)目。而由于 Bump / TSV 間距以及面積的限制,在做三維布圖綜合時(shí)需要控制芯片之間互連信號(hào)的數(shù)目。Integrity 3D-IC 可以很好地權(quán)衡二者,通過(guò)參數(shù)調(diào)整,幫助用戶(hù)快速地預(yù)覽結(jié)果并進(jìn)行三維布局以及分割的探索。

異構(gòu)芯片的堆疊

把不同制程的邏輯芯片堆疊在一起,既可以滿(mǎn)足性能需求,也能有更好的良率及更低的制造成本。Integrity 3D-IC 同樣支持異構(gòu)三維集成電路的布圖綜合,給不同的模塊分配合適的工藝制程。

2. 層次化設(shè)計(jì)方法

? 層次化結(jié)構(gòu)重建

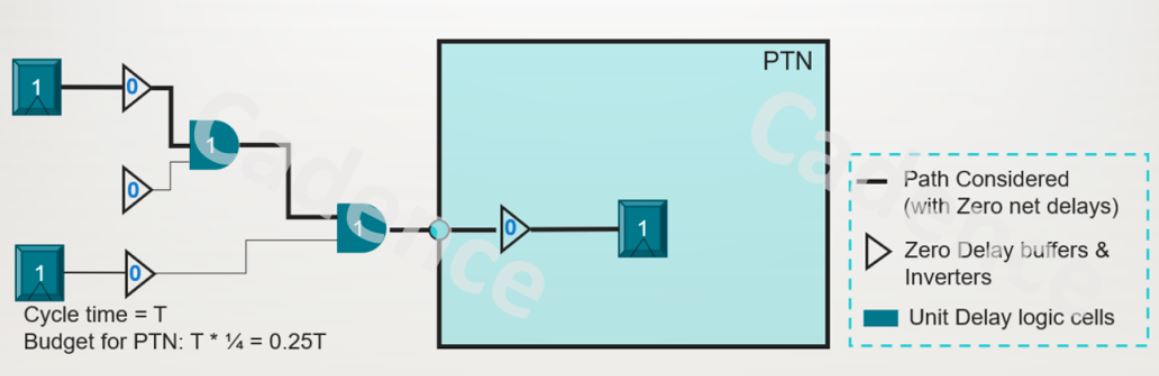

? 基于邏輯深度的時(shí)序預(yù)算

層次化結(jié)構(gòu)重建

基于三維空間模塊布局的結(jié)果,Integrity 3D-IC 會(huì)將原來(lái)二維的網(wǎng)表進(jìn)行層次化結(jié)構(gòu)的重建,在系統(tǒng)頂層產(chǎn)生 Top Die 和 Bottom Die 兩個(gè)層次化結(jié)構(gòu),把各個(gè)模塊分配給上層芯片和下層芯片,得到新的三維集成電路的網(wǎng)表。在此過(guò)程中,Integrity 3D-IC 可以自動(dòng)創(chuàng)建上層芯片與封裝 PKG 相連所需要的 Feed Through,并且更新系列相關(guān)的時(shí)序約束信息、翻轉(zhuǎn)計(jì)數(shù)格式文件等。

基于邏輯深度的時(shí)序預(yù)算

在層次化設(shè)計(jì)流程中,系統(tǒng)的時(shí)序約束需要正確地映射到相對(duì)應(yīng)的各層芯片中。在早期,可以通過(guò)基于時(shí)鐘周期的方法做快速的時(shí)序預(yù)算,給上下層芯片按指定比例分配合適的時(shí)序約束文件。為了得到更加準(zhǔn)確的時(shí)序預(yù)算,可以在 Integrity 3D-IC 使用基于邏輯深度的時(shí)序預(yù)算。基于邏輯深度的時(shí)序預(yù)算會(huì)根據(jù)最長(zhǎng)的邏輯路徑給芯片做好時(shí)序的裕量的分配,并且允許用戶(hù)靈活地對(duì)邏輯路徑上的組合邏輯單元、時(shí)序邏輯單元等設(shè)置權(quán)重,另外扇出也會(huì)被考慮在內(nèi)。

從設(shè)計(jì)初始就充分考慮三維實(shí)現(xiàn)的自由度能提供最佳系統(tǒng)性能。Integrity 3D-IC 助力架構(gòu)和布圖規(guī)劃設(shè)計(jì)師從全局考慮不同模塊在三維空間多層級(jí)上的邏輯物理分布。通過(guò) Cadence 強(qiáng)大的的層次化早期布圖規(guī)劃算法實(shí)現(xiàn)不同單元、模塊、IP 在不同層次晶粒的最優(yōu)分配,將 3D-IC 優(yōu)勢(shì)發(fā)揮到極致。

- 審核編輯 黃宇

-

集成電路

+關(guān)注

關(guān)注

5420文章

11971瀏覽量

367394 -

IC

+關(guān)注

關(guān)注

36文章

6102瀏覽量

178548 -

3D

+關(guān)注

關(guān)注

9文章

2953瀏覽量

109990 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1071瀏覽量

55490

發(fā)布評(píng)論請(qǐng)先 登錄

3D-IC設(shè)計(jì)之系統(tǒng)級(jí)版圖原理圖一致性檢查

SMARTSCAN三維掃描儀電子產(chǎn)品配件三維掃描服務(wù)

三維可視化的應(yīng)用和優(yōu)勢(shì)

Cadence 憑借突破性的 Integrity 3D-IC 平臺(tái)加速系統(tǒng)創(chuàng)新

機(jī)電約束與三維層次化組規(guī)劃與布局

3D園區(qū)可視化建模三維有哪些類(lèi)型,都有哪些功能

3D智慧城市三維可視化的特點(diǎn)

智慧園區(qū)可視化三維大屏展示綜合管理平臺(tái)的價(jià)值

工業(yè)工廠3D沉浸式三維數(shù)字化管理系統(tǒng)

Integrity 3D-IC早期三維布圖綜合功能

3D-IC未來(lái)已來(lái)

產(chǎn)品資訊 | 3D-IC 設(shè)計(jì)之自底向上實(shí)現(xiàn)流程與高效數(shù)據(jù)管理

3D-IC 設(shè)計(jì)之 Memory-on-Logic 堆疊實(shí)現(xiàn)流程

3D-IC 以及傳熱模型的重要性

3D-IC 設(shè)計(jì)之早期三維布圖綜合以及層次化設(shè)計(jì)方法

3D-IC 設(shè)計(jì)之早期三維布圖綜合以及層次化設(shè)計(jì)方法

評(píng)論