應用1 統計計數

在進行模塊設計時,我們經常需要統計報文的數量,以供軟件(or 主機)讀取,有些統計僅僅用于debug,有些統計是協議要求,有些統計是為了便于功能實現。

當需要統計的數量較多時,為了降低功耗和減少面積,我們通常采用RAM去實現。

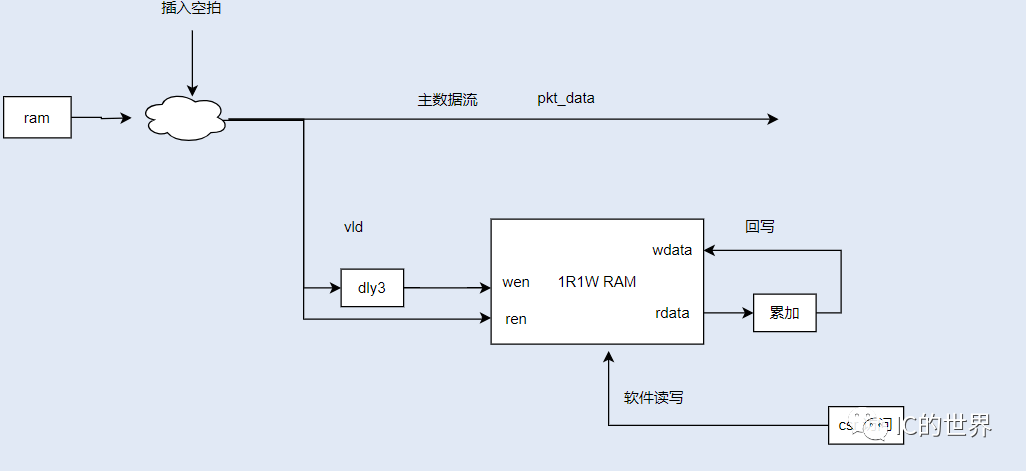

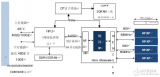

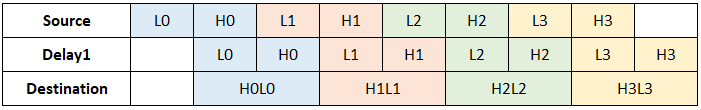

如下案例中,統計有效數據包的個數。

假設數據中存在pkt_id,pkt_id為0~63,則ram的深度為64。pkt_id用于作為讀寫地址。RAM讀延時為3個時鐘周期。

有數據來臨時,pkt_vld作為讀使能,讀出當前包計數rdata,三個周期后,rdata加1回寫到ram。

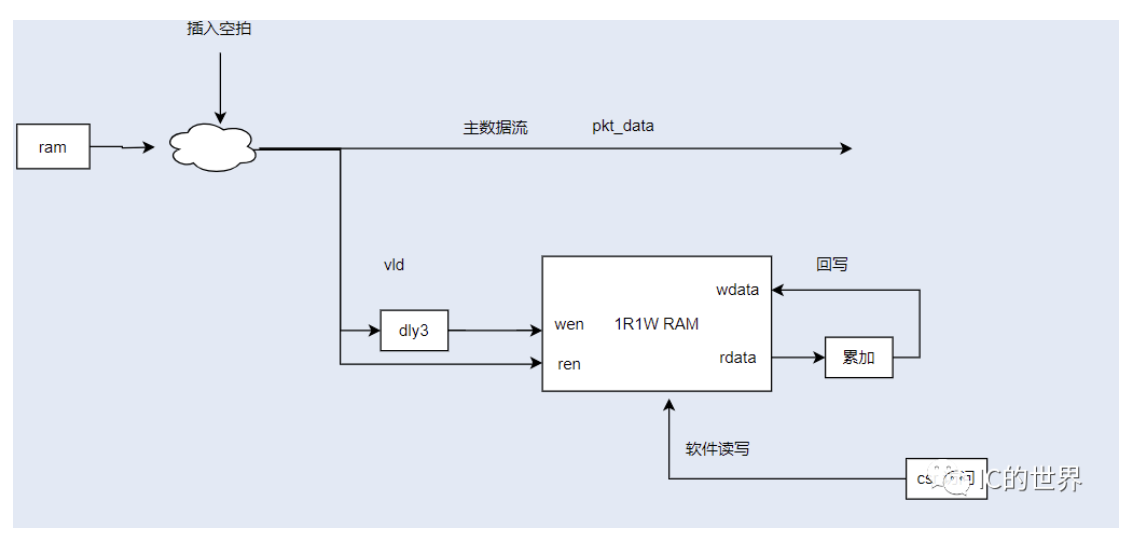

如下圖所示:需要有三個注意事項

NOTE1:需要有讀寫保護,因為可能出現連續4個周期內,pkt_vld為1,且pkt_id相同,此時會出現同一個周期對相同的地址進行讀寫,因此需要RAM需要添加讀寫保護模塊,保證數據能夠正確寫入,且讀出的都是最新值,否則就會出現統計錯誤。

NOTE2:圖中既有軟件讀、又存在硬件讀,且硬件讀優先級更高,軟件讀優先級低,因此為了保證軟件讀能夠在有效周期內得到響應,因此需要在主數據流上插入空拍,避免出現軟件讀長時間無法響應而產生超時。

應用2 位寬轉換

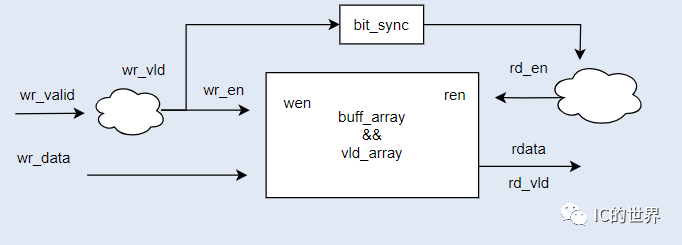

在進行模塊設計時,我們經常需要進行數據位寬的轉換,常見的兩種轉換場景有同步時鐘域位寬轉換和異步時鐘域位寬轉換。本文將介紹異步時鐘域位寬轉換

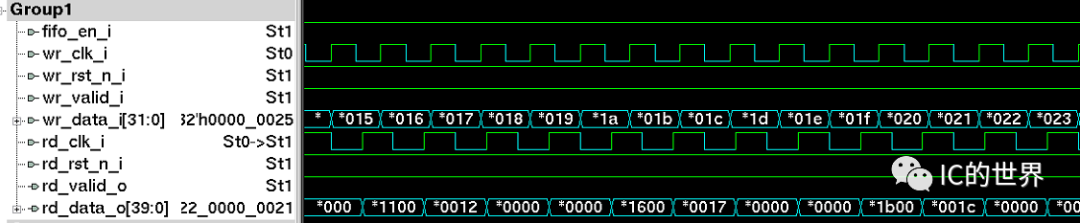

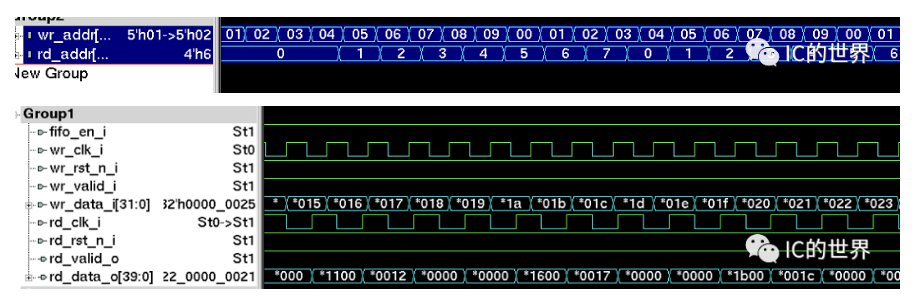

異步時鐘域的位寬轉換讀時鐘和寫時鐘屬于兩個時鐘。如下案例中,數據位寬由32bit轉40bit,寫時鐘頻率156.25MHz,讀時鐘頻率125Mhz,寫數據為32bit,讀數據位寬為40bit,通過計算得到入口數據速率和出口數據速率保持一致(156.2532==40125)。

存儲模塊是由寄存器搭建的。那么需要多大存儲模塊呢?32和40的最小公倍數為160,極限場景下,只需要160bit的寄存器作為存儲就夠了,但是讀操作通常晚于寫操作,并且考慮到時鐘有抖動有偏移,為了避免溢出,稍微增加一部分緩存,我們可以采用320bit作為存儲模塊。因此寫側32bit寫10次,讀側40bit讀8次,讀寫兩側所需的時間相等。

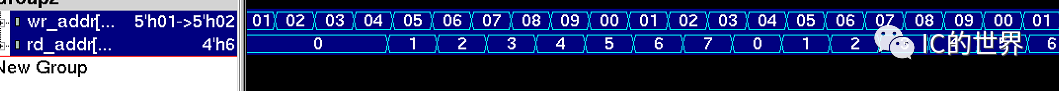

注意事項:寫地址(wr_addr)跳轉范圍是09,讀地址(rd_addr)跳轉范圍07。

如圖所示:

buff_array為320bit的數據存儲。

vld_array為80bit的有效標志位存儲:vld_array[n]為1表示buff_array[4n+3:4n]存在4bit的有效數據。

always @(posedge wr_clk or negedge wr_rst_n) begin if (~wr_rst_n) begin buff_array <= {DATA_FIFO_DEPTH{1'b0}}; vld_array <= {VALID_FIFO_DEPTH{1'b0}}; end else begin if (wr_en) begin buff_array[ wr_addr*32 +: 32] <= wr_data_i; vld_array[wr_addr*8 +: 8] <= {8{wr_valid_i}}; end end end reg [10-1:0] rd_valid_bus; reg [40-1:0] rd_data_bus; always @(*) begin rd_data_bus[40-1:0] = buff_array[ rd_addr*40 +: 40]; rd_valid_bus[10-1:0] = vld_array[rd_addr*10 +: 10]; end integer i; reg [40-1:0] rd_data_valid_mask; always @(*) begin for(i = 0; i < 40; i = i + 1) begin rd_data_valid_mask[i] = rd_valid_bus[i/4]; end end always @(posedge rd_clk or negedge rd_rst_n) begin if (~rd_rst_n) begin rd_data_o <= {40{1'b0}}; rd_valid_o <= 1'b0; end else begin if (rd_en) begin rd_data_o <= rd_data_bus & rd_data_valid_mask; rd_valid_o <= |rd_valid_bus; end else begin rd_data_o <= {40{1'b0}}; rd_valid_o <= 1'b0; end end end

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5424瀏覽量

123500 -

RAM

+關注

關注

8文章

1391瀏覽量

116874 -

數據包

+關注

關注

0文章

269瀏覽量

24899 -

讀寫保護

+關注

關注

0文章

5瀏覽量

5913

原文標題:ram的兩種應用~統計計數和位寬轉換

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA的HDTV視頻圖像灰度直方圖統計算法設計

AVR的兩種位操作及比較

STC12系列單片機的定時器有兩種計數速率

求分享S32G2內存映射系統計數器的地址

一種使用IP方法的獨特統計計數器

RAM的兩種應用:統計計數和位寬轉換

RAM的兩種應用:統計計數和位寬轉換

評論