ERC全稱為electrical rule checking,翻譯為電氣規(guī)則檢查。檢測(cè)的是GDS版圖中是否存在電學(xué)連接問(wèn)題,屬于PV(physical verification)的一個(gè)項(xiàng)目。這也算是一個(gè)后端signoff的基本概念,今天就給大家簡(jiǎn)單介紹一下ERC。

什么叫電氣規(guī)則呢?其實(shí)它的種類也不多,主要包括:1. MOS的gate不能直接連supply。2. cell input永遠(yuǎn)不能floating。3. 一個(gè)cell的driver最多一個(gè),或者說(shuō)output不能發(fā)生short。 4. N/P區(qū)(襯底或阱)不能floating。可能還有別的,不過(guò)我目前只知道這四種了,可以先了解一下。我下面分別說(shuō)一下這四條規(guī)則的理由。

對(duì)于1,我們?cè)谠O(shè)計(jì)芯片的時(shí)候總是會(huì)按最悲觀的情況考慮問(wèn)題,因此我們會(huì)認(rèn)為PG的供電總是不穩(wěn)定的。人們的初衷可能都是簡(jiǎn)單的,希望一個(gè)mos常開或者常關(guān),但如果直接將PG接到gate上,在電壓出現(xiàn)波動(dòng)的時(shí)候(比如說(shuō)由于靜電),這個(gè)mos的開關(guān)就不那么穩(wěn)定,其溝道電阻相應(yīng)會(huì)受到影響。甚至電壓波動(dòng)很大的時(shí)候會(huì)發(fā)生邏輯錯(cuò)誤,或者擊穿mos管。

因此實(shí)際應(yīng)用的時(shí)候,對(duì)于那些輸入一直為0或者一直為1的情況,我們會(huì)從PG接一個(gè)TIE cell,再接到gate上。TIE cell可以起到一個(gè)穩(wěn)定電壓、中繼的作用。

Cell的input如果floating,那個(gè)pin就是會(huì)類似一根天線,它的電壓很容易受旁邊電路的影響,此時(shí)就不能認(rèn)為它是一個(gè)完美的高電壓或者低電壓了,相對(duì)應(yīng)的數(shù)字信號(hào)就沒了意義。這里可能要聯(lián)系一點(diǎn)模擬的知識(shí),假設(shè)高電壓是5V,低電壓是0V,我們可能就認(rèn)為4V以上就是邏輯1,1V以下就是邏輯0,所以input輸入是什么其實(shí)完全是由它的電壓決定的。

在floating的情況下,輸入就不確定,邏輯可能受到影響。除此之外還可能影響power,比如一個(gè)CMOS反相器,input如果不確定,NMOS和PMOS就處于一種“半導(dǎo)通半不導(dǎo)通”的狀態(tài)。

我們知道反向器的任何一個(gè)mos導(dǎo)通的時(shí)候另一個(gè)mos關(guān)斷,漏電流就不會(huì)很大,而這種“半導(dǎo)通半不導(dǎo)通”就會(huì)產(chǎn)生很大的漏電流,甚至?xí)龎墓茏印?/p>

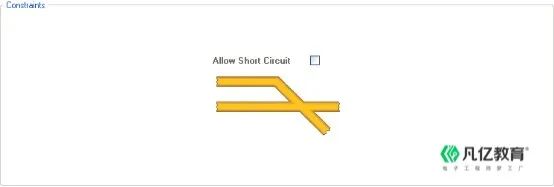

Multiple driver的情況,會(huì)導(dǎo)致電路VDD和VSS發(fā)生short。還是假設(shè)兩個(gè)反相器,它們的output接在了一起,當(dāng)?shù)谝粋€(gè)反相器輸出邏輯1(高電平),第二個(gè)反相器輸出邏輯0(低電平)的時(shí)候,相當(dāng)于產(chǎn)生一條從VDD直接到VSS的電流通路。這是絕對(duì)不被允許的。

N/P floating,還是主要為了防止latch up。一般會(huì)將N well接VDD,P substrate接VSS,減小well/substrate和drain/source之間的電勢(shì)差,可以防止latch up產(chǎn)生。

一般我們會(huì)把擺放cell的區(qū)域隔一段差一個(gè)tap cell,然后塞滿filler cell,為的就是保證n/p區(qū)同一個(gè)row的cell公用,而且都能找到附近的tap cell。這一部分可以參考我之前寫的一篇介紹latch up的文章。

除了ERC之外,現(xiàn)在還有PERC的概念,就是programmable ERC。指的是用戶可以根據(jù)自己的design客制化編寫一些ERC的rule來(lái)進(jìn)行檢查,一般都是會(huì)檢查ESD相關(guān)的rule。

比如說(shuō)PERC有current density檢查,就是檢查某一條專門用來(lái)ESD放電路徑上current承載能力的;還有point to point resistance檢查,是為了檢查ESD放電路徑的電阻,需要保證它的電阻小于其他路徑的電阻,確保靜電電流走預(yù)設(shè)好的放電路徑。

PERC還支持layout的檢查和schematic的檢查,用戶就自己設(shè)定檢查規(guī)則,也很方便。

-

反相器

+關(guān)注

關(guān)注

6文章

316瀏覽量

44101 -

ERC

+關(guān)注

關(guān)注

0文章

7瀏覽量

10023 -

漏電流

+關(guān)注

關(guān)注

0文章

273瀏覽量

17393 -

電壓波動(dòng)

+關(guān)注

關(guān)注

0文章

53瀏覽量

8251 -

GDS

+關(guān)注

關(guān)注

0文章

28瀏覽量

6427

發(fā)布評(píng)論請(qǐng)先 登錄

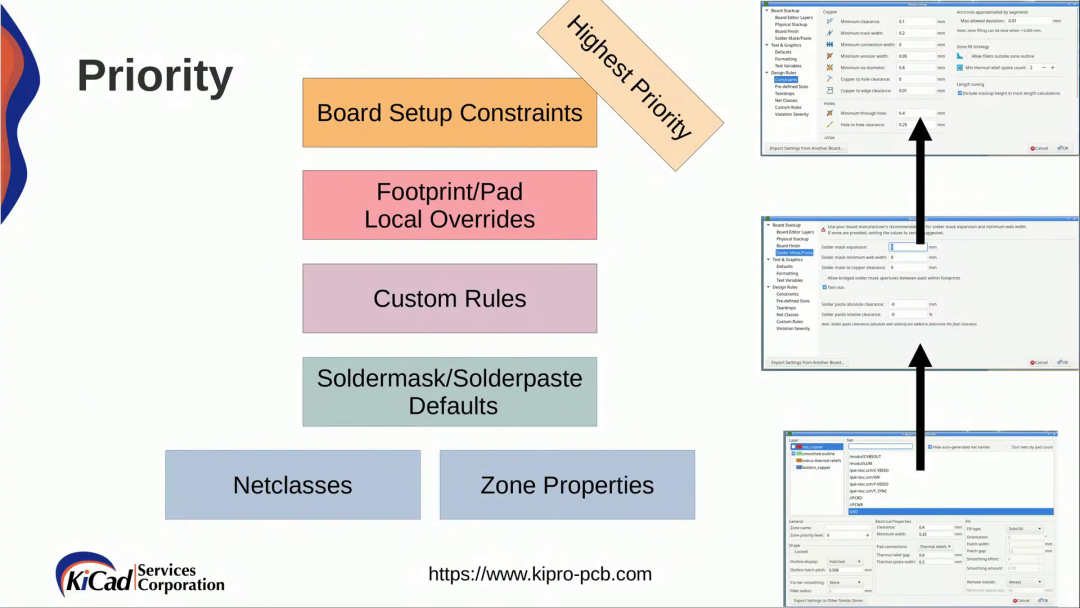

KiCad 中的自定義規(guī)則(KiCon 演講)

概倫電子先進(jìn)電路檢查分析平臺(tái)工具NanoSpice CCK介紹

Altium Designer中PCB設(shè)計(jì)規(guī)則設(shè)置

芯片設(shè)計(jì)中的設(shè)計(jì)規(guī)則檢查

和Dr Peter一起學(xué)KiCad 4.8:設(shè)計(jì)規(guī)則檢查(DRC)

電氣安規(guī)分析儀的原理和應(yīng)用

KiCad發(fā)現(xiàn)之旅(一)原理圖編輯

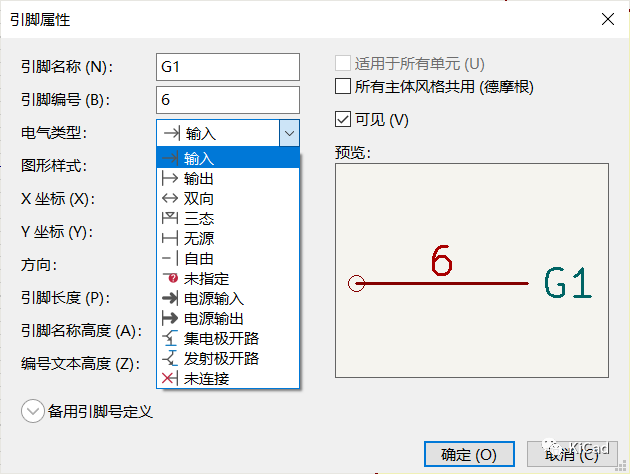

原理圖符號(hào)引腳的電氣類型

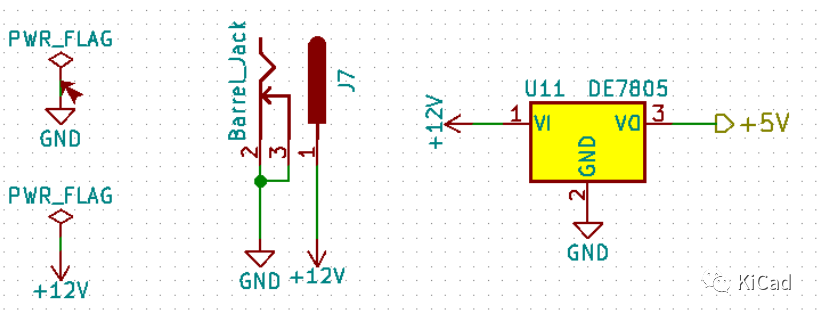

KiCad中電源符號(hào)PWR_FLAG的應(yīng)用

網(wǎng)關(guān)的設(shè)置規(guī)則

電氣設(shè)備檢修分析與建議

AD9元器件間距規(guī)則如何設(shè)置

sbam397.TSC(AMC1300B模擬電路)進(jìn)行ERC檢查時(shí)出現(xiàn)錯(cuò)誤的原因?

如何對(duì)電氣設(shè)備進(jìn)行絕緣性能檢查

什么叫電氣規(guī)則呢?電氣規(guī)則檢查-ERC

什么叫電氣規(guī)則呢?電氣規(guī)則檢查-ERC

評(píng)論