金屬柵極的使用

隨著鉿基高k材料的引入,人們發(fā)現(xiàn)高k介質(zhì)與多晶硅柵極的兼容性一直是影響高k材料使用的一個障礙。因為柵極的一個關(guān)鍵特性是它的功函數(shù),即自由載流子逃逸所需要的能量。功函數(shù)決定器件的閾值電壓Vt。傳統(tǒng)的柵介電材料 SiO2或SiON采用多晶硅為柵極,功函數(shù)取決于多晶硅的摻雜濃度。半導(dǎo)體制造商可以根據(jù)設(shè)計需要很容易地改變多晶硅摻雜濃度來得到所需的閾值電壓。然而隨著鉿基高k材料的引入,人們發(fā)現(xiàn)如果繼續(xù)使用多晶硅作為柵極材料,鉿基材料與多晶硅材料之間會形成Hf-Si鍵從而產(chǎn)生所謂的“費米釘軋現(xiàn)象”,即功函數(shù)被拉向多晶硅能帶間隙中央,這種現(xiàn)象在PMOS器件中更為顯著,這就使得閾值電壓變得不可調(diào)制。而金屬柵極的使用可以解決柵極和高k柵介質(zhì)材料的相容性問題。

同時,柵極也面臨等比例縮小的挑戰(zhàn)。施加在柵極上的電壓會將少數(shù)載流子從溝道區(qū)吸引到電介質(zhì)和溝道的界面處,形成反型載流子分布。這時會在柵極的兩側(cè)形成載流子的累積,以維持電荷中性,這必將耗盡附近半導(dǎo)體的電荷。當(dāng)半導(dǎo)體的電荷被完全耗盡時,半導(dǎo)體就等于絕緣體了,相當(dāng)于增大了柵介質(zhì)的有效厚度。盡管耗盡層厚度只有幾個埃的SiO2厚度(對于NMOS為2~4?,對于PMOS為3~6?),但是當(dāng)柵介質(zhì)厚度降到十幾個埃左右時,這一厚度的影響就變得十分顯著。由于降低等效氧化層厚度是器件等比例縮小的關(guān)鍵, 因此多晶硅的耗盡就成了一個很大的障礙。

雖然可以通過提高多晶硅柵極的摻雜濃度來提高材料中自由載流子的濃度,以此來緩解多晶硅的耗盡,但是柵極中的摻雜已經(jīng)接近飽和水平,尤其對PMOS來講,高濃度硼穿透柵介質(zhì)已經(jīng)是十分嚴(yán)重的問題了。而金屬中有大量的自由載流子濃度,不會受到耗盡的限制。

另外采用金屬柵替代多晶硅柵還可以消除遠(yuǎn)程庫侖散射效應(yīng),有效抑制高k柵介質(zhì)中表面軟聲子散射引起的溝道載流子遷移率下降。與多晶硅柵/高k介質(zhì)相比,金屬柵/高k介質(zhì)柵結(jié)構(gòu)具有更高的電子和空穴遷移率,合適的閾值電壓,在RMOS和PMOS器件中具有更高的驅(qū)動電流性能。

金屬柵材料性能的要求

1、合適的有效功函數(shù)

有效功函數(shù)是高k/金屬柵結(jié)構(gòu)中最重要的參數(shù)之一,它是影響閾值電壓的最主要的因素。其表達(dá)式為

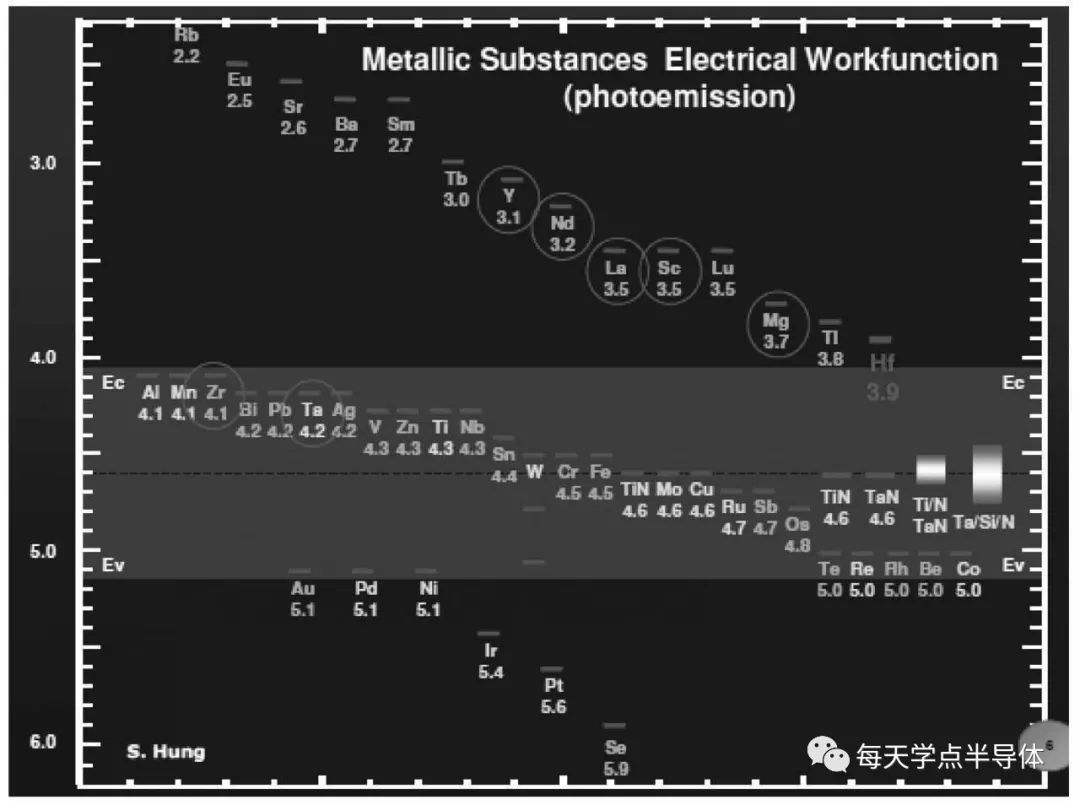

柵金屬的功函數(shù)需要和溝道中載流子的能量相匹配,也就是說所選金屬柵極的功函數(shù)必須分別能滿足PMOS和NMOS的需求。圖6.1所示為不同材料的功函數(shù)。除金屬的組成外,金屬的有效功函數(shù)會隨沉積方式、晶體結(jié)構(gòu)、底層的介質(zhì)材料以及所經(jīng)歷的高溫過程不同而變化。

圖6.1不同金屬的功函數(shù)

金屬柵極的選擇通常根據(jù)器件的要求不同而選用不同的功函數(shù):一是選擇近Si的禁帶中央的同一種金屬作為PMOS和NMOS器件的柵極,但由于其功函數(shù)不可調(diào),通常只適于SOI、雙柵晶體管以及 FinFET器件的應(yīng)用需求;而對于高性能器件,需要選擇雙金屬柵,即功函數(shù)分別靠近Si價帶和導(dǎo)帶的金屬材料,作為PMOS(大約5.0~ 5.2eV)和NMOS(大約4.1eV)器件的柵極。雙金屬柵極工藝具有較高的挑戰(zhàn)性,不僅需要選擇合適功函數(shù)的材料,而且必須能夠在不破壞第一層金屬的情況下得到第二層金屬。

2、較高的熱穩(wěn)定性

熱不穩(wěn)定性可能導(dǎo)致金屬材料與高k介質(zhì)間的相互擴(kuò)散或化學(xué)反應(yīng),引發(fā)等效氧化物厚度(EOT)增加、閾值電壓變化、漏電流增大等效應(yīng),使器件電學(xué)性能嚴(yán)重衰退。因此柵極金屬必須具有高的熱穩(wěn)定性以避免金屬沉積和退火過程中產(chǎn)生的氧空位及過度氧化導(dǎo)致的有效功函數(shù)偏移。尤其對于先柵極工藝中,柵極金屬與高k材料必須經(jīng)歷傳統(tǒng)CMOS工藝中激活摻雜雜質(zhì)采用的1000℃左右高溫?zé)崽幚砉に嚕诟邷赝嘶饤l件下,獲得合適的有效功函數(shù)極具挑戰(zhàn)性。

3、較低的界面態(tài)密度

金屬柵與高k介質(zhì)之間,高k介質(zhì)與SiO2之間存在著一定的界面態(tài)。較高的界面態(tài)密度會產(chǎn)生大量的界面固定電荷和陷阱電荷,造成器件性能及可靠性的降低,因此需要較低的界面態(tài)密度。金屬柵極取代多晶硅在滿足功函數(shù)和熱穩(wěn)定性要求的同時,不應(yīng)對器件載流子遷移率、柵漏電流等電學(xué)性能和整體可靠性造成影響。

4、HKMG(高k介質(zhì)層+金屬柵極)整合工藝

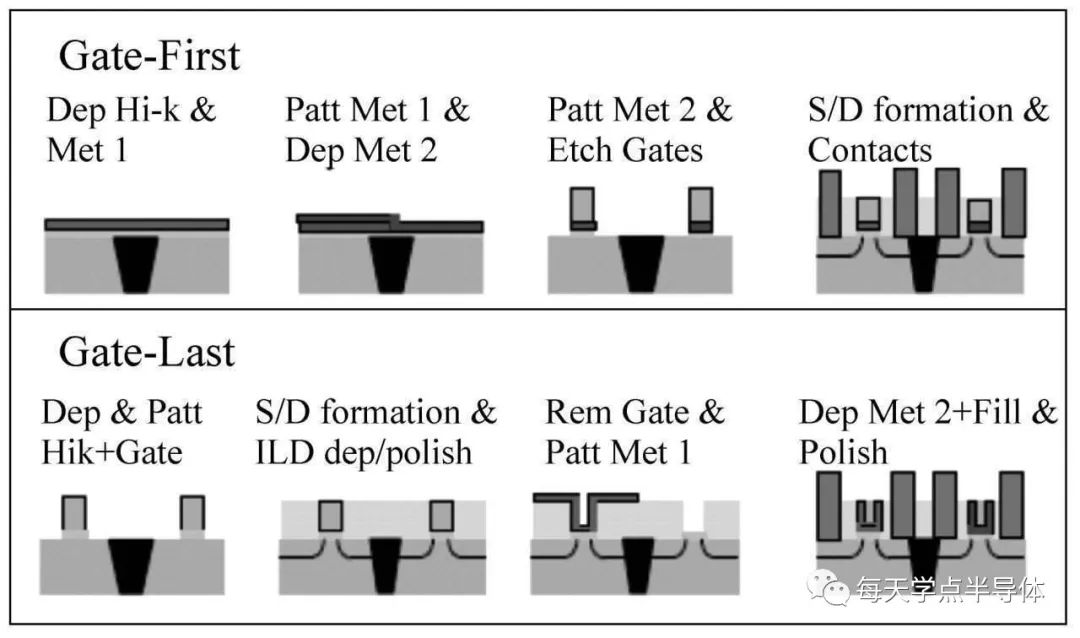

目前在制作HKMG結(jié)構(gòu)晶體管的工藝方面,業(yè)內(nèi)主要存在兩大各自固執(zhí)己見的不同陣營,分別是以IBM為代表的gate-first(先柵極)工藝流派和以Intel公司為代表的gatelast(后柵極)工藝流派(見圖6.2)。后柵極工藝又分先高k和后高k兩種不同方法,圖6.2所示為先高k后柵極工藝,Intel公司在45nm采用,到32nm后轉(zhuǎn)為后高k后柵極工藝。一般來說使用gate-first工藝,高k介質(zhì)和金屬柵極必須經(jīng)受漏源極退火工藝的高溫,因此實現(xiàn)HKMG結(jié)構(gòu)的難點在于如何控制PMOS管的Vt電壓(閾值電壓);而gate-last工藝雖然工藝復(fù)雜,芯片的管芯密度同等條件下要比gate-first工藝低,但是金屬柵極不需要經(jīng)受高溫過程,不論先高k還是后高k。因此先柵極金屬柵材料的選擇非常困難。

圖6.2 HKMG整合工藝

5、金屬柵極有效功函數(shù)的調(diào)制

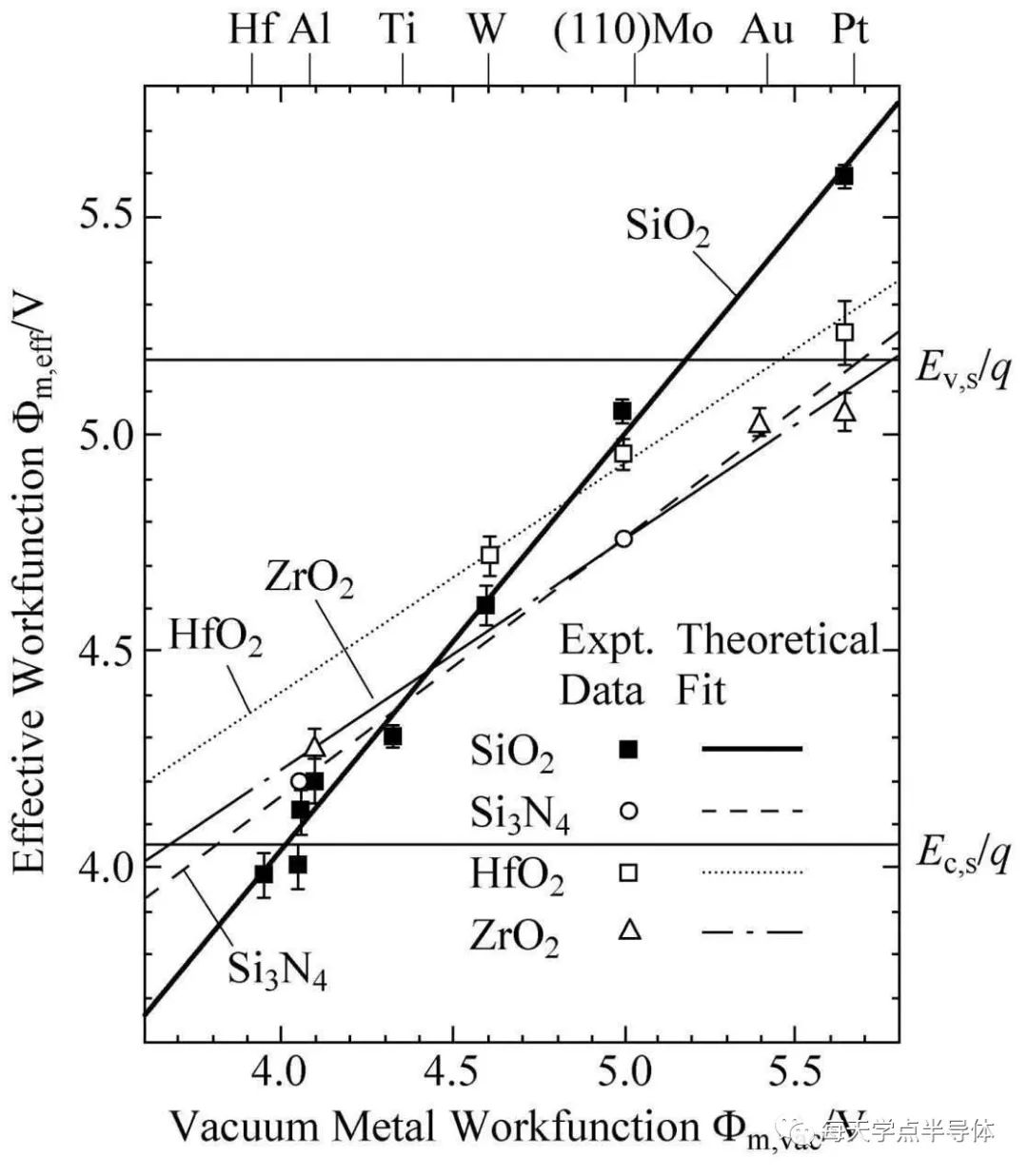

由于金屬柵極功函數(shù)與柵介質(zhì)材料有關(guān)。高k/金屬柵結(jié)構(gòu)界面處存在本征界面態(tài),導(dǎo)致金屬費米能級向高k介質(zhì)的電荷中性能級移動,產(chǎn)生費米能級釘軋效應(yīng)。這種效應(yīng)使得有效功函數(shù)主要由高k介質(zhì)決定,大幅縮小了金屬柵在高k介質(zhì)上的有效功函數(shù)調(diào)制范圍(見圖6.3),使高k介質(zhì)上的金屬柵有效功函數(shù)的調(diào)制變得困難。

圖6.3不同金屬柵極在不同柵介質(zhì)上的有效功函數(shù)

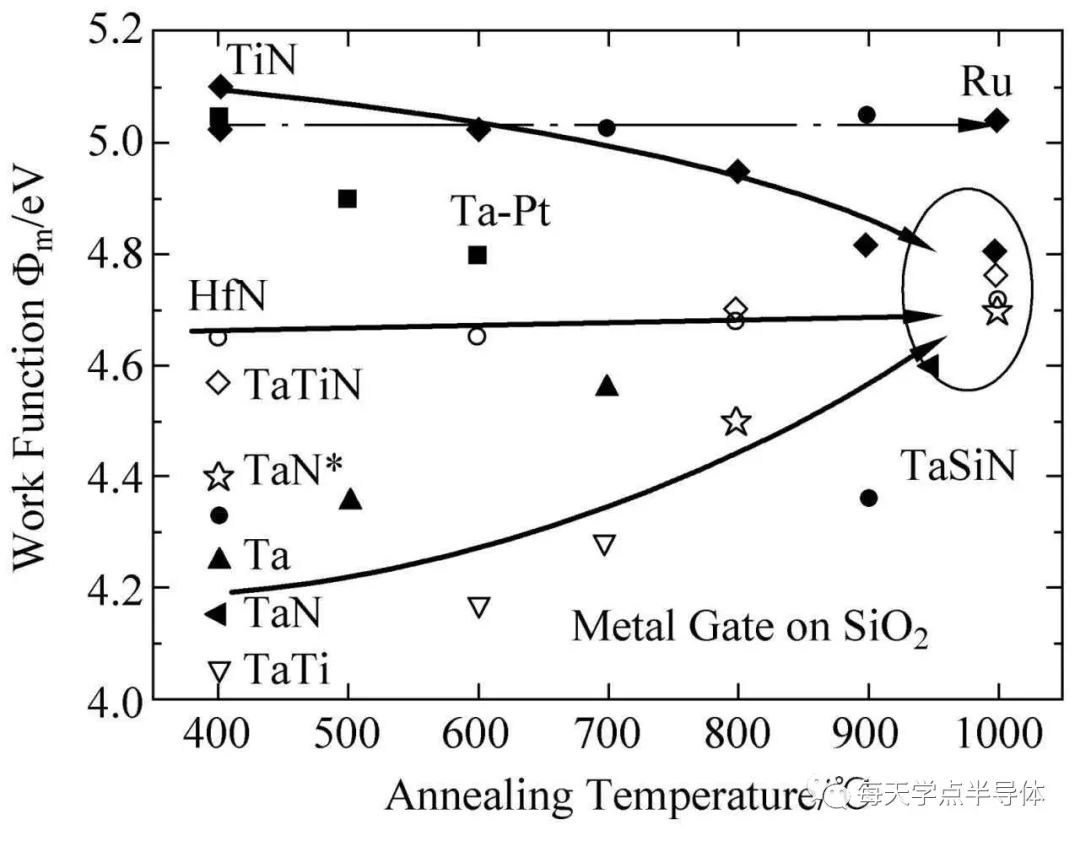

另外,高溫退火可能導(dǎo)致金屬柵與柵介質(zhì)間的界面反應(yīng)和相互擴(kuò)散,造成有效功函數(shù)的嚴(yán)重漂移。圖6.4所示為金屬柵極/SiO2介質(zhì)體系,在高溫退火后,金屬有效功函數(shù)移向Si的禁帶中央。金屬柵極/高k體系同樣會遇到同樣的問題。因此,金屬柵材料的選擇會因為HKMG整合工藝不同而不同。而先柵極金屬柵材料的選擇比后柵極工藝更加困難。

圖6.4金屬功函數(shù)隨退火溫度變化

早期的解決思路主要是通過改變金屬柵極材料的成分獲得合適的有效功函數(shù)和高的熱穩(wěn)定性與常規(guī)CMOS工藝兼容的鎳的全硅化工藝是自對準(zhǔn)工藝,而且?guī)缀鯖]有柵介質(zhì)的損傷,是一種比較簡單的形成金屬柵的方法。由于NiSi的功函數(shù)接近硅能帶間隙中央,可以通過摻雜(PtSix:5.1eV;Ni(20%)Ta(80%)Si:4.2eV)和改變硅化鎳的相態(tài)(NiSi:4.5eV;Ni3 Si:4.85eV)對其進(jìn)行調(diào)節(jié)。但是高摻雜濃度的硅化物和相控制都很難付諸生產(chǎn),硅化處理的不完全和組分的微小偏差都會導(dǎo)致柵極功函數(shù)出現(xiàn)較大幅度的變化;而且用NiSi做柵極同時也會形成Hf-Si鍵,不能對閾值電壓進(jìn)行很好的控制。

單元素金屬或者合金可以作為金屬柵極,但是它們的熱穩(wěn)定性和抗氧化能力較差,只有少數(shù)像鉑和銥這樣的貴金屬較好,但是這些金屬極難刻蝕,很難與標(biāo)準(zhǔn)工藝集成。

具有良好導(dǎo)電性和合適功函數(shù)的金屬氧化物如氧化銥(4.32eV)和氧化釕(5.0~5.3eV),同樣可以作為MOS器件柵極的候選材料,然而金屬氧化物的熱穩(wěn)定性差,并且其成分中的氧在高溫退火條件下會向襯底擴(kuò)散導(dǎo)致襯底被進(jìn)一步氧化,使得有效功函數(shù)變化和等效氧化物厚度(EOT)增加,且金屬氧化物對H2的退火氣氛十分敏感。

氮的加入可以很大程度上提高金屬柵的熱穩(wěn)定性和抗氧化能力。難熔金屬的氮化物(TiN、TaN、HfN、WN)與高k柵介質(zhì)之間有較好的熱力學(xué)和化學(xué)穩(wěn)定性,界面特性良好,與高k柵介質(zhì)的集成表現(xiàn)出 良好的電學(xué)特性。但由于難熔金屬氮化物與高k材料在源漏雜質(zhì)激活過程中的界面反應(yīng)、高k介質(zhì)中的氧空位、偶極子層、金屬誘生界面態(tài)等引起的費米能級釘軋效應(yīng),使金屬柵的有效功函數(shù)一般被限制在禁帶中央附近。

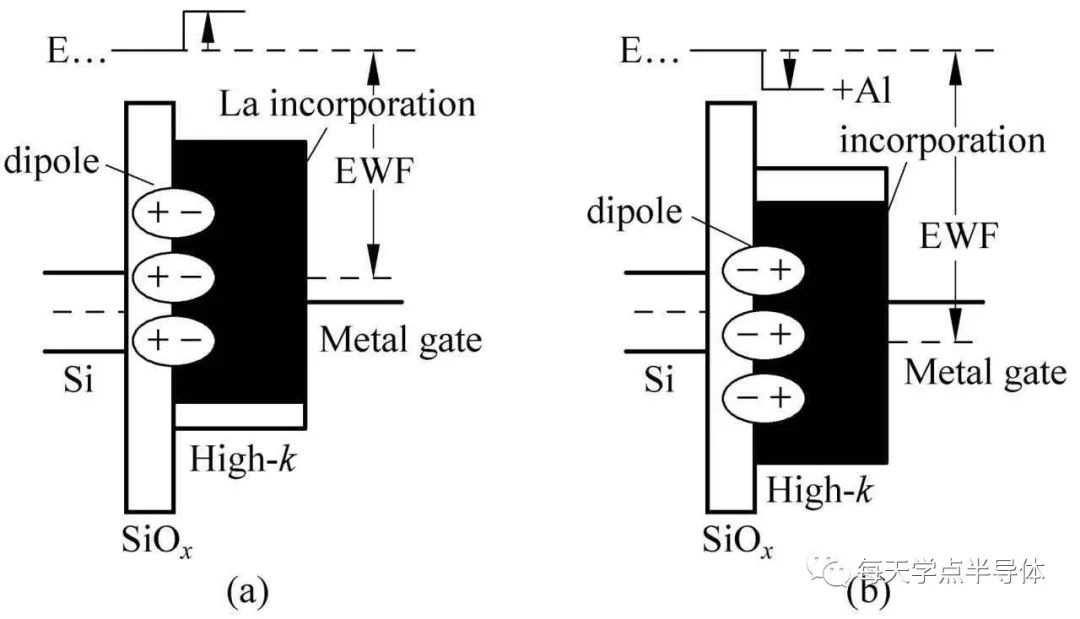

目前對于先柵極工藝,通常采用高k/金屬柵的界面調(diào)制,通過在界面處引入偶極子層來調(diào)節(jié)有效功函數(shù)。通常采用功函數(shù)位于帶隙中間的金屬(如TiN),而通過在高k介質(zhì)上(或下)沉積不同的覆蓋層來調(diào)節(jié)Vt。通過覆蓋層得到帶邊功函數(shù)的原理是覆蓋層與高k材料在高溫退火過程中發(fā)生互混,最后在高k/SiO2界面處形成偶極子層來實現(xiàn)的。La等適合調(diào)節(jié)NMOS管有效功函數(shù)是因為La2O3中氧的區(qū)域濃 度小于過渡層SiO2中的氧的濃度,所以氧會向高k方向移動,最后形成電場是由界面層SiO2指向高k介質(zhì)的偶極子層,該電場的存在可以改變帶邊間的勢壘差,使NMOS管金屬柵的有效功函數(shù)從禁帶中央附近向?qū)Ц浇苿樱欢鳤l誘生的偶極子層的極性與La形成的偶極子層的極性相反,使PMOS管金屬柵的有效功函數(shù)從禁帶中央附近向價帶附近移動,如圖6.5所示。但是如前所述,這種方法對NMOS的作用十分明顯,而對PMOS效果則不顯著,而且由于Al2O3的k值較低,PMOS的EOT也會受到影響。所以高性能器件的PMOS的Vt調(diào)節(jié)目前仍是先柵極工藝中的主要挑戰(zhàn)之一。而采用后柵極工藝,由于不需要經(jīng)歷高溫的源漏激活過程,金屬材料的選擇相對較簡單。目前量產(chǎn)的Intel公司主要采用TiN作為PMOS的金屬柵極,而通過擴(kuò)散形成TiAlN 作為NMOS的金屬柵極。

圖6.5 La、Al元素在高k/SiOx界面產(chǎn)生的偶極子層對有效功函數(shù)的影響

6、金屬柵極的沉積方法

金屬柵極的沉積方法主要由HKMG的整合工藝決定。為了獲得穩(wěn)定均勻的有效功函數(shù),兩種工藝都對薄膜厚度的均勻性要求較高。另外,先柵極的工藝對金屬薄膜沒有臺階覆蓋性的要求,但是后柵極工藝因為需要重新填充原來多晶硅柵極的地方,因此對薄膜的臺階覆蓋 性及其均勻度要求較高。

目前的功函數(shù)金屬柵極沉積主要采用原子層沉積(ALD)或射頻濺射物理氣相沉積法(RFPVD)。兩者相比,ALD的方法可以提供很好的階梯覆蓋性,可以得到均勻的金屬柵極厚度,為得到穩(wěn)定的功函數(shù)提供保證;而RFPVD的方法可以容易地通過調(diào)節(jié)反應(yīng)參數(shù)獲得不同功函數(shù),同時獲得比ALD更高的生產(chǎn)能力。因此先柵極工藝一般選擇RFPVD方法沉積功函數(shù)金屬,后柵極工藝隨器件尺寸減小,會逐漸從RFPVD向ALD過渡。

通常情況下,功函數(shù)金屬的厚度一般選擇在50~100?之間可以獲得比較穩(wěn)定的功函數(shù)。

在后柵極工藝中,功函數(shù)金屬沉積后,需要再沉積金屬Al將金屬柵極連接出去。一般采用熱鋁的方法來完成。之前需要濺射法沉積Ti作為黏附層,CVD鋁作為籽晶層。

自對準(zhǔn)硅化物

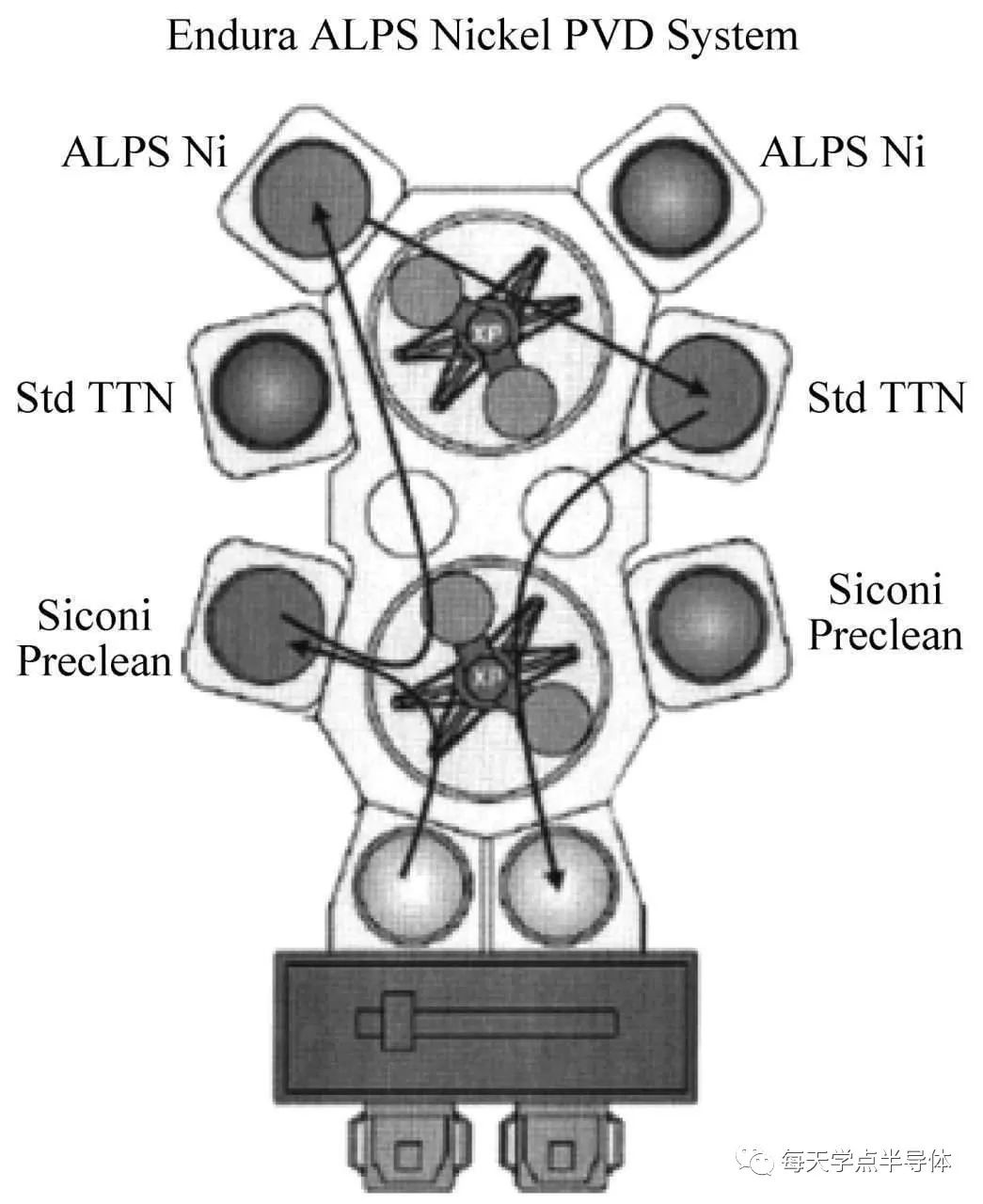

圖6.6是標(biāo)準(zhǔn)的Endura物理氣相沉積(PVD)鎳-鉑合金薄膜的機(jī)臺結(jié)構(gòu),主要包括三部分:預(yù)清潔處理腔(preclean)、鎳-鉑(NiPt)合金薄膜沉積腔和蓋帽層(cap layer)TiN沉積腔。其中根據(jù)具體工藝需要,每種腔室可以有一個或多個,以達(dá)到最佳的工藝速度。工藝過程中,硅片(wafer)先進(jìn)入預(yù)清潔處理腔,以去除硅片表面的自然氧化物(native oxide),然后進(jìn)入鎳-鉑合金薄膜沉積腔沉積一層鎳-鉑合金薄膜,最后進(jìn)入TiN沉積腔生成蓋帽層。下面對這三種 工藝腔進(jìn)行詳細(xì)描述。

圖6.6標(biāo)準(zhǔn)的Endura物理氣相沉積鎳-鉑合金薄膜機(jī)臺

預(yù)清潔處理

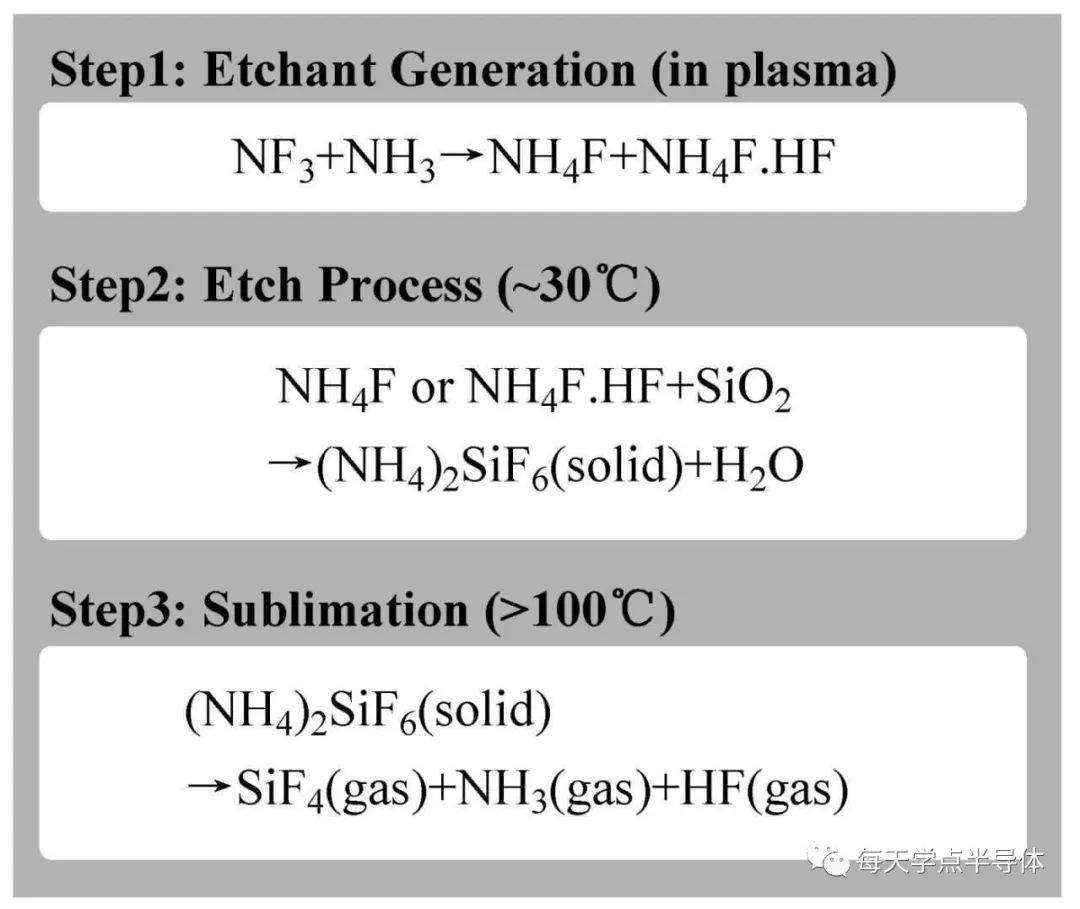

當(dāng)集成電路技術(shù)發(fā)展到65nm以下時,傳統(tǒng)的預(yù)清潔處理(preclean)方式HF dip和Ar sputter已經(jīng)不能滿足制程的需要了,必須采用先進(jìn)的SiCoNi預(yù)清潔處理腔。它主要包括兩個步驟:刻蝕(etch)和升華(sublimation)。NF3和NH3在plasma的作用下產(chǎn)生活性粒子,活性粒子在低溫條件下與硅片上的SiO2發(fā)生反應(yīng)生成易升華的化合物(NH4)2SiF6,然后在高溫下將化合物(NH4)2SiF6升華以達(dá)到除去native oxide的效果。其反應(yīng)機(jī)理如圖6.7所示

圖6.7 SiCoNi的反應(yīng)機(jī)理

與HF dip和Ar sputter相比,SiCoNi具有諸多優(yōu)點

(1)SiCoNi可以消除HF dip過程中存在的Q-time問題。由于HF dip與金屬薄膜的生長必須在不同的機(jī)臺上進(jìn)行,在硅片傳輸?shù)倪^程中,與大氣接觸使得硅片上重新生長一層薄薄的SiO2薄膜。

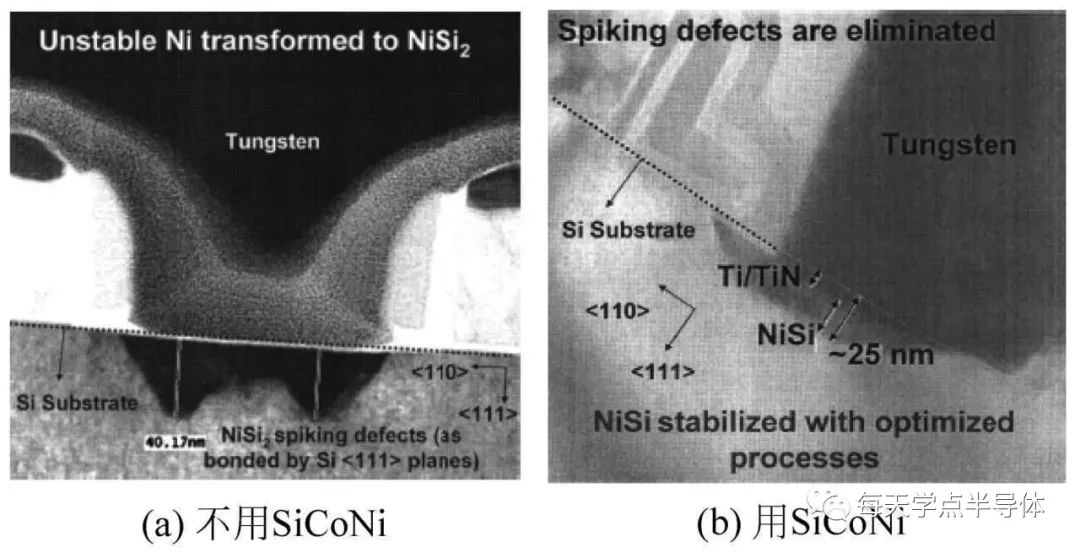

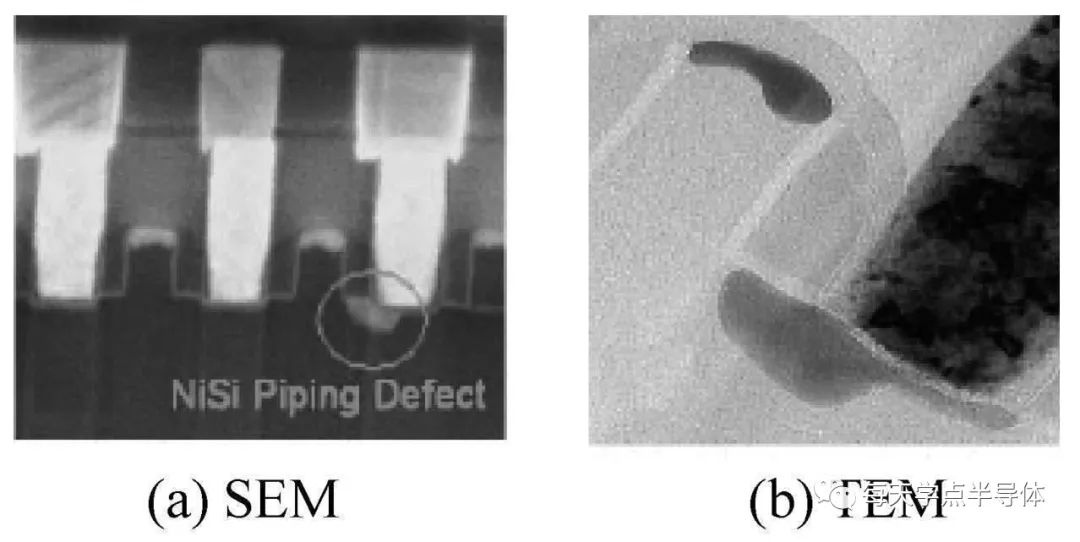

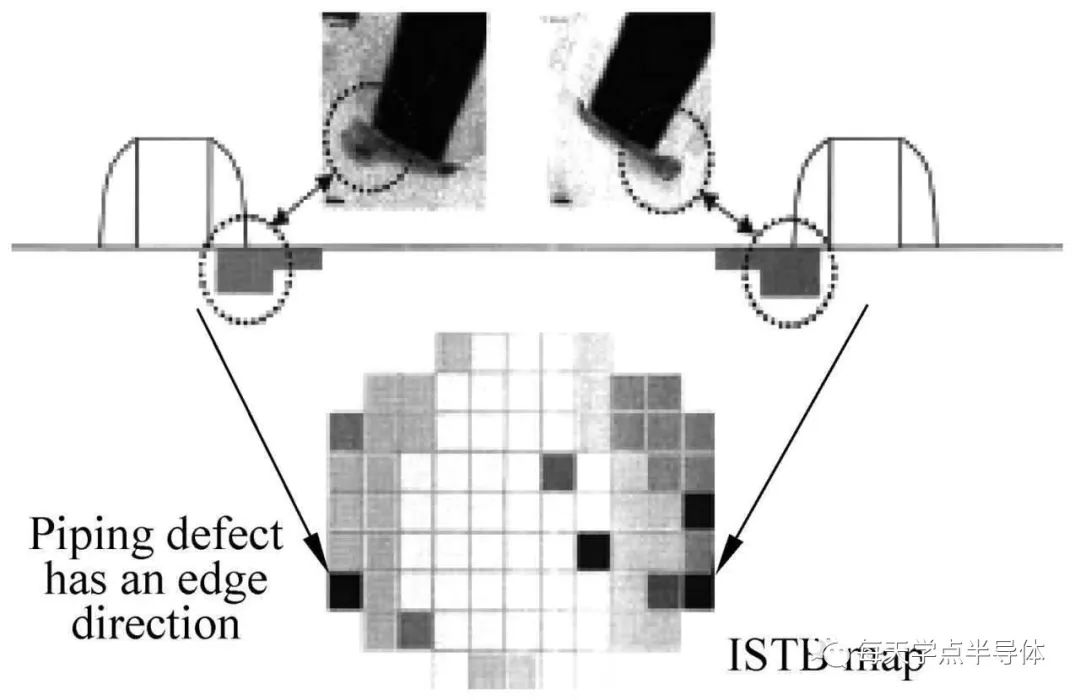

(2)SiCoNi是一種柔和的化學(xué)刻蝕的方式。Ar sputter preclean方式會在反應(yīng)腔內(nèi)產(chǎn)生比較強(qiáng)的plasma,對硅片表面產(chǎn)生強(qiáng)大的轟擊效應(yīng),在除去SiO2的同時,也對硅片表面產(chǎn)生破壞作用,使硅片表面變得粗糙,缺陷增加,在形成硅化物的過程中容易形成尖峰狀缺陷(spiking),見圖6.8(a)。另外,反應(yīng)腔內(nèi)的plasma也會對硅片上的器件產(chǎn)生破壞作用。而SiCoNi采用remote plasma的方式,在反應(yīng)腔內(nèi)沒有plasma,因此,對硅片表面和器件的破壞都較小,消除了尖峰狀缺陷,見圖6.8(b)。

圖6.8 SiCoNi對PMOS上的spiking defect的影響

(3)SiCoNi是一種高選擇性的預(yù)清潔方式,SiO2: Si>20:1,SiO2 : Si3N4>5:1。

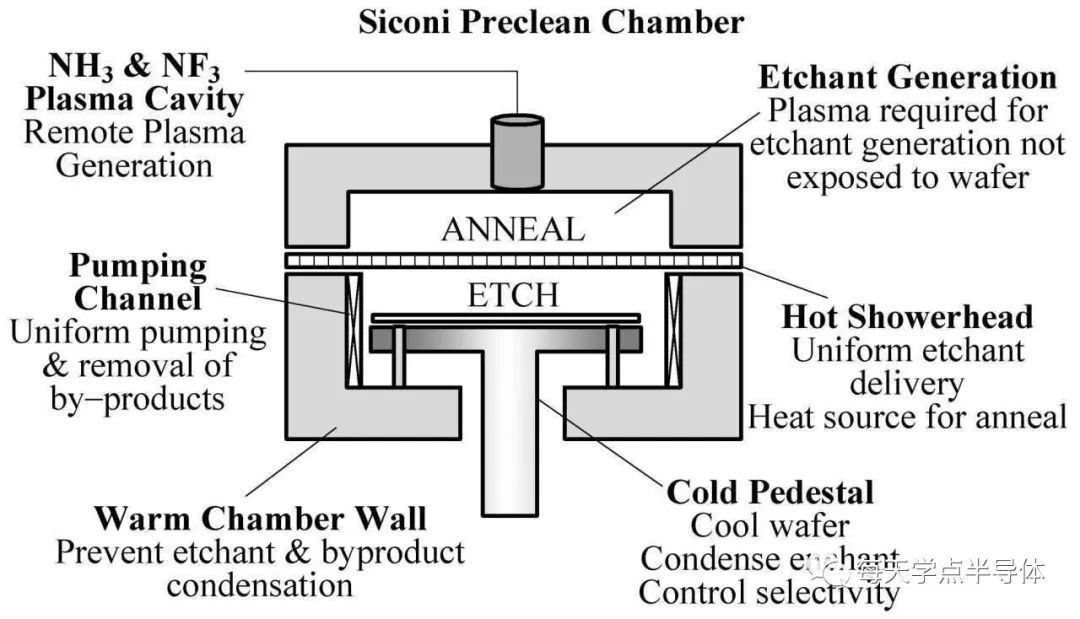

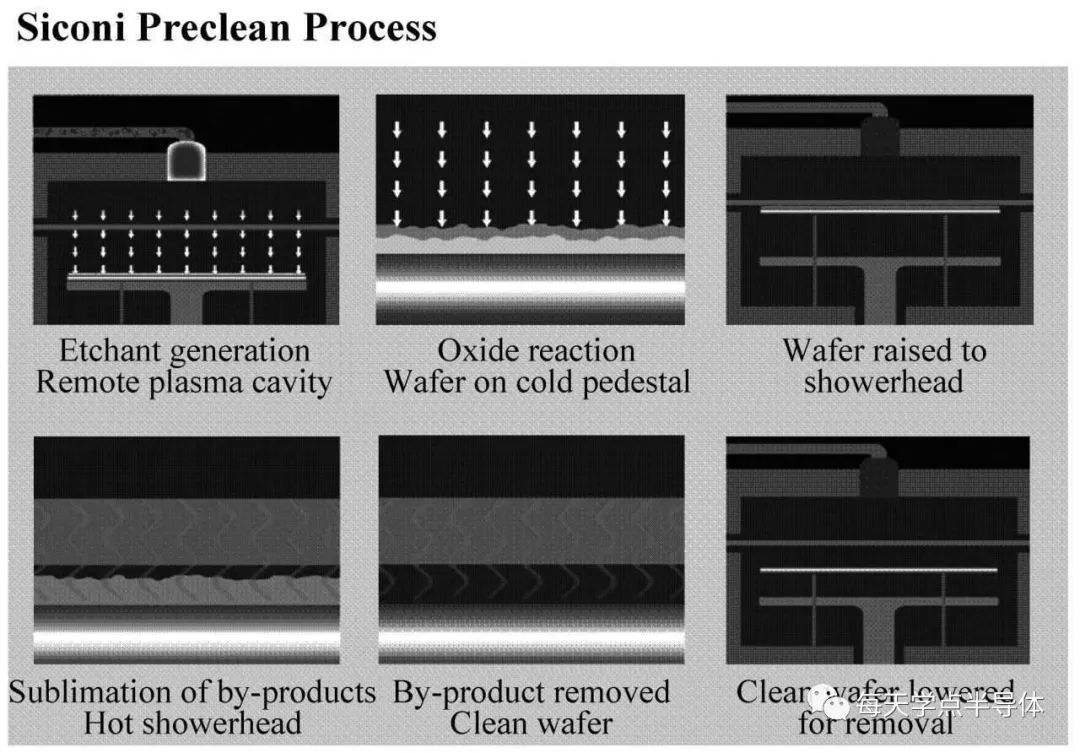

圖6.9為SiCoNi反應(yīng)腔的結(jié)構(gòu),主要包括remote plasma發(fā)生器、hot showerhead、cold pedestal等主要部件。remote plasma產(chǎn)生器的主要作用是將NF3和NH3的混合氣體在plasma作用下生成活性粒子。hot showerhead的溫度為180℃左右,硅片上的SiO2生成易升華的化合物(NH4)2SiF6后,會被升舉而靠近hot showerhead,將(NH4)2SiF6升華。由于(NH4)2SiF6只有在低溫條件下才會生成,因此,cold pedestal的溫度較低,接近室溫,為(NH4)2SiF6的生成提供條件。圖6.10為SiCoNi工藝過程,硅片進(jìn)入反應(yīng)腔后,NF3和NH3的混合氣體在remote plasma發(fā)生器中產(chǎn)生活性粒子,活性粒子進(jìn)入反應(yīng)腔后與 硅片表面的SiO2反應(yīng)生成易升華的化合物(NH4)2SiF6,然后將硅片升舉到hot showerhead附近,利用輻射加熱的方式將硅片表面的(NH4)2SiF6升華,然后由真空泵將氣體抽走。在實際工藝過程中,有時一步升華很難把硅片表面的副產(chǎn)物去除干凈,往往采用兩步或多步升華以達(dá)到徹底除去副產(chǎn)物的目的。

圖6.9 SiCoNi反應(yīng)腔的結(jié)構(gòu)簡圖

圖6.10 SiCoNi的工藝過程

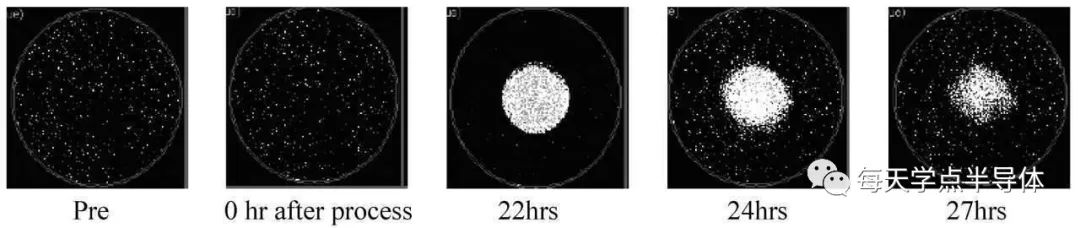

在實際的集成電路制造工藝中,為了確保機(jī)臺在生產(chǎn)產(chǎn)品時不會出現(xiàn)問題,需要定期對機(jī)臺進(jìn)行測試(monitor),對于SiCoNi反應(yīng)腔來說,當(dāng)用長有SiO2的空白硅片測試在工藝過程中的顆粒(particle)缺陷時,發(fā)現(xiàn)將經(jīng)過SiCoNi preclean的硅片放置一段時間之后,在硅片的中心會出現(xiàn)大量的particle,隨著時間的增加,這種particle會自動減少,直至消失,這就是所謂的“幽靈(ghost)”缺陷,見圖6.11,這會影響對機(jī)臺實際狀況的評估。為了克服這個缺陷,得到?jīng)]有g(shù)host效應(yīng)的測試結(jié)果,可采用裸露的硅片作為測試硅片。

圖6.11 ghost效應(yīng)

鎳鉑合金沉積

當(dāng)集成電路技術(shù)發(fā)展到65nm以下時,必須使用Ni silicide。但如果使用純鎳的薄膜作為形成silicide的金屬,由于鎳原子的擴(kuò)散能力很強(qiáng),則會在源漏極上出現(xiàn)如圖6.12所示的侵蝕(encroachment)缺陷。Encroachment缺陷會增加漏電,降低良率。因此,在實際的集成電路制造工藝中,常常采用含鉑5~10atom%的鎳鉑合金作為形成silicide的金屬。

圖6.12 Encroachment缺陷照片

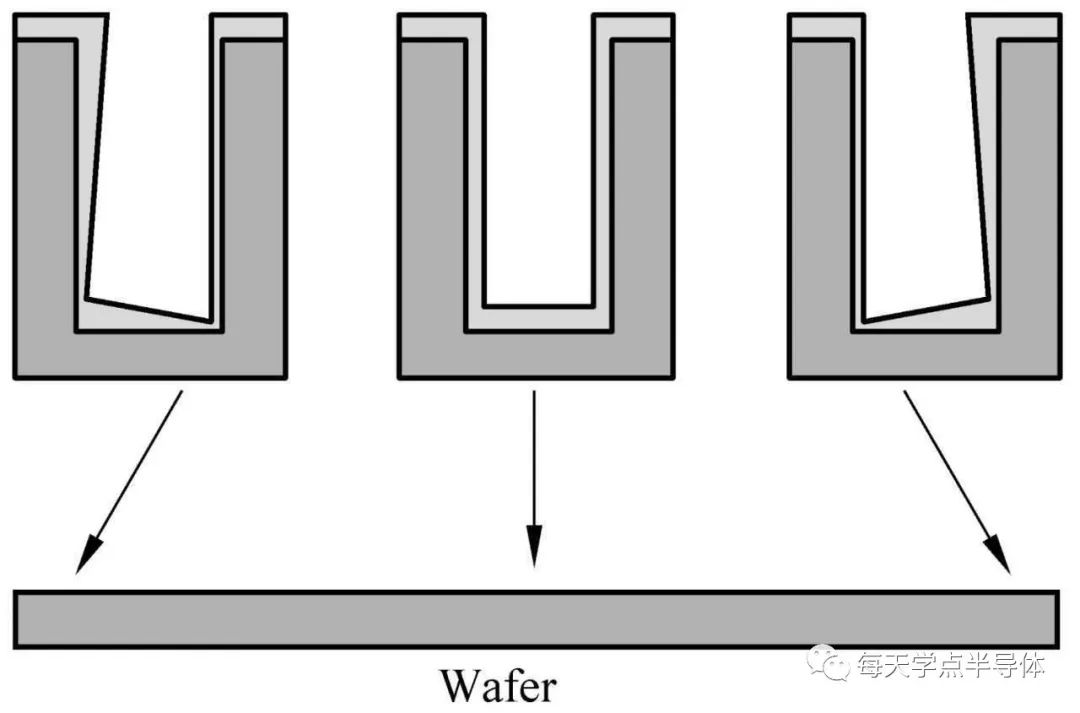

隨著技術(shù)的發(fā)展,除了需要Ni-Pt合金之外,傳統(tǒng)的PVD鍍膜的機(jī)臺已經(jīng)不再滿足制程的需要。尤其是當(dāng)發(fā)展到65nm時,線寬進(jìn)一步縮小,鍍膜之前的深寬比(aspect ratio)進(jìn)一步增加,這就要求鍍Ni-Pt薄膜的機(jī)臺具有比較好的臺階覆蓋率(step coverage),另外,物理氣相沉積長膜方式會受到硅片上幾何結(jié)構(gòu)的影響而存在不對稱性(asymmetry),對于槽(trench)和通孔(via)而言,離硅片中心較遠(yuǎn)的一邊比較容易沉積,厚度較厚,而離硅片中心較近的一邊由于受到側(cè)壁的遮擋效應(yīng)(shadow effect),厚度較薄,如圖6.13所示。在對Ni-Pt薄膜進(jìn)行熱處理形成硅化物的過程中,較厚的一邊所形成的硅化物的厚度較厚,嚴(yán)重的情況下甚至?xí)@到柵極(gate)下面,形成如 圖6.14所示的encroachment defect,增加漏電,嚴(yán)重降低器件的良率。

因此,必須使用型號為ALPS(Advanced Low Pressure Sputtering)的Ni-Pt沉積腔。

圖6.13 Shadow effect和不對稱性

圖6.14 Encroachment缺陷在硅片上的分布

與傳統(tǒng)的PVD相比較,ALPS主要有三個方面的改進(jìn)以增強(qiáng)臺階覆蓋率和降低不對稱性。

(1)增加硅片和靶材之間的距離(long through),使從靶材上濺射出來的大角度的粒子沉積到反應(yīng)腔的側(cè)壁上,只有小角度的粒子可以到達(dá)硅片表面。

(2)降低反應(yīng)壓力(low pressure),壓力越低,氣體分子的平均自由程會越大,粒子的碰撞概率降低,這樣可以確保更具有方向性的沉積。

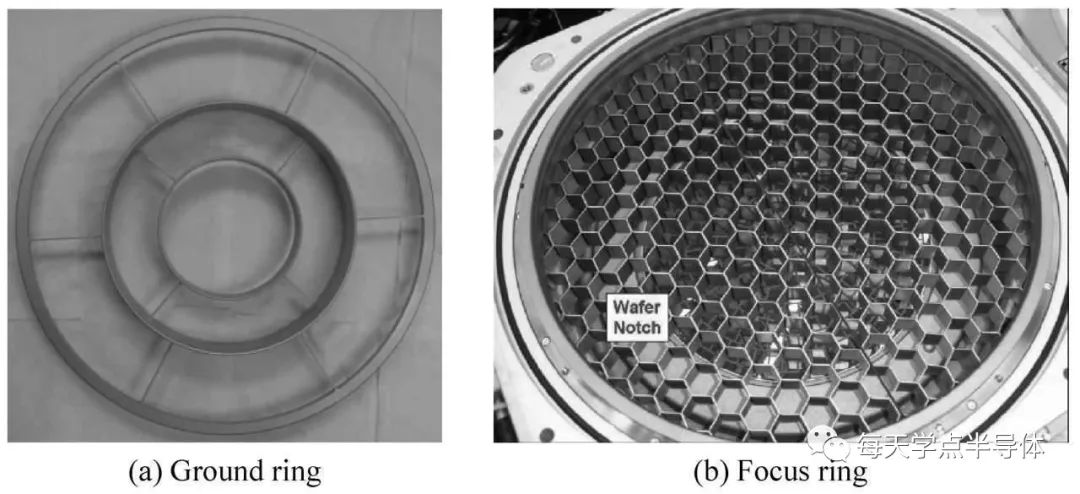

(3)在硅片和靶材之間安裝基環(huán)(ground ring),如圖6.15(a)所示。基環(huán)可以將一些大角度的粒子過濾,確保到達(dá)硅片表面的都是小角度的粒子,以增加階梯覆蓋率和降低不對稱性。當(dāng)制程發(fā)展到45nm時,線寬進(jìn)一步縮小,ALPS不再滿足階梯覆蓋率和不對稱性的要求,此時,需要對ALPS進(jìn)行改進(jìn),采用ALPS ESI(Extend Salicide Integration),用聚焦環(huán)(focus ring)替代基環(huán),見圖6.15(b)。

圖6.15 Ground ring和Focus ring的實物圖

蓋帽層TiN沉積

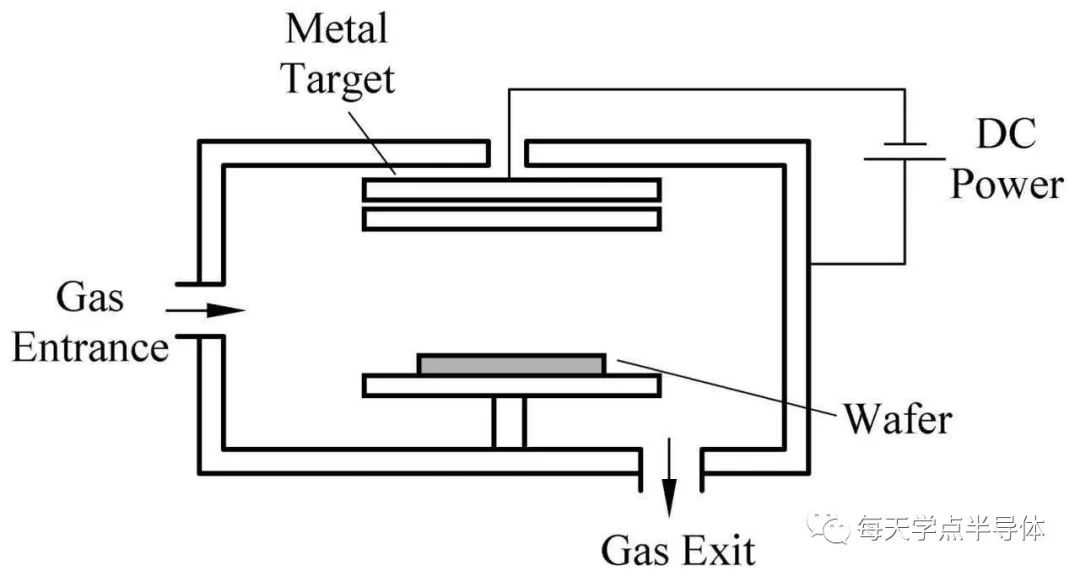

蓋帽層(cap layer)TiN主要是為了保護(hù)Ni-Pt薄膜,對階梯覆蓋率和不對稱性的要求較低,因此,常采用標(biāo)準(zhǔn)的PVD方式,其反應(yīng)腔結(jié)構(gòu)簡圖如圖6.16所示。

圖6.16標(biāo)準(zhǔn)PVD反應(yīng)腔的結(jié)構(gòu)簡圖

審核編輯:黃飛

-

集成電路

+關(guān)注

關(guān)注

5420文章

11983瀏覽量

367502 -

射頻

+關(guān)注

關(guān)注

106文章

5735瀏覽量

169905 -

PVD

+關(guān)注

關(guān)注

4文章

51瀏覽量

17324 -

金屬柵極

+關(guān)注

關(guān)注

0文章

5瀏覽量

5192 -

ALPS

+關(guān)注

關(guān)注

0文章

14瀏覽量

12598

原文標(biāo)題:金屬薄膜沉積工藝及金屬化

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

創(chuàng)碩達(dá)——金屬化聚丙烯薄膜

什么是陶瓷金屬化?斯利通來告訴你!

CL20型金屬化聚酯薄膜電容器

CBB20型交流金屬化聚丙烯薄膜電容器

CBB23型金屬化聚丙烯薄膜電容器

CBB25型金屬化聚丙烯薄膜電容器

金屬化薄膜電容原理結(jié)構(gòu)與使用注意事項

金屬化薄膜電容器474J/684J/105J的特點及用途

一文解析金屬化薄膜電容器的發(fā)展現(xiàn)狀

CBB金屬化薄膜電容器應(yīng)用的優(yōu)勢是什么

基于PVD 薄膜沉積工藝

一文詳解半導(dǎo)體薄膜沉積工藝

一文詳解金屬薄膜沉積工藝及金屬化

一文詳解金屬薄膜沉積工藝及金屬化

評論