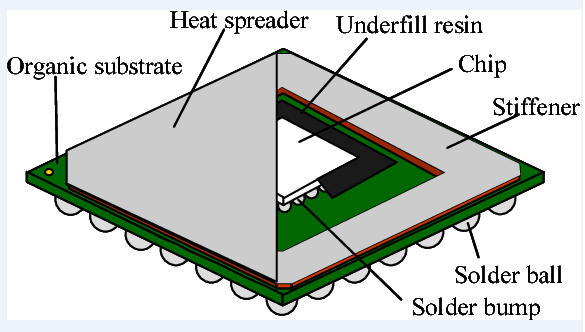

作為全球領(lǐng)先的芯片封測(cè)企業(yè),長(zhǎng)電科技深刻理解先進(jìn)的封裝設(shè)計(jì)能力對(duì)于確保半導(dǎo)體行業(yè)的產(chǎn)品性能、功能和成本至關(guān)重要。大規(guī)模高密度的集成電路為產(chǎn)品設(shè)計(jì)提供了極大的靈活性。例如Chiplet等前沿技術(shù)包含多個(gè)堆疊芯片,通過(guò)中介層上的走線,或特殊的通孔和凸塊來(lái)實(shí)現(xiàn)所需的連接。根據(jù)其工藝規(guī)則獨(dú)立驗(yàn)證這些子芯片和基板的物理連接精度,確保了整個(gè)2.5D/3D封裝組件正確地按預(yù)期運(yùn)行。

長(zhǎng)電科技認(rèn)為,電子設(shè)計(jì)自動(dòng)化EDA工具可對(duì)芯片封裝設(shè)計(jì)中的模塊或芯片中介層接口進(jìn)行快速、準(zhǔn)確的裝配級(jí)驗(yàn)證。這些封裝設(shè)計(jì)技術(shù)不僅使得芯片之間的連接更加緊密和高效,還提供了更大的設(shè)計(jì)自由度和更高的性能潛力。

長(zhǎng)電科技深入掌握這些先進(jìn)的封裝設(shè)計(jì)技術(shù),并將其融入到設(shè)計(jì)中,以滿足客戶對(duì)于更高性能和更小尺寸的需求。長(zhǎng)電科技的先進(jìn)封裝設(shè)計(jì)能力具有以下的優(yōu)勢(shì):

? 快速的上市時(shí)間:設(shè)計(jì)人員可以重用小芯片和經(jīng)典模塊,從而實(shí)現(xiàn)更快的芯片創(chuàng)新并縮短上市時(shí)間;

? 外形尺寸縮小:設(shè)計(jì)人員可以將各種邏輯、內(nèi)存或?qū)S眯酒cSoC集成,為各種應(yīng)用提供更小的外形尺寸;

? 性能和效率提升:封裝設(shè)計(jì)工具將高密度、互連的芯片集成到封裝模塊中,從而提供更高的帶寬、低延遲和理想的電源效率;

? 成本降低:設(shè)計(jì)人員可以在更成熟、更低成本的工藝節(jié)點(diǎn)上重用模擬IO、射頻RF、數(shù)字化大算力等模塊,并將可擴(kuò)展的邏輯設(shè)計(jì)集中在最先進(jìn)的節(jié)點(diǎn)上。

長(zhǎng)電科技的芯片封裝設(shè)計(jì)服務(wù),致力于提供一流的自動(dòng)化設(shè)計(jì)解決方案,為客戶項(xiàng)目注入創(chuàng)新活力和效率,降低設(shè)計(jì)風(fēng)險(xiǎn)和成本。

自動(dòng)化設(shè)計(jì)

公司采用最先進(jìn)的自動(dòng)化設(shè)計(jì)技術(shù)JedAI,利用EDA最新軟件工具和流程,通過(guò)定制增強(qiáng)功能模塊的使用,實(shí)現(xiàn)高效而精確的芯片封裝設(shè)計(jì),提高設(shè)計(jì)效率,確保設(shè)計(jì)的一致性,準(zhǔn)確性和可靠性。

先進(jìn)封裝協(xié)同設(shè)計(jì)

積極采用2.5D-RDL芯片封裝技術(shù)、3D芯片堆疊封裝設(shè)計(jì)等技術(shù),提高芯片的集成度,為客戶項(xiàng)目帶來(lái)更多可能性。

DFM滿足制造生產(chǎn)要求

通過(guò)應(yīng)用DFM,芯片封裝設(shè)計(jì)更好地滿足制造要求,降低制造風(fēng)險(xiǎn)和成本。

設(shè)計(jì)規(guī)則的嚴(yán)格檢查

通過(guò)DRC設(shè)計(jì)規(guī)則檢查以確保設(shè)計(jì)的合規(guī)性和可靠性。通過(guò)嚴(yán)格的規(guī)則檢查流程,及早發(fā)現(xiàn)和解決潛在的設(shè)計(jì)問(wèn)題。

物理驗(yàn)證與芯片參數(shù)提取

芯片封裝物理參數(shù)提取是長(zhǎng)電科技的一項(xiàng)專業(yè)服務(wù)。公司嚴(yán)格遵循標(biāo)準(zhǔn)流程,確保芯片封裝的物理參數(shù)的準(zhǔn)確提取和驗(yàn)證。

Chiplet規(guī)劃與IO對(duì)齊

精心規(guī)劃Chiplet,確保它們?cè)谠O(shè)計(jì)中無(wú)縫對(duì)齊,以實(shí)現(xiàn)更佳性能和穩(wěn)定性。以此能夠提供更靈活、高效和可靠的芯片設(shè)計(jì)方案。

LVS邏輯檢查和驗(yàn)證

通過(guò)LVS邏輯檢查,保證設(shè)計(jì)的邏輯一致性,消除潛在問(wèn)題,確保每一個(gè)芯片的正常運(yùn)行和性能表現(xiàn),從而為客戶提供高質(zhì)量的設(shè)計(jì)解決方案。

長(zhǎng)電科技始終堅(jiān)持提升設(shè)計(jì)質(zhì)量、提高設(shè)計(jì)效率、降低設(shè)計(jì)風(fēng)險(xiǎn)和成本的目標(biāo),將不斷努力推動(dòng)封裝設(shè)計(jì)技術(shù)的創(chuàng)新和進(jìn)步,以滿足客戶的多樣化需求。

長(zhǎng)電科技是全球領(lǐng)先的集成電路制造和技術(shù)服務(wù)提供商,提供全方位的芯片成品制造一站式服務(wù),包括集成電路的系統(tǒng)集成、設(shè)計(jì)仿真、技術(shù)開(kāi)發(fā)、產(chǎn)品認(rèn)證、晶圓中測(cè)、晶圓級(jí)中道封裝測(cè)試、系統(tǒng)級(jí)封裝測(cè)試、芯片成品測(cè)試并可向世界各地的半導(dǎo)體客戶提供直運(yùn)服務(wù)。

通過(guò)高集成度的晶圓級(jí)(WLP)、2.5D/3D、系統(tǒng)級(jí)(SiP)封裝技術(shù)和高性能的倒裝芯片和引線互聯(lián)封裝技術(shù),長(zhǎng)電科技的產(chǎn)品、服務(wù)和技術(shù)涵蓋了主流集成電路系統(tǒng)應(yīng)用,包括網(wǎng)絡(luò)通訊、移動(dòng)終端、高性能計(jì)算、車載電子、大數(shù)據(jù)存儲(chǔ)、人工智能與物聯(lián)網(wǎng)、工業(yè)智造等領(lǐng)域。長(zhǎng)電科技在中國(guó)、韓國(guó)和新加坡設(shè)有六大生產(chǎn)基地和兩大研發(fā)中心,在20多個(gè)國(guó)家和地區(qū)設(shè)有業(yè)務(wù)機(jī)構(gòu),可與全球客戶進(jìn)行緊密的技術(shù)合作并提供高效的產(chǎn)業(yè)鏈支持。

審核編輯:湯梓紅

-

芯片封裝

+關(guān)注

關(guān)注

11文章

576瀏覽量

31393 -

封裝設(shè)計(jì)

+關(guān)注

關(guān)注

2文章

46瀏覽量

12057 -

長(zhǎng)電科技

+關(guān)注

關(guān)注

5文章

376瀏覽量

32900

原文標(biāo)題:長(zhǎng)電科技:自動(dòng)化與創(chuàng)新科技,邁向封裝設(shè)計(jì)的未來(lái)

文章出處:【微信號(hào):gh_0837f8870e15,微信公眾號(hào):長(zhǎng)電科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

長(zhǎng)電科技江陰成立子公司聚焦先進(jìn)封裝

MUN12AD03-SEC的封裝設(shè)計(jì)對(duì)散熱有何影響?

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

整流橋關(guān)鍵參數(shù)與封裝設(shè)計(jì)的關(guān)聯(lián)都有哪些?

封裝設(shè)計(jì)圖紙的基本概念和類型

如何通俗理解芯片封裝設(shè)計(jì)

集成電路封裝設(shè)計(jì)為什么需要Design Rule

臺(tái)積電擴(kuò)大先進(jìn)封裝設(shè)施,南科等地將增建新廠

聯(lián)電獲得高通高性能計(jì)算先進(jìn)封裝大單

聯(lián)電拿下高通訂單!先進(jìn)封裝不再一家獨(dú)大

長(zhǎng)電華天萬(wàn)年芯,國(guó)內(nèi)半導(dǎo)體封裝領(lǐng)域隱藏的好企業(yè)

長(zhǎng)電科技深耕5G通信領(lǐng)域,提供芯片封裝解決方案

持續(xù)拓展汽車電子 長(zhǎng)電科技把握新機(jī)遇

長(zhǎng)電科技先進(jìn)封裝設(shè)計(jì)能力的優(yōu)勢(shì)

長(zhǎng)電科技先進(jìn)封裝設(shè)計(jì)能力的優(yōu)勢(shì)

評(píng)論