封裝設(shè)計是集成電路(IC)生產(chǎn)過程中至關(guān)重要的一環(huán),它決定了芯片的功能性、可靠性和制造工藝。

1.封裝設(shè)計的總體目標(biāo)

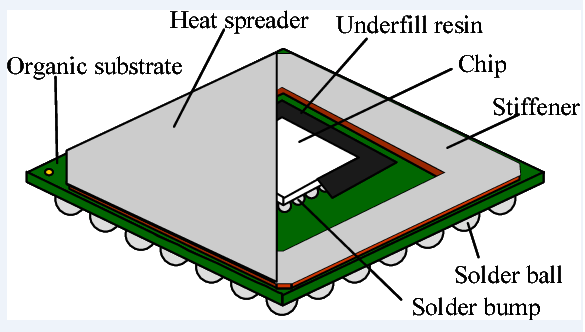

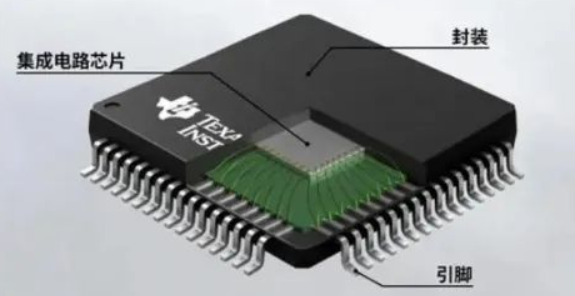

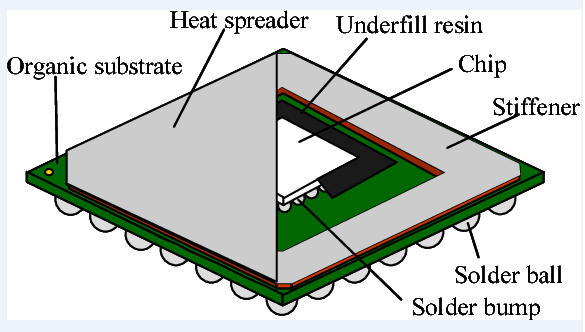

封裝設(shè)計的主要目標(biāo)是為芯片提供機(jī)械保護(hù)、電氣連接以及熱管理等功能,確保芯片在使用過程中穩(wěn)定工作。通過封裝,芯片與外部系統(tǒng)建立電氣互連和機(jī)械連接,同時要保證芯片能有效散熱。

類比來說,封裝就像是芯片的“外殼”和“支架”,它不僅保護(hù)芯片免受外界環(huán)境的損害,還幫助芯片與外部設(shè)備進(jìn)行信息交換。

2.芯片布局與裝片設(shè)計

在封裝設(shè)計中,芯片布局是核心任務(wù)之一。芯片的排布方式與封裝的尺寸、芯片的數(shù)量和尺寸等因素緊密相關(guān)。常見的布局方式包括:

平鋪式布局

- :適用于芯片面積較小且需要較大封裝空間的情況。所有芯片都在同一平面上并排放置。

堆疊式布局

- :當(dāng)芯片數(shù)量多、尺寸大時,通常會采用在垂直方向上堆疊的方式,以充分利用空間,避免芯片之間或芯片到封裝邊緣的距離過小。

混合式布局

- :當(dāng)平鋪和堆疊結(jié)合使用時,能夠兼顧空間利用和制造可行性,常見于高集成度的系統(tǒng)級封裝(SiP)。

例如,系統(tǒng)級封裝(SiP)中,不同功能的芯片往往需要按不同的布局進(jìn)行合理分配,從而達(dá)到功能整合和散熱需求的平衡。

3.元器件排布與集成密度

當(dāng)集成電路設(shè)計中元器件密度較高時,元器件之間的距離就顯得尤為重要。較小的間距有助于提高系統(tǒng)的集成度和功能密度,但需要確保制程的可行性。例如,多個無源元器件和晶片通過合理的布局和設(shè)計,可以在保持高集成度的同時避免相互干擾。

這個過程就像在一個緊湊的空間中合理安排家具和物品,既要考慮每個物品的功能,又要確保每個物品之間有足夠的空間,避免產(chǎn)生不必要的沖突或問題。

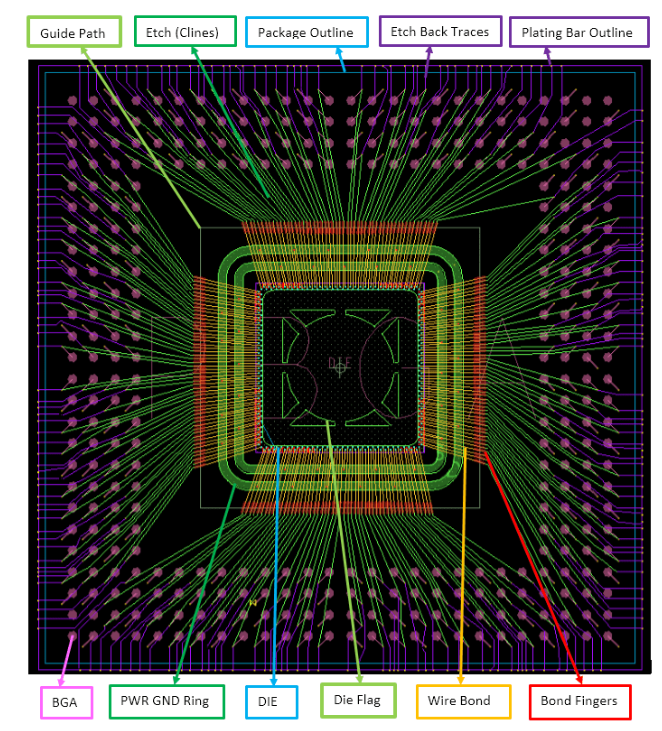

4.引線鍵合設(shè)計

引線鍵合(Wire Bonding)是一種經(jīng)典的芯片互連技術(shù),廣泛應(yīng)用于各類封裝中。通過將引線與芯片的焊盤連接,將芯片電氣信號傳遞至外部電路。隨著封裝的復(fù)雜度增加,引線鍵合設(shè)計的難度也隨之增加。

選擇合適的線型和直徑

- :根據(jù)芯片尺寸、功率要求和封裝類型,選擇不同的線材類型(如金線、鋁線等)及其直徑,確保良好的電氣性能和熱傳導(dǎo)能力。

連接方式設(shè)計

- :在芯片的不同位置進(jìn)行合理的引線布局,如處理角落處的線彎和堆疊芯片的連接,避免線彎過度導(dǎo)致連接不穩(wěn)定。

就像我們給電器接線一樣,要確保線纜的長度、粗細(xì)、彎曲角度等合適,避免電流流動不暢或出現(xiàn)電路故障。

5.倒裝芯片(FC)技術(shù)

倒裝芯片(Flip Chip, FC)技術(shù)與傳統(tǒng)的引線鍵合不同,它通過將芯片倒裝,使芯片的電極直接與基板上的焊盤接觸,從而實現(xiàn)電氣連接。FC技術(shù)的優(yōu)勢在于:

更好的電學(xué)性能

更小的封裝尺寸

- :由于沒有引線的連接空間,F(xiàn)C封裝可以做得更小、更緊湊,適應(yīng)高密度集成的需求。

更好的熱管理

- :FC技術(shù)有利于熱量的快速傳導(dǎo),使得芯片能夠更有效地散熱,避免過熱問題。

可以把倒裝芯片技術(shù)想象成將芯片“翻轉(zhuǎn)過來”,直接與基板連接,就像在做拼圖時,把拼圖的圖片面朝下拼接在一起,省去了多余的連接步驟,使整個過程更加簡潔和高效。

6.封裝設(shè)計與系統(tǒng)級優(yōu)化

封裝設(shè)計不僅僅是考慮單個芯片的連接和散熱問題,它還需要綜合考慮整個系統(tǒng)的需求。比如在系統(tǒng)級封裝(SiP)中,多個不同功能的芯片和器件集成在同一個封裝中時,設(shè)計師需要關(guān)注電氣性能、機(jī)械強(qiáng)度和熱管理的多重因素,從而確保整個系統(tǒng)的穩(wěn)定性和可靠性。

這就像在組裝一臺多功能的電子設(shè)備時,每個元器件都有其特定功能,如何在有限的空間內(nèi)有效集成并優(yōu)化其性能是封裝設(shè)計的關(guān)鍵。

總結(jié):封裝設(shè)計是集成電路制造過程中至關(guān)重要的一環(huán),它不僅決定了芯片的電氣性能,還直接影響其散熱能力、物理強(qiáng)度和生產(chǎn)工藝的可行性。從芯片的布局、引線鍵合到倒裝芯片技術(shù),每一個設(shè)計細(xì)節(jié)都在影響最終產(chǎn)品的穩(wěn)定性和性能。在面對復(fù)雜的集成需求時,封裝設(shè)計需要綜合考慮各種因素,才能確保產(chǎn)品滿足各項性能要求。

聲明:

本號對所有原創(chuàng)、轉(zhuǎn)載文章的陳述與觀點均保持中立,推送文章僅供讀者學(xué)習(xí)和交流。文章、圖片等版權(quán)歸原作者享有,如有侵權(quán),聯(lián)系刪除。

-

集成電路

+關(guān)注

關(guān)注

5421文章

12012瀏覽量

367827 -

芯片封裝

+關(guān)注

關(guān)注

11文章

576瀏覽量

31358 -

封裝設(shè)計

+關(guān)注

關(guān)注

2文章

46瀏覽量

12051

發(fā)布評論請先 登錄

半導(dǎo)體后端工藝:封裝設(shè)計與分析

芯片封裝設(shè)計中的wire_bonding知識介紹

需要led 芯片設(shè)計,封裝設(shè)計的模擬軟件的聯(lián)系我

為什么需要封裝設(shè)計?

為什么需要封裝設(shè)計?

芯片封裝設(shè)計

RedEDA使用教程(芯片封裝設(shè)計RedPKG)

為什么需要封裝設(shè)計?封裝設(shè)計做什么?

如何通俗理解芯片封裝設(shè)計

如何通俗理解芯片封裝設(shè)計

評論