摩爾定律走下神壇,誰會(huì)是芯片下一個(gè)制勝法則?

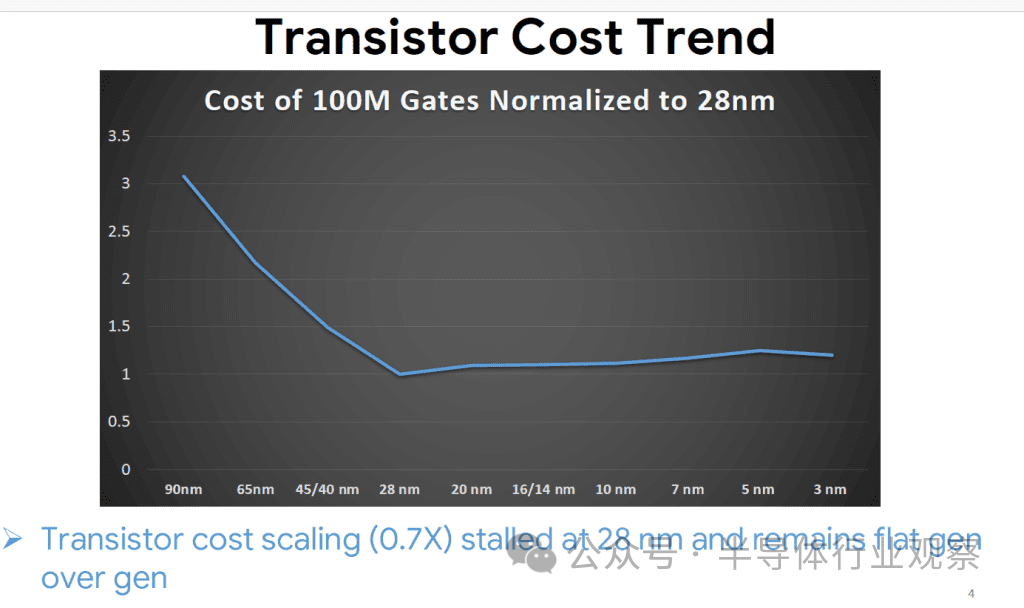

在動(dòng)態(tài)的半導(dǎo)體技術(shù)領(lǐng)域,圍繞摩爾定律的持續(xù)討論經(jīng)歷了顯著的演變,其中最突出的是 MonolithIC 3D 首席執(zhí)行官Zvi Or-Bach于2014 年的主張。他關(guān)于晶體管成本縮減在 28 nm 達(dá)到關(guān)鍵節(jié)點(diǎn)的說法引起了廣泛關(guān)注。

最近,谷歌的 Milind Shah 在 IEDM 2023 的短期課程中驗(yàn)證了這一說法。這一明確的說法“晶體管成本縮放 (0.7 倍) 在 28 納米處停滯不前,并且一代一代之間保持持平”,這證實(shí)了之前的說法。最初在 2014 年的公眾觀點(diǎn)和博客中預(yù)見到了摩爾定律的結(jié)論。

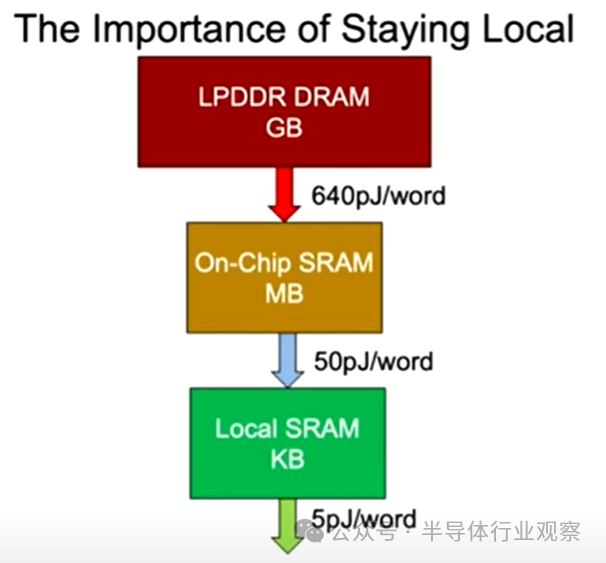

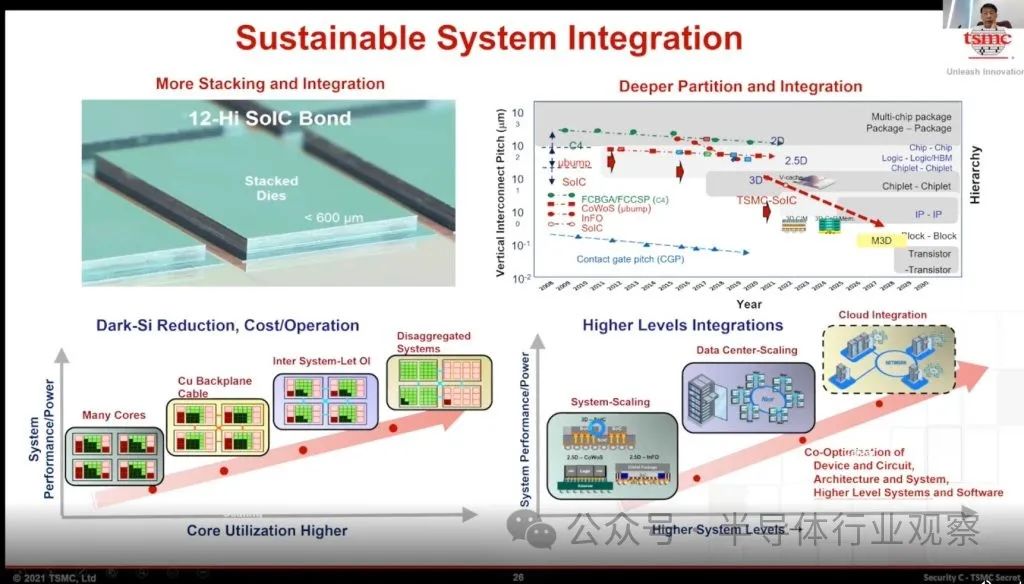

盡管成本擴(kuò)展停滯不前,為什么業(yè)界仍在推動(dòng)更小的晶體管,目標(biāo)是令人難以置信的 1 nm 節(jié)點(diǎn)?答案在于系統(tǒng)級(jí)的好處。正如 NVIDIA 首席科學(xué)家 Bill Dally 的圖表所示。

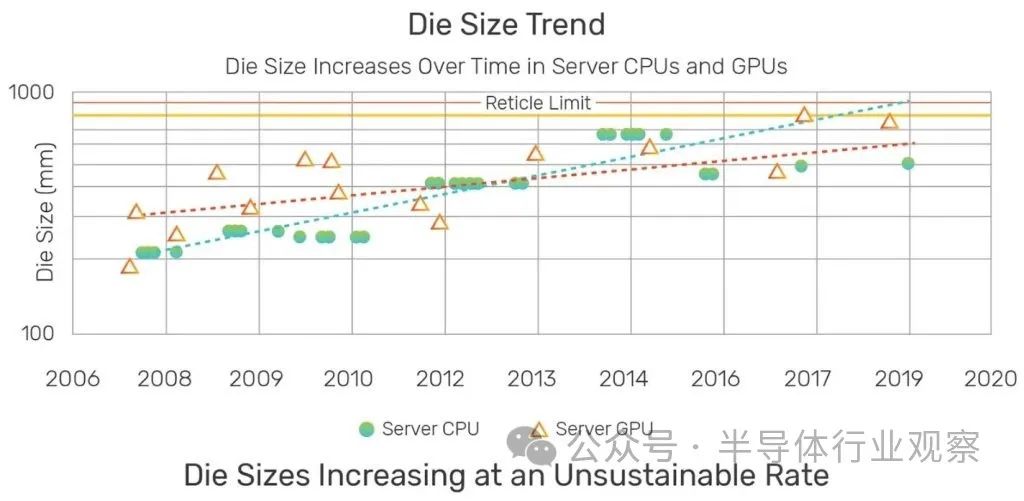

這反過來又推動(dòng)了 CPU 和 GPU 等領(lǐng)先計(jì)算設(shè)備達(dá)到甚至更大尺寸的趨勢(shì)。對(duì)更小節(jié)點(diǎn)的追求使得芯片上的組件集成更加緊密,從而進(jìn)一步提高性能和效率。

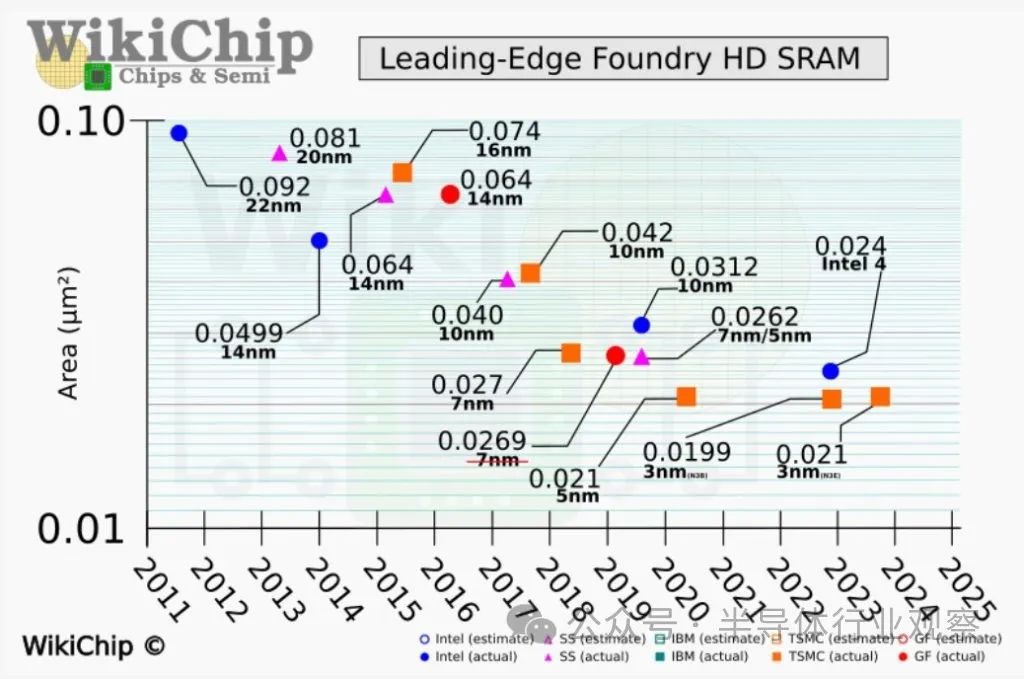

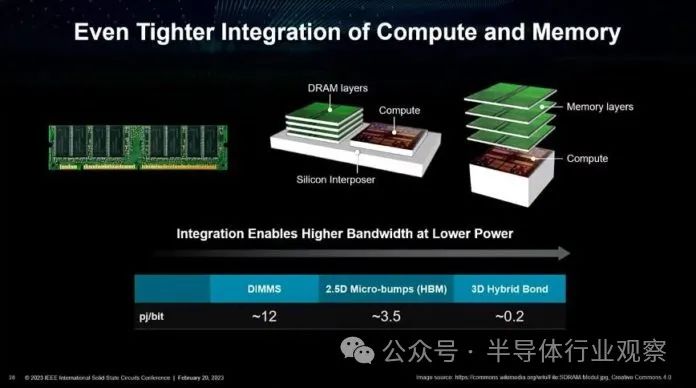

不幸的是,邏輯和存儲(chǔ)器(DRAM、NAND)制造工藝非常不同。因此,它們是在不同的晶圓上生產(chǎn)的并且不能通過縮放來集成。更糟糕的是,SRAM 位單元縮放已停止在 5 納米節(jié)點(diǎn)。

AMD 和臺(tái)積電似乎都 了解這些趨勢(shì),并在過去幾年中采用了混合鍵合技術(shù),以實(shí)現(xiàn)未來計(jì)算性能的進(jìn)步。

雖然當(dāng)前的實(shí)施(例如 AMD 的 3D V-Cache)是充分發(fā)揮 3D 集成潛力的墊腳石,但仍然存在重大障礙。其中包括架構(gòu)思維的根本轉(zhuǎn)變,從傳統(tǒng)的邊緣互連轉(zhuǎn)向新穎的 3D 集成方法。此外,要實(shí)現(xiàn)廣泛采用,還需要在系統(tǒng)級(jí)冗余、晶圓級(jí)集成、甚至片上射頻網(wǎng)絡(luò)方面進(jìn)行創(chuàng)新

拯救摩爾定律的終極辦法

正如IMEC負(fù)責(zé)計(jì)算擴(kuò)展的邏輯副總裁Julien Ryckaert所說:“整個(gè)半導(dǎo)體行業(yè)目前正在經(jīng)歷一場(chǎng)巨大的變革。十多年來,很明顯,受摩爾定律(更具體地說是登納德定律)啟發(fā)的尺寸縮放不能用作預(yù)測(cè) CMOS 技術(shù)節(jié)點(diǎn)未來的晴雨表。”

這源于我們現(xiàn)在稱為“縮放墻”的幾個(gè)因素。不僅擴(kuò)展 CMOS 組件的特征尺寸變得極其困難和昂貴,而且行業(yè)在其復(fù)雜系統(tǒng)中也面臨著嚴(yán)重的功率和速度障礙。

在技術(shù)層面,新的器件架構(gòu)和縮放助推器——由設(shè)計(jì)技術(shù)協(xié)同優(yōu)化 (DTCO) 支持——可以在接下來的幾個(gè) CMOS 節(jié)點(diǎn)中保持一定的面積縮放。但是這些將不可避免地失去動(dòng)力,或者至少不足以提供未來應(yīng)用程序的系統(tǒng)擴(kuò)展期望。

在架構(gòu)級(jí)別,復(fù)雜的內(nèi)存層次結(jié)構(gòu)、多核和多線程以及單個(gè)片上系統(tǒng) (SoC) 或小芯片中的核心專業(yè)化 (xPUs...) 已成為克服這些擴(kuò)展的方法墻壁。

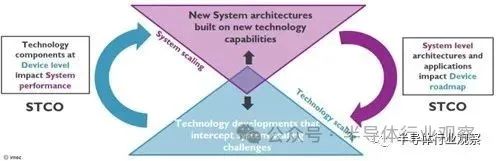

“我們今天面臨的問題是,早期的創(chuàng)新很少是真正的系統(tǒng)架構(gòu)到技術(shù)優(yōu)化循環(huán)的結(jié)果。向前邁進(jìn)的最大挑戰(zhàn)將是解決可以解決主要系統(tǒng)擴(kuò)展瓶頸的正確技術(shù)成分,以及探索一些技術(shù)中斷如何能夠?qū)崿F(xiàn)新的計(jì)算方式。這就是系統(tǒng)技術(shù)協(xié)同優(yōu)化 (STCO) 框架的目的。”Julien Ryckaert接著說。

在IMEC看來,由于自身需要在定義未來技術(shù)方面處于領(lǐng)先地位,因此他們現(xiàn)在必須通過系統(tǒng)擴(kuò)展挑戰(zhàn)來豐富其技術(shù)路線圖。這種演變從根本上意味著我們需要跳出傳統(tǒng)的“通用”技術(shù)產(chǎn)品,接受這樣一個(gè)事實(shí),即解決方案是由如人工智能、高性能計(jì)算 (HPC)和增強(qiáng)現(xiàn)實(shí)/虛擬現(xiàn)實(shí)等特定應(yīng)用需求驅(qū)動(dòng)的。

此外,最佳系統(tǒng)實(shí)施將是跨多種技術(shù)(例如極端 CMOS 邏輯縮放、高級(jí) 3D 封裝、新型存儲(chǔ)元件甚至 Si 光子學(xué))的微妙優(yōu)化的結(jié)果。到目前為止,這些不同的技術(shù)研究活動(dòng)是分別進(jìn)行的,每個(gè)活動(dòng)都有自己的 DTCO 研究和路線圖。

為了為系統(tǒng)驅(qū)動(dòng)的擴(kuò)展過渡做好準(zhǔn)備,IMEC重組了核心項(xiàng)目,并將所有 DTCO 活動(dòng)整合到一個(gè)項(xiàng)目中,該項(xiàng)目將研究所有核心技術(shù)項(xiàng)目中的技術(shù)到電路優(yōu)化,并用 STCO 計(jì)劃補(bǔ)充了這個(gè) DTCO 計(jì)劃,這將確保 DTCO 研究和系統(tǒng)應(yīng)用空間之間的聯(lián)系。

“此 STCO 計(jì)劃的目標(biāo)是以自上而下的方式將未來的系統(tǒng)需求和瓶頸轉(zhuǎn)化為技術(shù)需求。它還將探索利用獨(dú)特和新穎的技術(shù)能力啟用新架構(gòu)的可能性。”Julien Ryckaert說。

據(jù)他所說,在IMEC的每個(gè)核心技術(shù)項(xiàng)目中,都開始了獨(dú)立的研究活動(dòng),這些活動(dòng)已經(jīng)需要一定程度的系統(tǒng)評(píng)估。

一個(gè)很好的例子是其在 2022 年 VLSI 研討會(huì)上展示的背面供電網(wǎng)絡(luò)。這項(xiàng)工作是 3D 程序活動(dòng)和邏輯活動(dòng)共同開發(fā)電力傳輸系統(tǒng)解決方案的結(jié)果。背面技術(shù)嚴(yán)重影響邏輯縮放路線圖,因?yàn)樗枰?3D 技術(shù)功能,例如晶圓處理和硅通孔 (TSV) 處理。但要了解背面供電網(wǎng)絡(luò)為何以及如何帶來真正的系統(tǒng)性能優(yōu)勢(shì),需要評(píng)估其在更復(fù)雜環(huán)境中的行為,并深入研究系統(tǒng)配置。

另一個(gè)例子是新興存儲(chǔ)器,其中一些預(yù)計(jì)將取代片上 SRAM。這樣的內(nèi)存方案必然會(huì)影響邏輯縮放路線圖,只能在系統(tǒng)仿真框架中進(jìn)行評(píng)估。更不用說其中一些記憶可能會(huì)以 3D 方式堆疊。

當(dāng)我們開始為這些示例解決系統(tǒng)級(jí)挑戰(zhàn)時(shí),我們很快意識(shí)到,對(duì)于每個(gè)示例,所有技術(shù)解決方案都相互糾纏在一起。很明顯,邏輯、內(nèi)存和 3D 程序中的技術(shù)研究不能再在單獨(dú)的“孤島”中處理:它必須同時(shí)完成并由系統(tǒng)應(yīng)用程序目標(biāo)驅(qū)動(dòng)。

”好消息是我們不是從頭開始,因?yàn)槲覀円呀?jīng)有許多從系統(tǒng)角度分析的研究活動(dòng)。我們現(xiàn)在需要的是將這些活動(dòng)組織成一個(gè)共同的愿景,并為它們制定路線圖。”Julien Ryckaert表示。

Julien Ryckaert進(jìn)一步指出,IMEC的 DTCO/STCO 活動(dòng)圍繞系統(tǒng)的 3 個(gè)基本擴(kuò)展壁進(jìn)行了闡述:內(nèi)存/帶寬壁(即,如何以足夠的速度獲取數(shù)據(jù)以饋送邏輯內(nèi)核)、功率/熱壁(即,如何有效地處理功率傳輸和散熱)和尺寸縮放墻。

IMEC希望能與其合作伙伴一起校準(zhǔn)這個(gè)研究路線圖,并確保我們正在為行業(yè)應(yīng)對(duì)正確的挑戰(zhàn)。這將需要與所有的合作伙伴進(jìn)行深入討論,而這些已經(jīng)開始進(jìn)行。

Julien Ryckaert表示:“盡管人們和我們一樣認(rèn)為這是一個(gè)雄心勃勃的計(jì)劃目標(biāo),但我們確實(shí)看到了圍繞這一倡議的很多興奮。我們必須明智地選擇我們的戰(zhàn)斗,那些與未來系統(tǒng)擴(kuò)展最相關(guān)的戰(zhàn)斗,同時(shí)利用我們獨(dú)特的技術(shù)能力。”

在他看來,真正的 STCO 研究需要將許多學(xué)科整合在一起,每個(gè)學(xué)科都處理廣泛不同的規(guī)模,并在不同的抽象領(lǐng)域運(yùn)作他們的科學(xué)。一個(gè)真正的挑戰(zhàn)是在不丟失關(guān)鍵信息的情況下,構(gòu)建從一個(gè)域到另一個(gè)域的一組適當(dāng)?shù)某橄髮印_@是從上到下和從下到上傳播信息以執(zhí)行完整系統(tǒng)優(yōu)化的唯一方法。

而要正確地做到這一點(diǎn),您不僅需要每個(gè)領(lǐng)域的所有正確專業(yè)知識(shí),而且還需要這些學(xué)科彼此密切互動(dòng)。Imec 擁有獨(dú)特的基礎(chǔ)設(shè)施,其中大多數(shù)學(xué)科都在同一屋檐下緊密合作。這有助于思想的交流、信息的順利傳播以及擴(kuò)大對(duì)結(jié)果和解釋的批判眼光。

“我對(duì)在這個(gè) STCO 領(lǐng)域向前邁進(jìn)感到非常興奮,因?yàn)槲覀兯腥耍瑹o論我們來自哪個(gè)領(lǐng)域,都明白在未來半導(dǎo)體研究中發(fā)揮作用的將是通過 STCO 框架。而 imec 是這種計(jì)劃起飛的合適地點(diǎn)。”Julien Ryckaer說。

審核編輯:黃飛

-

cpu

+關(guān)注

關(guān)注

68文章

11057瀏覽量

216349 -

摩爾定律

+關(guān)注

關(guān)注

4文章

638瀏覽量

79744 -

gpu

+關(guān)注

關(guān)注

28文章

4923瀏覽量

130847 -

晶體管

+關(guān)注

關(guān)注

77文章

9995瀏覽量

141026 -

28nm

+關(guān)注

關(guān)注

0文章

173瀏覽量

95104

原文標(biāo)題:摩爾定律止步28nm

文章出處:【微信號(hào):WW_CGQJS,微信公眾號(hào):傳感器技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

TMD或?qū)⑷〈鶶i,下一代半導(dǎo)體材料來襲

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

電力電子中的“摩爾定律”(1)

玻璃基板在芯片封裝中的應(yīng)用

瑞沃微先進(jìn)封裝:突破摩爾定律枷鎖,助力半導(dǎo)體新飛躍

納米壓印技術(shù):開創(chuàng)下一代光刻的新篇章

混合鍵合中的銅連接:或成摩爾定律救星

石墨烯互連技術(shù):延續(xù)摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

后摩爾定律時(shí)代,提升集成芯片系統(tǒng)化能力的有效途徑有哪些?

觀點(diǎn)評(píng)論 | 芯片行業(yè),神奇的一年

使用tSPI協(xié)議減少下一個(gè)多電機(jī)BLDC設(shè)計(jì)的布線

高算力AI芯片主張“超越摩爾”,Chiplet與先進(jìn)封裝技術(shù)迎百家爭(zhēng)鳴時(shí)代

摩爾定律的終結(jié):芯片產(chǎn)業(yè)的下一個(gè)勝者法則是什么?

摩爾定律的終結(jié):芯片產(chǎn)業(yè)的下一個(gè)勝者法則是什么?

評(píng)論