FPGA(現(xiàn)場可編程門陣列)和RISC-V處理器在多個方面存在顯著的區(qū)別。

首先,F(xiàn)PGA是一種可編程的硬件設(shè)備,它包含大量的邏輯單元和可編程連接資源,可以根據(jù)用戶的需求進(jìn)行動態(tài)配置,實現(xiàn)不同的邏輯功能。它本身并不執(zhí)行程序,而是通過編程來定義其內(nèi)部的電路結(jié)構(gòu)和邏輯功能。FPGA具有高度的靈活性和可重新配置性,可以適應(yīng)各種變化的應(yīng)用需求。

而RISC-V是一種基于精簡指令集(RISC)原則的開源指令集架構(gòu)(ISA)。它是一個處理器的設(shè)計規(guī)范和標(biāo)準(zhǔn),定義了處理器如何執(zhí)行指令和與內(nèi)存交互。RISC-V處理器是一種實際運行的硬件,它按照RISC-V指令集架構(gòu)執(zhí)行程序,完成各種計算和控制任務(wù)。RISC-V處理器的特點是其指令集經(jīng)過精簡設(shè)計,使得處理器的功耗、體積大大縮小,適用于現(xiàn)代計算設(shè)備,如倉庫規(guī)模云計算機(jī)、高端移動電話和微小嵌入式系統(tǒng)等。

其次,F(xiàn)PGA和RISC-V處理器的應(yīng)用領(lǐng)域也有所不同。FPGA廣泛應(yīng)用于通信、醫(yī)療、工業(yè)控制、航空航天等領(lǐng)域,特別是在需要靈活性和可重新配置性的場合。而RISC-V處理器則更多地應(yīng)用于微控制器、嵌入式系統(tǒng)、物聯(lián)網(wǎng)等領(lǐng)域,其開源特性和模塊化設(shè)計使得它成為這些領(lǐng)域的理想選擇。

總結(jié)來說,F(xiàn)PGA和RISC-V處理器在性質(zhì)、功能和應(yīng)用領(lǐng)域等方面存在明顯的區(qū)別。FPGA是一種可編程的硬件設(shè)備,通過編程實現(xiàn)不同的邏輯功能;而RISC-V處理器是一種基于特定指令集架構(gòu)的硬件,執(zhí)行程序完成計算和控制任務(wù)。兩者在各自的領(lǐng)域發(fā)揮著重要的作用。

-

處理器

+關(guān)注

關(guān)注

68文章

19824瀏覽量

233709 -

FPGA

+關(guān)注

關(guān)注

1643文章

21982瀏覽量

614554

發(fā)布評論請先 登錄

晶心科技推出突破性的RISC-V 27系列處理器及向量擴(kuò)展指令處理器

學(xué)習(xí)RISC-V入門 基于RISC-V架構(gòu)的開源處理器及SoC研究

RISC-V的特色,大飽眼福!!!

RISC-V開源處理器核介紹

RISC-V系列處理器的相關(guān)資料推薦

從零開始寫RISC-V處理器之一 二 前言 緒論

香山處理器 RISC-V的典范

高云半導(dǎo)體攜帶RISC-V FPGA設(shè)計易用性方案出席RISC-V論壇

RISC-V是通用RISC處理器還是可定制的處理器?

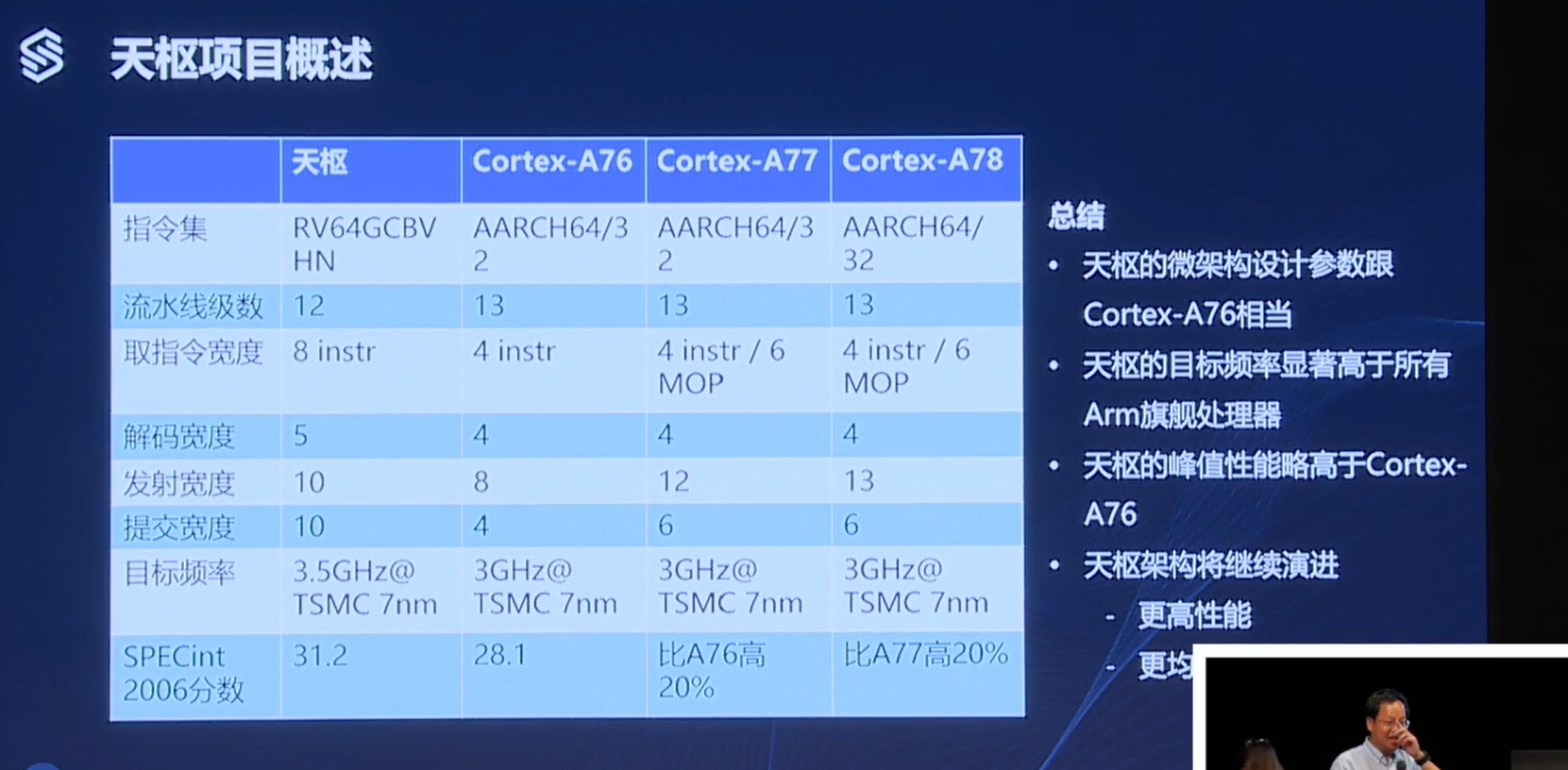

首屆risc-v峰會的最新消息:天樞的高性能RISC-V處理器架構(gòu)詳解

從零開始寫RISC-V處理器

基于形式的高效 RISC-V 處理器驗證方法

fpga和risc-v處理器的區(qū)別

fpga和risc-v處理器的區(qū)別

評論