5.1/O 寄存器

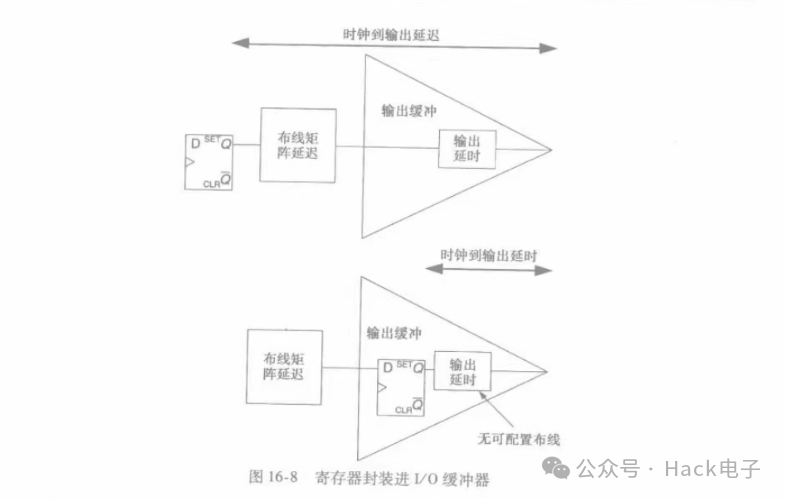

許多FPGA有構造在輸入和輸出緩沖器中的觸發器來優化芯片的時序入和出。同時這些專門的IO緩沖器是使能或禁止把這些寄存器封裝進V0的一個優化。圖16-8說明封裝寄存器進VO緩沖器的概念。

把寄存器放置進I/O有許多優點:

在 FPGA的 I/O上的延時是最小的。

內部更多的邏輯是可用的。

優良的時鐘到輸出的時序

優良的建立時間的時序

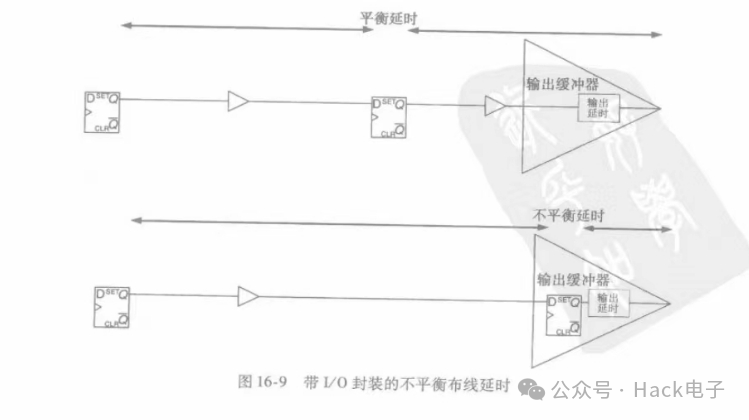

此優化的缺點是放置在VO緩沖器中的寄存器不可能成為內部邏輯的最佳放置地,如圖16-9所示。

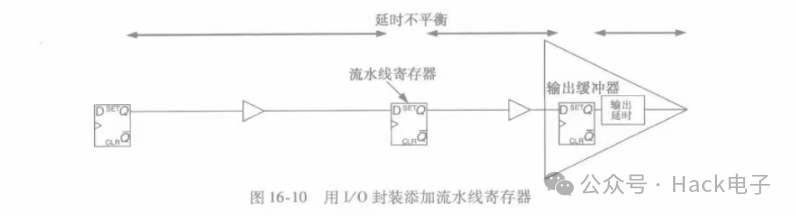

對于在I/O和內部邏輯二者有緊的時序要求的高速設計,如果設計協議允許在I/O添加另層流水線寄存器可能是有利的,如圖16-10所示。

如果有大量的IO寄存器,額外的流水線層次可以根據寄存器利用率和潛在的擁擠增加有效的開銷。

當封裝寄存器進 VO 時為高速設計可能要求額外的流水線寄存器。

因此,如果沒有緊的VO時序要求和有相對大量的O寄存器,不推薦這個優化。

6.封裝因子

封裝因子作為百分比定義,將人工地限制FPGA中邏輯資源的利用率。例如,一個100%的封裝因子告訴布局工具所有的邏輯資源對實現是有效的,但是50%的封裝因子告訴工具只有總的邏輯資源一半是有效的。

這個優化的用途是有限的,但是可以被高級的用戶使用。例如,為了對沒有包含在當前流程中的未來邏輯保持座席,封裝因子可以按照估計的尺寸減少。這個實現的方便類似于在集成新的核時設計者可以作什么預計。因此,資源利用率問題可能更早地識別。

此外,封裝因子可以利用來決定設計中凈空的數量,或者“真實的”利用率。如果有未用的邏輯元件,布局和布線工具復制邏輯元件將更充裕,有最優布局圖以外擴展的方式。一個邏輯元件當它的任何部分利用來實現邏輯時均定義它被利用,并不需要它完全被利用。因此,百分比利用率通常是比真實的利用率高。

設置封裝因子可以幫助決定真實的利用率。

換言之,報告60%利用率的FPCA可能有比40%更多的邏輯資源可用(當然不管利用率達到100%時布線能力問題)。為了估計設計中真實的利用率和凈空率,封裝因子可以減少直到設計不可以正確地布線。

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21985瀏覽量

615099 -

寄存器

+關注

關注

31文章

5425瀏覽量

123652 -

觸發器

+關注

關注

14文章

2033瀏覽量

61952 -

時鐘輸出

+關注

關注

0文章

4瀏覽量

5740

原文標題:FPGA布局布線優化(三)

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

緩沖器,緩沖器是什么?

液壓緩沖器的優點

74SSTUB32868A 28位至56位寄存器緩沖器數據表

74SSTUB32868 28位至56位寄存器緩沖器數據表

SN74SSTV16859具有SSTL 2輸入和輸出的13位至26位寄存器緩沖器數據表

SN74SSTVF16859具有SSTL 2輸入和輸出的13位至26位寄存器緩沖器數據表

CAB4A-DDR4寄存器32位1:2命令/地址/控制緩沖器和1:4差分時鐘緩沖器數據表

封裝寄存器進VO緩沖器的概念及其優點簡析

封裝寄存器進VO緩沖器的概念及其優點簡析

評論