近日,據海外科技媒體 Windows Latest 的報道,惠普品牌計算機在升級至最新的 Windows 10 及 Windows 11 操作系統后,可能會遇到 Caps Lock On 與 Num Lock On 的通知顯示問題。

惠普用戶表示,一旦敲擊大寫字母或按鍵數字,屏幕便會出現相應的彈出式窗口。Windows Latest 發現此現象自 4 月 25 日更新的安裝開始顯現,且更新過程通常由內置的 HP Support Assistant 智能完成。

若用戶不愿手動關閉如上提示,可嘗試以下操作:首先,在任務管理器中停用 HP System Event Utility 進程;其次,在啟動項目中屏蔽所有與惠普相關的選項。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

WINDOWS

+關注

關注

4文章

3611瀏覽量

91320 -

惠普

+關注

關注

0文章

600瀏覽量

38301 -

任務管理器

+關注

關注

0文章

15瀏覽量

7853

發布評論請先 登錄

相關推薦

熱點推薦

Molex莫仕Micro-Lock Plus連接器系列介紹

Micro-Lock Plus連接器系列專為緊湊型應用打造,不僅具備高溫環境下所需的電氣和機械可靠性,還提供出色的空間優化與堅固耐用的連接性能。該系列產品能滿足各行業的嚴格需求,包括在嚴苛環境下運行設備的要求。

如何得到tvp5158每個輸入端口的Lost lock status?

嘗試過讀取0x0,可以讀到第一個cvbs lock 狀態。其它三個輸入端口如何讀取其Lost lock status?

發表于 01-22 06:43

TVP5151是否可以將lost lock detect作為與攝像頭連接狀態的檢測?

需求:在視頻輸入處,想要檢測攝像頭連接情況。如果連接不正常,給出告警或其他處理。

方案:從tvp5151的手冊來看,有如下寄存器,僅找到這部分內容,其他內容尚未找到。

疑問:是否可以將lost lock detect作為與攝像頭連接狀態的檢測?

謝謝。:)

發表于 01-10 08:37

ADC12D1800 PLL的LOCK信號不能鎖定,出現低電平,是什么原因?

最近在調試AD模塊,使用ADC12D1800,AD輸出的時鐘DCLKI、DCLKQ首先經過FPGA內部的PLL用于寄存數據,但是PLL的LOCK信號不能鎖定,出現低電平,請問最可能是什么原因?

發表于 01-01 07:58

DS90UB954A RIN1有時無法Lock 913輸入的FPD-link信號,為什么?

DS90UB954A RIN1 有時候無法Lock 913輸入的FPD-link信號。但是從物理上可以在954輸入端可以量到信號。MIPI端無輸出信號。

這種狀態下0x4D 低兩位一直為0x40。

發表于 12-17 08:36

DS90UB954出錯后就不能繼續收圖圖,怎么解決?

在使用過程中出現DS90UB954出錯后就不能繼續收圖現象. 出錯時候0x4D提示:[0x4D] : 0x30 或者是0x33

手冊提示是:

Bi-directional Contr

發表于 12-16 08:27

DS90UB914測量lock腳,一直為低,有試過將bist打高,lock一直沒變化,問題出在哪里?

現通過914配置913:

1)直接讀取914的0x06,可自動獲取913的地址0xB0

2)配置SER_Alias地址0x07,寫入別名0xB2

3)讀取0xB2的0x00地址,無法獲取

4)測量lock腳,一直為低,有試過將bist打高,lock一直沒變化

請問下問題

發表于 12-12 07:39

請問一下LMH1983的0x1C Loss of Lock Threshold 和0x2D LockStepSize的具體功能是什么?

想請問一下LMH1983的0x1C Loss of Lock Threshold 和0x2D LockStepSize的具體功能。 LockStepSize似乎是設置一個觀察時間,Loss

發表于 11-12 07:23

使用LMK04821芯片的單PLL模式,輸出的時鐘頻率基本上是對的,但PLL2不能lock,為什么?

我們使用LMK04821芯片的單PLL模式,從OSCin輸入125Mhz的差分時鐘,配置參數如下。

測試中發現,輸出的時鐘頻率基本上是對的,但PLL2不能lock。

請問可能是什么原因?需要如何調查和解決這個問題?謝謝!

發表于 11-11 06:13

通過CDCE62005 EVM工具生成5路lvds格式輸出5路128MHz的LVDS格式時鐘時,LOCK引腳的信號如下,為什么?

684.4536m

注:在使用CDCE62005 EVM工具配置5路LVDS 100MHz和200MHz輸出時,LOCK信號能正常拉高,在測試5路128MHz和150MHz時出現上述問題。

發表于 11-08 12:26

CDCE62005按默認配置,無輸出無PLL_LOCK是怎么回事?

采用AUX_IN輸入25MHz時鐘,外部配置引腳如圖均設為高電平(經測量確為高電平),芯片寄存器為默認,希望能實現芯片手冊示例中的輸出(156.25MHz和125MHz等輸出)。

經測量芯片供電正常,輸入時鐘正確給入,但都無輸出,且PLL_LOCK始終為低電平。求問可能是出了什么問題?

發表于 11-08 07:07

TAS5805M EVM初始化之后, SPDIF Lock的燈就不亮了,為什么?

在EVM初始化之后, SPDIF Lock的燈就不亮了,

是否有甚么步驟做錯了或是需要注意的地方? 謝謝!

發表于 10-15 06:22

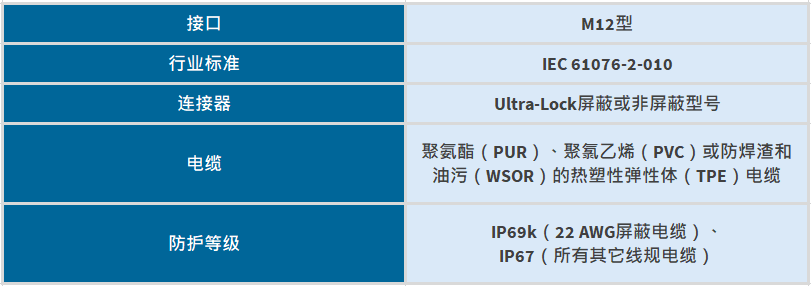

Molex莫仕Brad M12 Ultra-Lock 2.0連接器介紹

Brad M12 Ultra-Lock 2.0包含插頭的纜線組件和插座,符合IEC 61076-2-010標準。這款產品適用于易于組裝的界面,有屏蔽式和非屏蔽式兩種型號供用戶選擇。它不僅能夠提高

惠普電腦更新后出現“Caps Lock On”及“Num Lock On”提示

惠普電腦更新后出現“Caps Lock On”及“Num Lock On”提示

評論