算力是數字經濟時代的核心生產力,并且近年來需求劇增。而我國當前的算力供給上仍面臨巨大的挑戰,一方面,國外的高端算力芯片被美國禁售,另一方面,國內的芯片產業仍處于發展階段[1]。如何獲取算力提升,成為當前時代芯片研究的重要命題。

一.算力突破

研究如何獲取算力提升,要從算力的來源上考慮。芯片算力可大致總結為以下計算公式:

因此,獲取算力提升的主要切入點是晶體管密度、芯片面積、單位晶體管的算力,這三個方面分別主要涉及制作工藝、光刻口徑、計算架構。

(1)晶體管密度:

晶體管密度的主要影響因素是制造工藝、基板材料,同樣的面積內,封裝的可用晶體管越多,就能提供越強的算力。

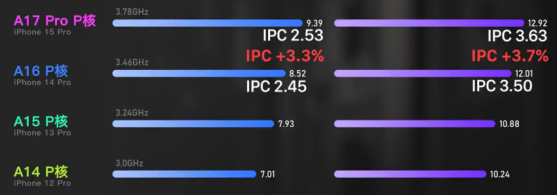

制造工藝方面,受限于美國的無理封鎖,當前國內量產芯片的最先進制造工藝為14nm,國際上量產芯片最先進的制造工藝為3nm。清華大學尹首一教授認為,國內芯片制造工藝將長期處于在14nm,國內芯片產業與研究不能指望通過制造工藝獲得性能提升。在國際領域,雖然芯片制造商仍能享受到制程工藝帶來的升級,但從蘋果A17Pro芯片的性能表現、高通仍然采用基于4nm的升級工藝制造今年旗艦芯片的市場行為來看,產業界最先進的工藝制程已經不及預期。

基板材料方面,隨著制造工藝步入埃米級別,芯片制造工藝受到硅原子性質的影響越來越大,產業界和學界也在探索新的材料用于制造芯片,通過“彎道超車”的方式提升晶體管密度,比如英特爾等廠商正在研發的玻璃基芯片[3]、北京大學彭練矛教授團隊正在研發的碳基芯片[4]。

(2)芯片面積

芯片面積和晶體管密度考慮的是類似的問題,在一顆芯片內提供更多的可用晶體管,就意味著能提供更多的算力。但是在當前,GPU的單芯片面積基本已經達到上限,想通過面積獲得進一步的算力提升,可以從拓展角度考慮,有兩個探索的方向:平面拓展和垂直拓展。

平面拓展就是在光刻時使用光照拼接技術,實現兩個曝光區域的物理連接,來把芯片做大,通過計算架構的優化設計,保證晶圓中晶體管的可用性,Cerebras公司和Tesla公司已經實現了晶圓級芯片。垂直拓展就是把芯片或其中的部分器件三維堆疊起來,如AMD的3D緩存技術。

(3)單位晶體管提供的算力:

單位晶體管提供的算力和計算架構息息相關,計算架構的優化改進或使用新的計算架構,能夠對芯片算力產生更根本的影響。計算架構上面臨的主要問題有:基本器件的設計架構不同導致的晶體管數量不同,需要探索更優的基本器件結構設計;馮諾依曼架構的“存儲墻”導致的訪存瓶頸,限制了算力的發揮,需要降低帶寬對算力的限制;功耗限制導致的darkselect問題,即為了保證芯片功耗,不能同時點亮芯片上的所有晶體管,需要優化設計來避免。

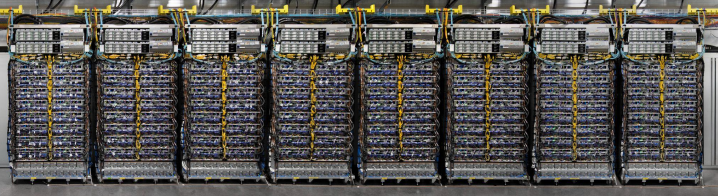

面對以上的部分問題,產業界和學界已經給出了相應的解決方案。在計算架構的優化方面,有數據流、可重構、存算一體三條路徑。首先,數據流芯片嘗試不使用指令而是直接通過數據驅動計算,避免外部存儲訪問,來解決晶體管利用率低的問題。Google的TPU芯片已經證明了,這種方式雖然在單芯片性能上遜于GPU,但能在系統級算力上實現超越[1]。具體來講,單核TPU v4的性能是低于A100 GPU的,只有它的88%,但1024顆TPU v4的集群性能,超過了A100 GPU的集群性能,最高達到了1.96倍。4096顆TPUv4芯片示意圖如下圖3所示。

圖 34096顆TPUv4芯片集成[6]

可重構芯片嘗試在芯片內布設可編程的計算資源,根據計算任務的數據流特點,動態構造出最適合的計算架構,國內團隊設計并在12nm工藝下制造的CGRA芯片,已經在標準測試集上實現了和7nm的GPU基本相當的性能。存算一體嘗試通過集成存儲和計算在一個芯片甚至一個容器內,來突破訪存限制,發揮芯片的最大算力。下面我們將重點介紹存算一體技術。

二.存算一體

存算一體是一種新型計算架構,直接利用存儲器本身進行數據處理,從根本上消除數據搬運,實現存儲與計算融合一體化,成為后摩爾時代集成電路領域的重點研究方向之一。

(1)存算一體技術優勢:

存算一體技術具有很大的優勢,存算融合的特點使其天然具備較大算力、低延遲、高帶寬等優勢。相比傳統架構,存算一體大算力芯片不僅僅是能效比有數量級的提升,更重要的是將大大緩解存儲墻問題,簡化AI服務器集群的互聯網絡及其管理和各類成本,包括高速互聯、DPU和能耗等。因此,存算一體技術是實現芯片算力突破的重要途徑,可助力實現28nm等效7nm功效。

(2)傳統工藝芯片算力提升實例:

目前已有一些企業和高校,通過存算一體技術,實現28nm制程芯片的能效算力提升。

憶鑄科技于2021年10月于上海成立,是一家基于ReRAM設計和落地數字存算一體芯片的企業。在公司的技術暢想中,他們嘗試將新型憶阻器、存算一體架構、Chiplet技術、3D封裝等技術結合,實現大算力、高能效比的芯片。據其官網信息,億鑄第一代算力芯片采用的工藝為28nm,其能效比可以實現目前主流算力板卡的10倍以上[7]。

2023年8月29日,華為的麒麟9000s芯片隨著Mate 60 Pro成功發布,該款芯片一經發出,就引發業界討論:“麒麟9000s的工藝制程究竟是多少?”在2023年中國集成電路設計業(ICCAD)年會上,清華大學魏少軍教授在演講中提出:“能夠用14nm,甚至28nm做成7nm的產品性能才是真正的高手”。據悉,華為并未公布麒麟9000s真正的工藝制程,知名科技解析機構TechInsights對麒麟9000s深入解析結果顯示,該芯片確實擁有7nm工藝制程的特性。

圖 4 華為麒麟9000s芯片

知存科技的WTM2101量產芯片采用40nm制程,將神經網絡部署在芯片中,已經實現了滿足端側算力需求的語音識別等功能。即將量產的WTM8芯片,采用28nm制程,作為新一代存內AI計算視覺芯片,能夠實現圖像的AI超分、插幀、HDR識別和檢測這樣復雜的功能[8],現有的一些研究也已經證明存算一體可以實現16bit、32bit的浮點計算,具備進入高算力芯片的能力。

圖 5知存科技WTM-8系列芯片示意圖

三.未來展望

隨著工藝的進步,先進工藝制程已從28nm發展至3nm,蘋果新發布的A17Pro已采用了tsmc 3nm工藝。據悉,tsmc也將投資近萬億新臺幣建造1nm晶圓廠。在未來,有沒有一種全新的方案解決算力不足、工藝制程發展空間受限的局面?存算一體便是答案之一。

綜上所述,存算一體技術因為其特殊優勢,可以大大提升芯片算力,從而使得成熟28nm制程芯片能夠實現等效于7nm制程芯片的性能。當然這其中還有很多難點需要突破,需要科研工作著的不斷努力,期待未來基于存算一體技術的芯片可以更好地突破芯片制程的限制。

[1] 尹首一教授報告:以“架構”創新,突破算力卡脖子問題.

[2] 極客灣 space.bilibili.com/25876945.

[3] 第八屆未來芯片論壇中英特爾中國研究院的報告.

[4] 北京大學新聞網:專訪北大碳基芯片團隊:我們換道走了20年,覺得能走下去 (news.pku.edu.cn).

[5] AMD官網 amd.com.

[6] Jouppi N, Kurian G, Li S, et al. Tpu v4: An optically reconfigurable supercomputer for machine learning with hardware support for embeddings[C]//Proceedings of the 50th Annual International Symposium on Computer Architecture. 2023: 1-14.

[7] 憶鑄科技官網 (yizhu-tech.com).

[8] 知存科技官網(witintech.com).

[9] 從7nm到5nm,半導體制程 - 吳建明wujianming - 知乎(zhuanlan.zhihu.com/).

審核編輯 黃宇

-

芯片

+關注

關注

456文章

51260瀏覽量

427746 -

AI

+關注

關注

87文章

31670瀏覽量

270472 -

芯片制程

+關注

關注

0文章

51瀏覽量

4742 -

算力

+關注

關注

1文章

1023瀏覽量

14970 -

存內計算

+關注

關注

0文章

30瀏覽量

1406

發布評論請先 登錄

相關推薦

Altera 28nm FPGA助力NEC提升LTE基站性能

什么是Altera最新28nm FPGA技術?

如何利用28nm高端FPGA實現功耗和性能的平衡?

Fusion Design Platform?已實現重大7nm工藝里程碑

請大神解釋一下28nm下是沒有MIM電容了嗎?

求一份tsmc 7nm standard cell library

從7nm到5nm,半導體制程 精選資料分享

28nm Stratix V FPGA突破帶寬瓶頸

降低賽靈思28nm 7系列FPGA的功耗

22nm和28nm芯片性能差異

所謂的7nm芯片上沒有一個圖形是7nm的

存內計算——助力實現28nm等效7nm功效

存內計算——助力實現28nm等效7nm功效

評論