開關(guān)電源芯片被廣泛應(yīng)用于車載電子系統(tǒng)中,完成高效電能轉(zhuǎn)換。隨著智能駕駛技術(shù)的迅速發(fā)展,對(duì)開關(guān)電源芯片的電磁干擾(EMI)噪聲的要求也日益嚴(yán)苛。面對(duì)當(dāng)今愈發(fā)復(fù)雜的車載應(yīng)用環(huán)境,傳統(tǒng)依靠在實(shí)驗(yàn)室根據(jù)標(biāo)準(zhǔn)條件測(cè)試EMI噪聲的管理辦法已經(jīng)難以保證架駛安全性。為此,包括電氣與電子工程師協(xié)會(huì)(IEEE)在內(nèi)的國(guó)際權(quán)威機(jī)構(gòu)開始建立基于風(fēng)險(xiǎn)檢測(cè)的EMI噪聲管理標(biāo)準(zhǔn),以實(shí)現(xiàn)電子系統(tǒng)的全生命周期風(fēng)險(xiǎn)評(píng)估,這為實(shí)時(shí)EMI控制提出了極高的挑戰(zhàn)。

針對(duì)上述發(fā)展趨勢(shì),復(fù)旦大學(xué)芯片與系統(tǒng)前沿技術(shù)研究院、集成芯片與系統(tǒng)全國(guó)重點(diǎn)實(shí)驗(yàn)室劉明院士團(tuán)隊(duì)提出了在線閉環(huán)EMI管理新策略,消除了傳統(tǒng)EMI控制過程中需要人為干預(yù)的需求,實(shí)現(xiàn)噪聲原位動(dòng)態(tài)調(diào)控。在具體設(shè)計(jì)上,團(tuán)隊(duì)基于壓縮感知原理,在芯片上設(shè)計(jì)集成了高帶寬原位EMI傳感器,根據(jù)在線分析得到的EMI頻譜,進(jìn)一步完成了可自適應(yīng)調(diào)節(jié)開關(guān)頻率抖動(dòng)范圍的全局過額頻譜調(diào)節(jié)。

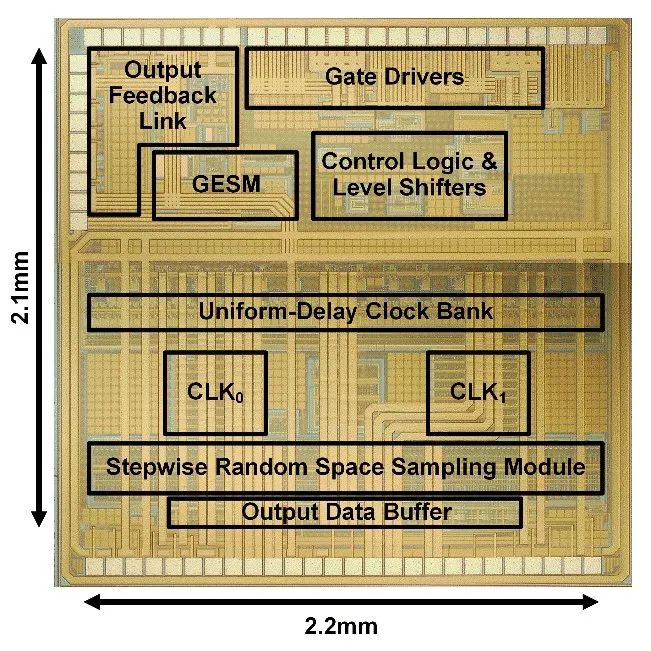

上述技術(shù)集成在一款控制氮化鎵(GaN)功率晶體管的高速DC-DC功率轉(zhuǎn)換芯片(BIT)中(圖1),采用180nm BCD工藝流片,測(cè)試結(jié)果表明,原位EMI傳感器帶寬達(dá)500MHz,檢測(cè)誤差在3dB 以內(nèi),EMI頻譜調(diào)節(jié)分辨率達(dá)9kHz,滿足通用EMI標(biāo)準(zhǔn)的測(cè)試要求。

圖1. 高速低EMI噪聲功率芯片(BIT)照片

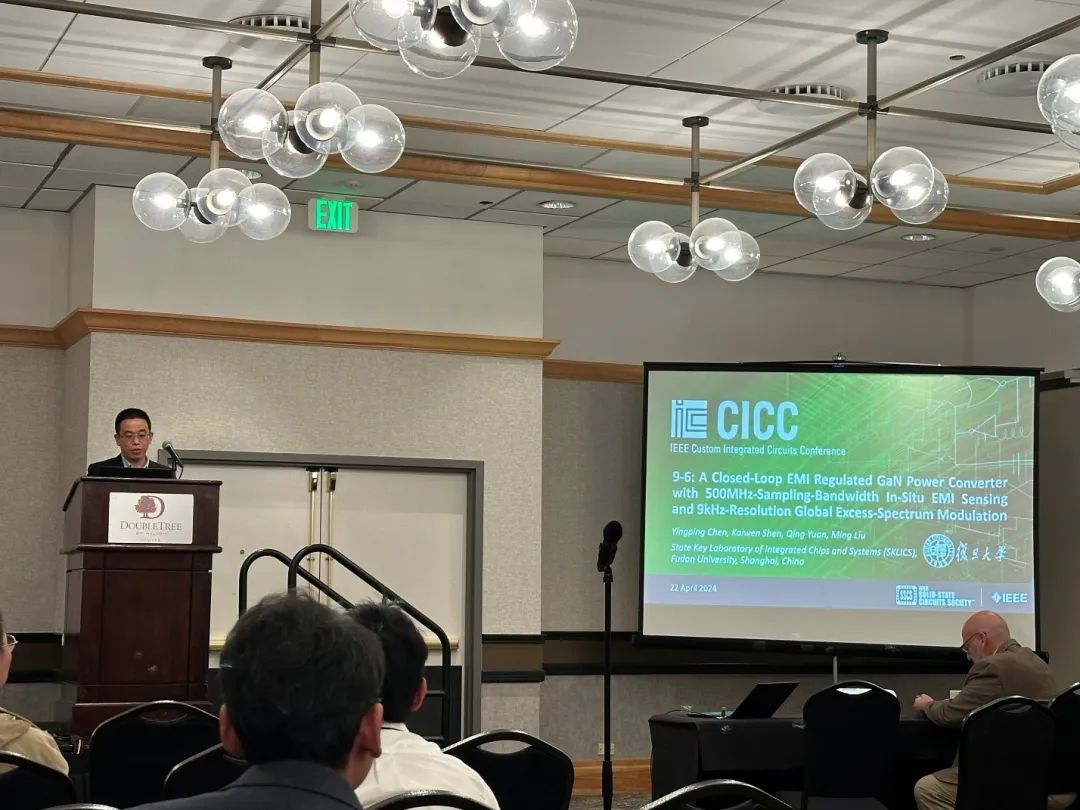

相關(guān)研究成果以A Closed-Loop EMI Regulated GaN Power Converter with 500MHz-Sampling-Bandwidth In-Situ EMI Sensing and 9kHz-Resolution Global Excess-Spectrum Modulation為標(biāo)題發(fā)表于2024年的IEEE定制集成電路會(huì)議(Custom Integrated Circuits Conference, CICC)上,論文第一作者、復(fù)旦大學(xué)芯片院青年研究員陳映平在大會(huì)上作口頭報(bào)告(圖2),并作展板介紹(Poster)。鑒于設(shè)計(jì)的新穎性與先進(jìn)性,本項(xiàng)工作榮獲大會(huì)最佳研究論文獎(jiǎng)(Best Regular Paper Award),最佳論文獲獎(jiǎng)比例為5/144。

圖2. 我院高速低EMI功率芯片在CICC 2024上作口頭報(bào)告

IEEE定制集成電路會(huì)議(CICC)是集成電路設(shè)計(jì)領(lǐng)域的旗艦會(huì)議之一,由IEEE固態(tài)電路協(xié)會(huì)(Solid-State Circuits Society)主辦,IEEE 電子器件協(xié)會(huì)(Electron Devices Society)協(xié)辦,每年吸引全球范圍內(nèi)大量學(xué)術(shù)界和工業(yè)界研發(fā)人員的關(guān)注和參與。本次CICC于2024年4月21日-24日在美國(guó)科羅拉多州首府丹佛舉行。

來源:復(fù)旦大學(xué)芯片與系統(tǒng)前沿技術(shù)研究院

審核編輯:劉清

-

集成電路

+關(guān)注

關(guān)注

5422文章

12029瀏覽量

368160 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2389瀏覽量

106491 -

氮化鎵

+關(guān)注

關(guān)注

61文章

1788瀏覽量

117910 -

GaN

+關(guān)注

關(guān)注

19文章

2199瀏覽量

76652 -

開關(guān)電源芯片

+關(guān)注

關(guān)注

5文章

220瀏覽量

24717

原文標(biāo)題:復(fù)旦大學(xué)芯片院在高速低EMI功率集成電路設(shè)計(jì)領(lǐng)域取得重要進(jìn)展

文章出處:【微信號(hào):第三代半導(dǎo)體產(chǎn)業(yè),微信公眾號(hào):第三代半導(dǎo)體產(chǎn)業(yè)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

國(guó)內(nèi)首條碳基集成電路生產(chǎn)線正式投產(chǎn)運(yùn)營(yíng)

電機(jī)驅(qū)動(dòng)與控制專用集成電路及應(yīng)用

維智科技將參加復(fù)旦大學(xué)第四屆數(shù)字經(jīng)濟(jì)生態(tài)論壇

新思科技攜手深圳大學(xué)推動(dòng)集成電路設(shè)計(jì)領(lǐng)域發(fā)展

微電子所在超寬帶低噪聲集成電路設(shè)計(jì)領(lǐng)域取得新進(jìn)展

納芯微與復(fù)旦大學(xué)微電子學(xué)院合作研發(fā)成果亮相JSSC

天合光能與復(fù)旦大學(xué)共建先進(jìn)光伏技術(shù)校企聯(lián)合實(shí)驗(yàn)室

德力西電氣榮獲復(fù)旦大學(xué)雙碳目標(biāo)與氣候變化貢獻(xiàn)獎(jiǎng)

ASIC集成電路應(yīng)用領(lǐng)域 ASIC集成電路的優(yōu)缺點(diǎn)分析

ASIC集成電路設(shè)計(jì)流程

高性能集成電路應(yīng)用 集成電路封裝技術(shù)分析

奇異摩爾與復(fù)旦大學(xué)三維集成芯片研究成果入選ISSCC 2025

生產(chǎn)單片機(jī)的公司有哪些?

成為集成電路設(shè)計(jì)高手的必經(jīng)之路:科目攻略大公開

復(fù)旦大學(xué)芯片院在高速低EMI功率集成電路設(shè)計(jì)領(lǐng)域取得重要進(jìn)展

復(fù)旦大學(xué)芯片院在高速低EMI功率集成電路設(shè)計(jì)領(lǐng)域取得重要進(jìn)展

評(píng)論