精工愛普生公司(TSE:6724,“愛普生”)為晶體振蕩器開發(fā)了一種新的差分輸出*方案。新方案,即寬振幅低壓差分信號(WA-LVDS),能夠靈活選擇最適合LSI所需振幅水平的輸出。愛普生計劃在2025財年(從2025年4月開始)推出具有WA-LVDS輸出的晶體振蕩器。

隨著數(shù)字化的最新進展,數(shù)據(jù)流量正在迅速增長,第五代移動通信系統(tǒng)(5G)、物聯(lián)網(wǎng)(IoT)和下一代通信系統(tǒng)將需要更快的傳輸速度和更高的容量來支持這種流量。在這種系統(tǒng)中,數(shù)據(jù)傳輸需要LVDS、LV-PECL和HCSL等通用差分輸出。每種方案都有自己的特點,工程師會為他們的特定系統(tǒng)選擇最佳方案。然而,近年來,通信設(shè)備所需的更高性能意味著電路現(xiàn)在被設(shè)計為接收通信設(shè)備中使用的LSI的最佳差分輸出。因此,越來越多的情況下無法使用通用差分輸出。因此,預(yù)計未來對適用于LSI的差分輸出的需求將更加強勁。

現(xiàn)有的LVDS具有通用差分輸出,其電流消耗低于LV-PECL和HCSL。然而,另一方面,它的振幅也較低,因此抗噪性較差。為了解決這個問題,愛普生開發(fā)了WA-LVDS,這是一種具有可選擇幅度電平的差分輸出,可以靈活使用。WA-LVDS通過容易地獲得高振幅來提高抗噪性。它還提供了比LV-PECL和HCSL更低的電流消耗。

作為晶體器件的領(lǐng)導(dǎo)者,愛普生將繼續(xù)提供滿足各種電子設(shè)備和社會基礎(chǔ)設(shè)施需求的晶體器件產(chǎn)品。

*:差分輸出是一種信號傳輸方法,其中數(shù)據(jù)以相反極性的兩條獨立線路之間的電壓差傳輸。差分輸出的優(yōu)點包括高頻數(shù)據(jù)傳輸和高抗噪性。

附錄

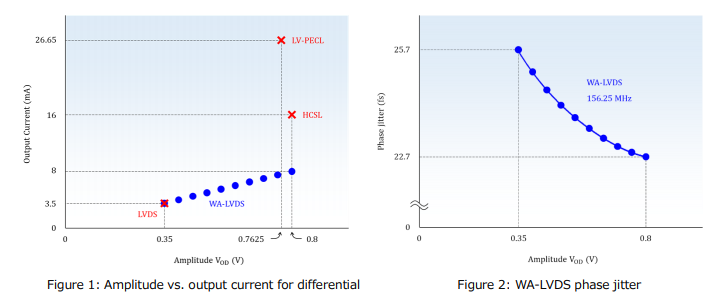

差分輸出的幅度、輸出電流和相位抖動*如圖1和圖2所示。LVDS、LVPECL和HCSL以紅色顯示。WA-LVDS以藍色顯示。

圖1

對應(yīng)于振幅的H和L電平之間的差對于LVDS定義為0.35 V。雖然輸出電流小,幅度低,導(dǎo)致LVDS的抗噪性比LV-PECL和HCSL。另一方面,LV-PECL和HCSL的振幅較大,但消耗較大電流量。WA-LVDS振幅可小幅度選擇,從與LVDS相同的電平到與LV-PECL和HCSL相對應(yīng)的水平。此外,WA-LVDS輸出電流保持較低,有助于低電流消耗。

圖2:

隨著WA-LVDS幅度的增加,相位抖動減小,從而產(chǎn)生低噪聲的差分輸出。

*:相位抖動:時鐘周期的波動稱為抖動。相位抖動是衡量無抖動理想時鐘邊緣偏差的指標,可以根據(jù)相位噪聲特性進行計算

-

lvds

+關(guān)注

關(guān)注

2文章

1127瀏覽量

67495 -

愛普生

+關(guān)注

關(guān)注

0文章

485瀏覽量

22711 -

信號傳輸

+關(guān)注

關(guān)注

4文章

456瀏覽量

20702

發(fā)布評論請先 登錄

CMD245C4低噪聲放大器現(xiàn)貨庫存

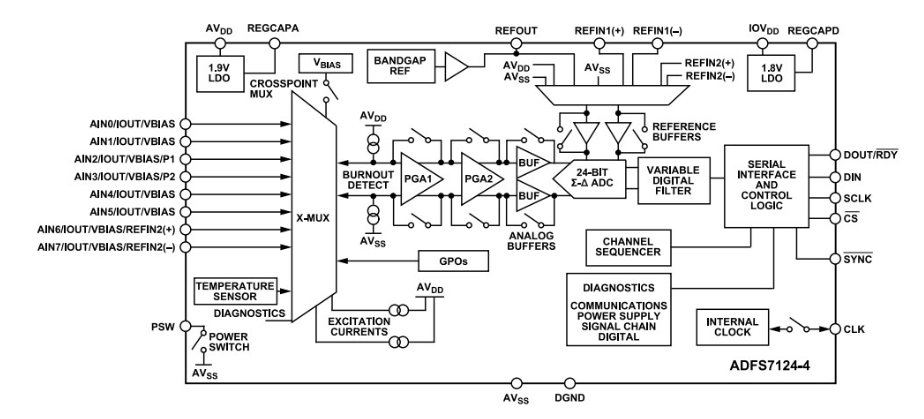

Analog Devices Inc. ADFS7124低功耗低噪聲模擬前端特性/應(yīng)用

CMD229P4低噪聲放大器Custom MMIC原裝庫存

-45V/200mA低噪聲線性穩(wěn)壓電源替代ADP7182/TPS7A30/LT1964/TPS7A34/MAX1735

LVDS輸出差分晶振SG2520VGN,X1G0059010007,愛普生6G測試和測量晶振

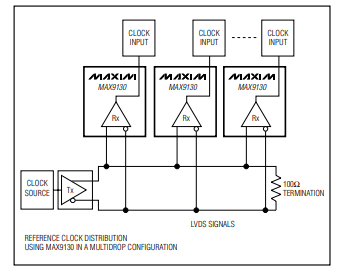

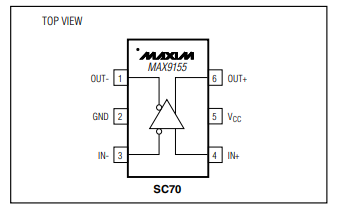

MAX9130單路、500Mbps、LVDS線接收器,SC70封裝技術(shù)手冊

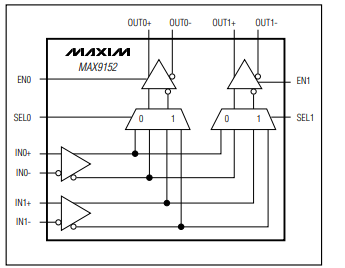

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉點開關(guān)技術(shù)手冊

MAX9155低抖動、低噪聲、LVDS轉(zhuǎn)發(fā)器,SC70封裝技術(shù)手冊

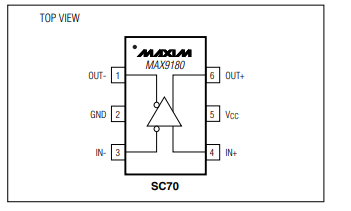

MAX9180 400Mbps、低抖動、低噪聲LVDS轉(zhuǎn)發(fā)器,SC70封裝技術(shù)手冊

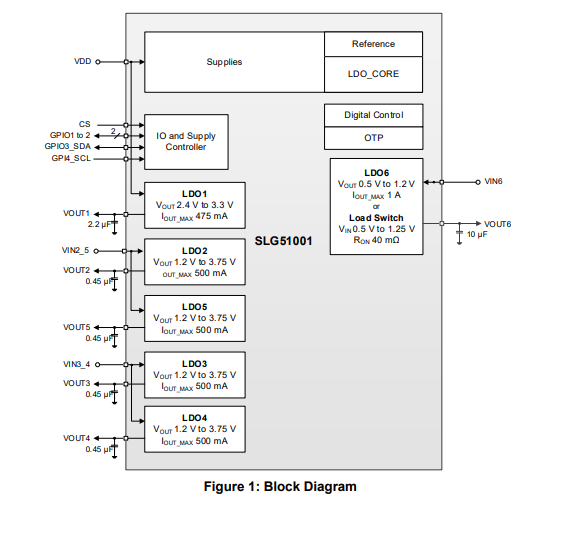

SLG51001高 PSRR、低噪聲多輸出LDO IC數(shù)據(jù)手冊

愛普生VG3225EFN壓控晶振5G基站低噪聲的解決方案

如何降低ADI LTM4702超低噪聲μModule穩(wěn)壓器的輸出開關(guān)噪聲

納祥科技NX6911:低噪聲、高輸出驅(qū)動能力、高壓擺率的寬電壓雙運放

求助,求推薦超低噪聲跨阻放大器

DAC8881 16位單通道低噪聲電壓輸出數(shù)模轉(zhuǎn)換器數(shù)據(jù)表

愛普生宣布開發(fā)獨特的寬振幅LVDS輸出 -與LS匹配的低噪聲輸出可靈活選擇-

愛普生宣布開發(fā)獨特的寬振幅LVDS輸出 -與LS匹配的低噪聲輸出可靈活選擇-

評論