DDR作為一種內(nèi)存技術(shù)正朝著更高性能、更低功耗的方向發(fā)展。應(yīng)用前景廣闊,將對(duì)半導(dǎo)體、計(jì)算機(jī)、汽車(chē)、新能源及各行業(yè)發(fā)展產(chǎn)生影響巨大。

在相同技術(shù)下,除了提高存儲(chǔ)密度、水平方向增加芯片數(shù)量以外,一種多層存儲(chǔ)(3D堆疊)技術(shù)被大量?jī)?yōu)化采用。

堆疊封裝可以在更小的空間內(nèi)提供更多的功能。堆疊封裝可以開(kāi)發(fā)具有不同功能的多芯片封裝,或者將多個(gè)存儲(chǔ)芯片放在一個(gè)容量增加的封裝中。

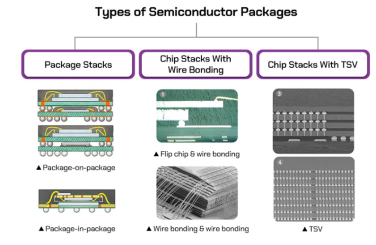

堆疊封裝根據(jù)不同的開(kāi)發(fā)技術(shù)分為三種類(lèi)型:

PiP(Package In Package)封裝

引線鍵合(Wire Bonding)封裝

硅穿孔(TSV)封裝;

堆疊封裝工藝優(yōu)點(diǎn)

封裝體的尺寸小,質(zhì)量輕;

頂層封裝模塊和底層封裝模塊的電子元件可以在組裝前進(jìn)行測(cè)試并替換,使得瑕疵率大大降低、良品比率升高,成本也大度下降;

在采取垂直互連的方式對(duì)上層和下層進(jìn)行連接,大大的減小了引線長(zhǎng)度,減少了寄生電容、寄生電感,電源損耗減小,信號(hào)的傳輸速度更快;

模塊中的存儲(chǔ)芯片和邏輯芯片可以由不同的商家提供,使產(chǎn)品的生產(chǎn)時(shí)問(wèn)縮短,效率提高。

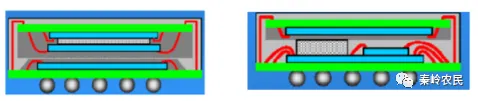

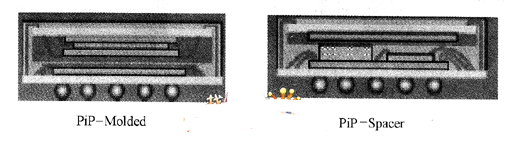

PiP(Package In Package)封裝

一般稱(chēng)堆疊封裝又稱(chēng)封裝內(nèi)的封裝,還稱(chēng)器件內(nèi)置器件,是在同一個(gè)封裝腔體內(nèi)堆疊多個(gè)芯片形成3D 封裝的一種技術(shù)方案。封裝內(nèi)芯片通過(guò)金線鍵合堆疊到基板上,同樣的堆疊,通過(guò)金線再將兩個(gè)堆疊之間的基板鍵合,然后整個(gè)封裝成一個(gè)元件便是PiP(器件內(nèi)置器件)。

PiP技術(shù)整合了PCB基板組裝及半導(dǎo)體封裝制作流程,可以將小型存儲(chǔ)卡所需要的零部件(控制器、閃存集成電路、基礎(chǔ)材質(zhì)、無(wú)源計(jì)算組件)直接封裝,制成功能完整的Flash存儲(chǔ)卡產(chǎn)品。PiP一體化封裝技術(shù)具有下列技術(shù)優(yōu)勢(shì):超大容量、高讀寫(xiě)速度、堅(jiān)固耐用、強(qiáng)防水、防靜電、耐高溫等,因此常運(yùn)用于SD卡、XD卡、MM卡等系列數(shù)碼存儲(chǔ)卡上。

技術(shù)優(yōu)勢(shì)

外形高度較低;

可以采用標(biāo)準(zhǔn)的SMT電路板裝配工藝;

單個(gè)器件的裝配成本較低。

PiP封裝結(jié)構(gòu)

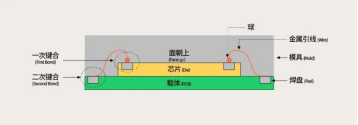

引線鍵合(Wire Bonding)封裝

引線鍵合是一種將金屬引線連接到焊盤(pán)上的技術(shù),用于連接內(nèi)部和外部芯片的方法。在結(jié)構(gòu)上,金屬引線在芯片的焊盤(pán)(一次鍵合)和載體的焊盤(pán)(二次鍵合)之間起到橋梁的作用。在早期,引線框架(lead frame)被用作載體基板,但隨著技術(shù)的不斷進(jìn)步,如今越來(lái)越多地使用PCB作為基板。連接兩個(gè)獨(dú)立焊盤(pán)的引線鍵合涉及引線的材料、鍵合條件、鍵合位置(不僅連接芯片和基板,還可能連接兩個(gè)芯片或兩個(gè)基板)等方面的顯著差異。

引線鍵合的結(jié)構(gòu)(載體為印刷電路板(PCB)時(shí))

技術(shù)優(yōu)勢(shì)

靈活性高:線鍵合堆疊封裝允許在單個(gè)封裝內(nèi)集成不同功能和工藝的芯片,具有較高的設(shè)計(jì)靈活性。

適應(yīng)性強(qiáng):該技術(shù)能夠適應(yīng)不同尺寸和形狀的芯片堆疊需求,為定制化設(shè)計(jì)提供了可能。

成本可控:與垂直堆疊封裝相比,線鍵合堆疊封裝的制造成本相對(duì)較低,適合大規(guī)模生產(chǎn)和應(yīng)用。

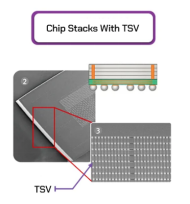

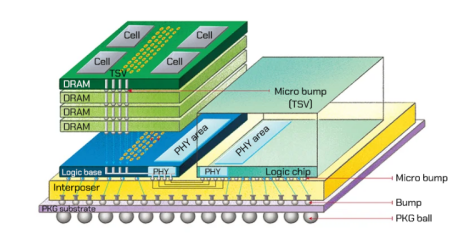

硅穿孔(TSV)封裝

TSV是一種芯片堆疊技術(shù),通過(guò)在硅上鉆孔來(lái)連接電路。TSV不是使用傳統(tǒng)的布線方法連接芯片到芯片或芯片到襯底,而是通過(guò)在芯片上鉆孔并填充導(dǎo)電材料(如金屬)來(lái)垂直連接芯片。雖然在與TSV堆疊時(shí)使用芯片級(jí)工藝,但在芯片正面和背面形成TSV和焊接凸起時(shí)使用晶圓級(jí)工藝。因此,TSV被歸類(lèi)為晶圓級(jí)封裝技術(shù)。

使用TSV封裝的主要優(yōu)點(diǎn)是高水平的性能和更小的封裝尺寸。如上圖所示,采用線鍵合的芯片堆疊封裝在每個(gè)堆疊芯片的側(cè)面都有導(dǎo)線連接。由于堆疊的芯片和連接的引腳越來(lái)越多,布線變得越來(lái)越復(fù)雜,需要更多的空間來(lái)連接它們。相比之下,采用TSV的芯片堆棧不需要復(fù)雜的布線,因此可以減小封裝尺寸。

TSV具有短的電信號(hào)傳輸路徑,這賦予TSV封裝強(qiáng)大的電氣性能。相反,如果使用線鍵合,信號(hào)傳輸路徑會(huì)變得更長(zhǎng),因?yàn)樾盘?hào)在到達(dá)芯片之前必須先到達(dá)基板,而且還不能在芯片中心進(jìn)行布線連接。相比之下,TSV封裝允許在芯片中心鉆孔,并且可以顯著增加引腳的數(shù)量。

目前量產(chǎn)的將TSV應(yīng)用于DRAM的存儲(chǔ)器產(chǎn)品包括HBM和3D堆疊存儲(chǔ)器(3DS)。前者用于圖形、網(wǎng)絡(luò)和高性能計(jì)算(HPC)應(yīng)用,而后者主要用作DRAM內(nèi)存模塊。

技術(shù)優(yōu)勢(shì)

高性能:TSV技術(shù)能夠大幅縮短信號(hào)路徑,降低信號(hào)傳輸?shù)难舆t和功耗,提升系統(tǒng)性能。

小型化:通過(guò)垂直堆疊和TSV互連,可以顯著減小封裝尺寸和重量,滿足電子產(chǎn)品小型化、輕量化的需求。

高集成度:TSV技術(shù)能夠?qū)崿F(xiàn)多層芯片堆疊和高度集成的封裝結(jié)構(gòu),提高芯片的集成密度和系統(tǒng)功能。

綜上所述,DDR芯片的堆疊封裝工藝技術(shù)作為一種先進(jìn)的封裝方式,在提升內(nèi)存性能、集成度及降低功耗方面具有重要意義。雖然堆疊封裝技術(shù)面臨技術(shù)成熟度、成本問(wèn)題和標(biāo)準(zhǔn)化等挑戰(zhàn),但隨著技術(shù)的不斷進(jìn)步和市場(chǎng)需求的不斷增長(zhǎng),其應(yīng)用前景依然廣闊。未來(lái),隨著半導(dǎo)體工藝的不斷進(jìn)步和封裝技術(shù)的不斷創(chuàng)新,堆疊封裝技術(shù)將在更多領(lǐng)域發(fā)揮重要作用,推動(dòng)電子產(chǎn)品的性能和功能不斷提升。

-

芯片

+關(guān)注

關(guān)注

459文章

52352瀏覽量

438568 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28769瀏覽量

235070 -

封裝

+關(guān)注

關(guān)注

128文章

8617瀏覽量

145110 -

內(nèi)存技術(shù)

+關(guān)注

關(guān)注

0文章

29瀏覽量

9922

原文標(biāo)題:堆疊封裝的三種主要類(lèi)型

文章出處:【微信號(hào):封裝與高速技術(shù)前沿,微信公眾號(hào):封裝與高速技術(shù)前沿】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

元器件PIP(堆疊封裝)和PoP(堆疊組裝)的比較

晶圓級(jí)多層堆疊技術(shù)及其封裝過(guò)程

元器件堆疊封裝結(jié)構(gòu)

芯片堆疊的主要形式

多層芯片堆疊封裝方案的優(yōu)化方法

堆疊封裝的安裝工藝流程與核心技術(shù)介紹

一文解析多芯片堆疊封裝技術(shù)(上)

華為芯片堆疊封裝專(zhuān)利公開(kāi)

芯片堆疊技術(shù)在系統(tǒng)級(jí)封裝SiP中的應(yīng)用存?

元器件PIP(堆疊封裝)和PoP(堆疊組裝)的比較

堆疊封裝技術(shù)的類(lèi)型解析

堆疊封裝技術(shù)的類(lèi)型解析

評(píng)論