2025年又是充滿無限可能的一年。開年之際,DeepSeek事件以燎原之勢席卷全球,再次印證了AI時代"一切皆有可能"的黃金法則。人工智能行業對計算的需求變革幾乎每天都在上演。從半導體的終端需求出發,芯片供給端正在經歷一場根本性的架構變革。在這場變革中,3D Chiplet異構集成技術逐步嶄露頭角,走向更廣闊的舞臺。

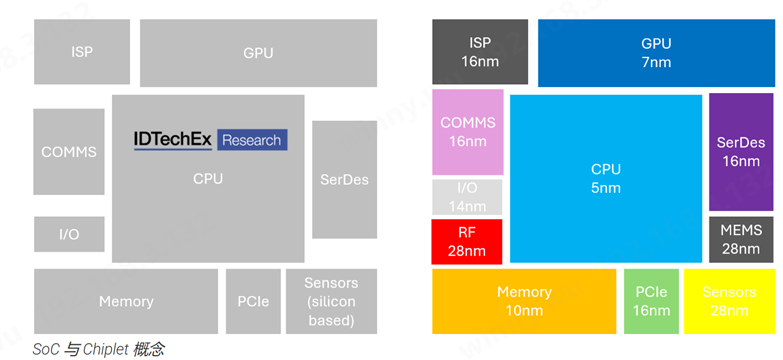

我們知道受制于最大光刻面積的限制,單芯片的面積無法無限制擴展。為此,需采用多次曝光拼接技術,這大幅增加了工藝難度,導致芯片良率顯著下降。面對晶體管數量持續增長與芯片橫向面積擴展受限的矛盾,Chiplet芯粒技術應運而生。

(來源:IDTechEx )

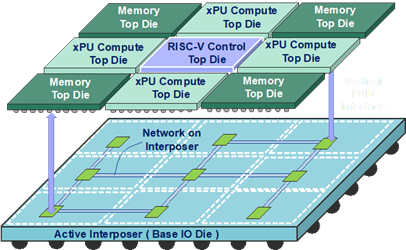

3D IC技術展現出了“超越摩爾定律”的巨大潛力,被視為后摩爾時代突破SoC集成度、性能等瓶頸的關鍵所在。通過3D IC 芯粒架構,多個同質和異質的小芯片/裸片得以在垂直尺度上整合于同一設計之中,這不僅提升了芯片的功能密度和單位性能,還增強了設計靈活性,同時降低了開發成本。典型的3D IC制造技術包括臺積電的 3D Fabric(SoIC)、 英特爾的Foveros、三星的X-Cube、日月光的VIPack 3D IC 等;從芯片最終商用角度來說,AMD MI300 GPU及Ryzen系列處理器;Intel 的Meteor Lake、Lunar Lake都是3D IC多芯粒堆疊的代表性案例。

(圖:3DIC Architecture)

AI時代驅動下的3D IC 應用趨勢

AI網絡加速CPO Chiplet部署進程

在AI高速發展的背景下,硅光集成憑借高速率+低功耗的優勢,有望成為數據中心互連的重要方案之一。作為一種新型光電子集成技術,CPO通過將光引擎與交換芯片近距離互連,縮短光信號輸入和運算單元間的電學互連長度。其優勢包括:高帶寬密度、低功耗、高集成度、低延時、小尺寸,并可通過半導體制造技術實現規模化生產。

報告大摩近期的報告預測,隨著英偉達Rubin服務器機架系統在2026年開始量產,CPO市場規模將在2023-2030年間以172%的年復合增長率擴張,預計2030年達到93億美元;在樂觀情景下,年復合增長率可達210%,市場規模將突破230億美元。

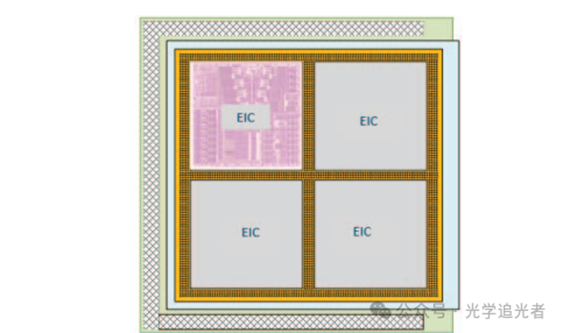

去年IEEE ECTC 2024上,Cisco公布了其基于3D封裝的3.2Tbs 光學引擎的技術細節,該技術集成了光子集成電路 (PIC) 和電氣 IC (EIC),使用晶圓級再分布層 (RDL) 實現緊湊的設計和低寄生電氣連接。

(來源:光學追光者公眾號)

上圖為4個800G EIC和1個3.2T PIC的封裝頂視圖,達到3.2Tb總帶寬,EIC互聯使用RDL層,PIC bump倒貼在FPOP上,使用邊緣耦合FAU光學封裝,EIC通過RDL連接到PIC bump上,EIC周圍和中間高的銅柱將頂部RDL和底部RDL連接到一起。

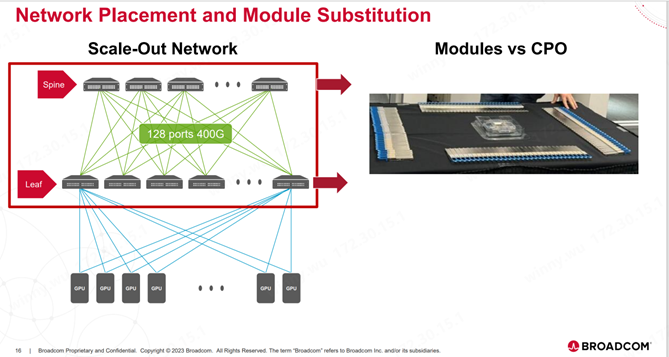

AI網絡Scale-out主要通過高速互聯容納更多節點,進而提升集群整體算力規模。當前機間通信主要以 400G-800G 為主,未來有望通過更高速率如 1.6T 組網互聯,以提高互聯帶寬,支持更多節點高速互聯;采用 CPO (Co-Packaged Optics) /NPO (Near Packaged Optics)、多異構芯片 C2C (Chip-to-Chip)封裝等方式降低延時,進而提升數據傳輸效率。

(來源:Broadcom)

博通引領多芯片設計轉向 3.5D 封裝技術

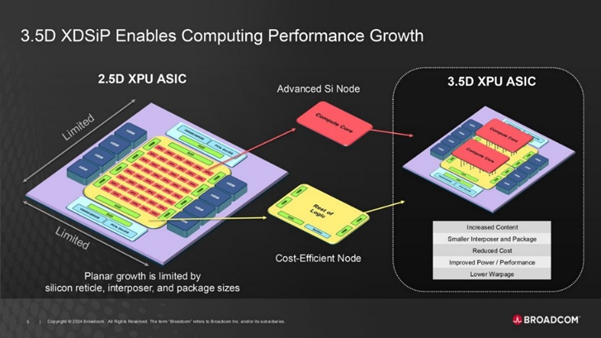

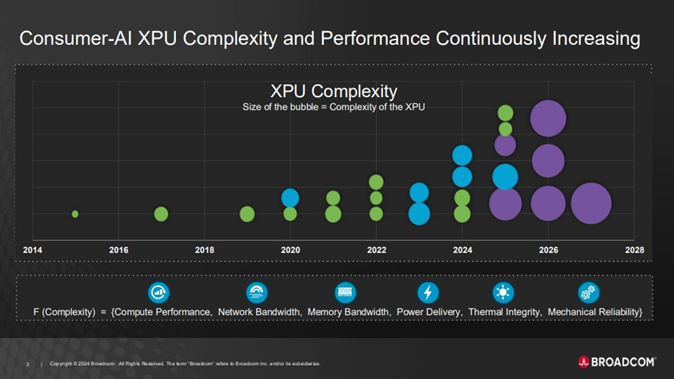

2024年年底,Broadcom 推出了其 3.5D eXtreme Dimension 系統級封裝 (3.5D XDSiP) 平臺,該平臺適用于 AI 和 HPC 工作負載的超高性能處理器。新平臺依賴于 TSMC 的 CoWoS 和其他先進封裝技術。它使芯片設計人員能夠構建 3D 堆棧邏輯、網絡和 I/O芯粒片以及 HBM 內存堆棧的系統級封裝 (SiP)技術。

(來源:Broadcom)

博通計劃將系統核心中的加速器核心或其他處理單元(如上圖紅色部分所示)劃分為任意數量的硅片。這些邏輯芯片可以包含通用 CPU 核心或高性能 AI 加速器,從 GPU 到張量處理單元 (TPU),或其他定制模塊。其余邏輯被重新安置在一個單獨的芯片上,在圖中以黃色顯示,其中包含從 I/O(包括基于PHY 的芯片間互連、高速 SerDes 和 HBM 內存接口)到充當處理器緩存的 SRAM 的所有內容。 這種設計方式同樣讓計算邏輯Die與I/O芯粒等其他模塊實現解耦,從而使用各自適用的相關工藝節點來實現更高性能和更佳的制造性價比。

“

簡單的來說,紅色部分稱作為計算Die ,而下面黃色的部分稱作3D Base Die,該芯粒可以包含各種I/O所需接口。這種設計方式讓計算Die與I/O芯粒等其他模塊實現解耦,從而使用各自適用的相關工藝節點來實現更高性能和更佳的制造性價比。運用3D Base Die作為3D IC 芯片的I/O基礎芯粒的架構設計已經成為AI時代異構芯片發展可預見的創新趨勢。

博通使用混合鍵合將上面較小的計算Die模塊堆疊在較大的Base芯片上,以實現連接和存儲。通常,芯片之間使用硅通孔 (TSV) 相互通信,這些硅通孔充當 3D 堆棧內的電梯井,在它們之間傳輸電力、信號和數據。而整個芯片的外圍,環繞著六個 HBM 模塊,采用了臺積電先進的工藝節點和 CoWoS 技術進行 2.5D 封裝。

(來源:Broadcom)

然而,隨著生成式AI模型的計算需求指數級增長,2.5D方案的帶寬和功耗限制變得愈發明顯。3.5D技術的出現,通過在封裝內堆疊更多的芯片模塊,實現了性能、功耗和成本的最佳平衡。3.5D 集成技術通過將 3D 硅堆疊與 2.5D 封裝相結合,能夠在不單純依賴制程工藝提升的情況下,實現芯片性能的顯著提升、功耗的有效降低以及成本的合理控制,從而成為了下一代 XPU 發展的必然趨勢。

國內存算一體3D IC 案例實現工藝節點效能突破

隨著AI高性能計算、自動駕駛等進入行業爆發期,巨大的算力催生了新的計算架構。由于芯片內數據提取與傳輸的需求日益增長,“存儲墻”成為了數據計算應用的一大障礙。深度學習加速的最大挑戰就是數據在計算單元和存儲單元之間頻繁的移動。

存算一體芯片技術的創新在很大程度上解決了芯片內不必要的數據搬移的延遲與功耗消耗,提升百倍千倍的AI計算效率,尤其是國內三維存算一體芯片的誕生將打破僅限于Intel與AMD等國際芯片企業在3DIC領域的壟斷地位。

2024年,奇異摩爾與復旦大學共同打造的三維存算一體芯片通過3D三維集成堆疊芯粒的形式實現晶體管密度等效2倍的提升,另一方面又實現了存儲與計算的緊耦合從而實現了高能效、降低存儲墻的性能。這款芯片利用3D封裝工藝加成存算一體技術僅使用28nm工藝就可以達到8/7nm工藝性能。在規避地緣政治管控的同時,實現先進工藝節點,成就高性能芯片。奇異摩爾自創立以來從片內互聯著手,不斷深耕Chiplet賽道,是國內首批布局3D Base Die互聯芯粒的科創企業。憑借在有源基板3D Base Die的設計能力以及先進封裝方面的資源整合成功聯合學術界實現三維存算一體芯片技術突破。(更多閱讀:芯片界奧林匹克放榜 !奇異摩爾與復旦大學三維集成芯片成果入選ISSCC 2025)

(來源:奇異摩爾)

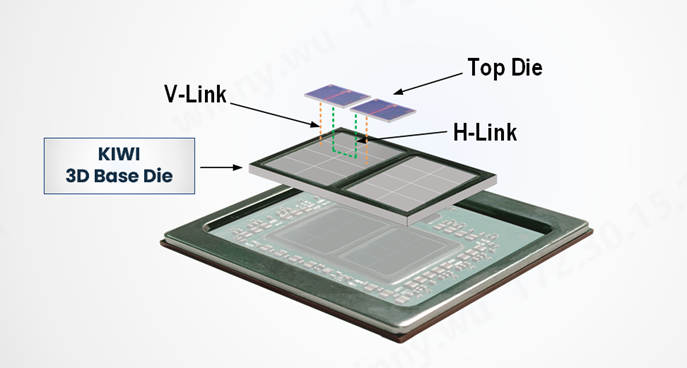

奇異摩爾的3D Base die(可理解為基于3D封裝的I/O Die)可以把原本集成在SoC中的Power、SRAM、I/O等非數字功能模塊拆分并拼搭進去,從而構成一個高度集成并節能的多核異構計算架構,同時實現上層的邏輯芯片面積最大化和芯片單位面積的最小化。在互聯方面,3D Base Die支持水平方向和垂直方向的異構芯片互連。垂直方向,通過TSV、microbump等3D互連技術與頂層邏輯芯粒、substrate垂直通信,從而以最小限度實現die與die之間的互連、片外連接,顯著提高芯粒集成密度,從而大規模提升芯片的算力。3D Base Die具有可復用功能,它與計算和存儲等芯粒解耦,進一步滿足存算一體芯片下一代技術的演進需求。

3D IC應用普及化的挑戰

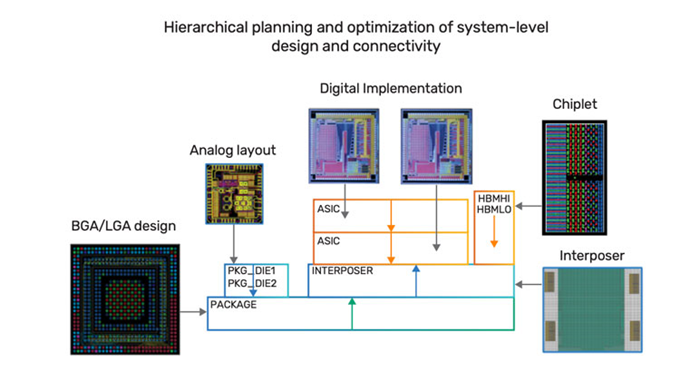

目前3D IC先進制造工藝技術仍舊掌握在少數企業手中,先進的節點工藝因為地緣政治的原因獲取上存在挑戰。從芯片制造本身來說,3D-IC的熱管理與機械應力、互聯、測試及相關材料的選擇等一系列復雜問題還存在設計與與制造方面的挑戰。此外,3D IC本身架構設計、EDA工具、封裝設計等板塊都具備復雜性和生態互通需求。設計人員需要要把這些必須具備的功能全部打通串聯,形成協同作戰,所以這是一個相對龐大的系統工程。

(來源:Cadence)

另一方面, 芯粒之間的互聯互通一直是3D IC 通用化落地的一個關鍵。國際標準方面,UCIe2.0 標準在去年下半年正式發布,標準的升級讓Chiplet生態又往前邁了一大步。UCIe 2.0解決了跨多個芯粒的 SiP 生命周期的可測試性、可管理性和調試 (DFx) 的設計挑戰。此次更新的一個關鍵功能是支持 3D 封裝,使芯粒能夠顯著提高帶寬密度和功率效率。UCIe 2.0 通過標準化接口和管理架構,促進了開放 Chiplet 生態系統的發展。

UCIe 2.0 在國內的生態通用化程度還需要不斷提高,盡管UCIe已經慢慢被國內芯片市場所接受,應用層面開始逐步出現落地案例。但仍然在芯粒協議、電源和熱管理等方向需要進行標準化和優化。3D IC 的大規模落地需要產業鏈上下游協同來實現生態的共榮,從封測制造、跨領域技術融合、標準共建與統一化等多維度方向來構建協調矩陣。

奇異摩爾作為Chiplet互聯的先行者將充分利用自身在3D IC設計與封裝量產的經驗資源與行業共赴這個價值萬億的產業新藍海。當設計軟件、材料科學、制造工藝、測試驗證等18個關鍵環節形成共振,當3000家上下游企業構建起創新聯合體,3D IC技術才能真正釋放其顛覆性潛能。這不是零和博弈的戰場,而是需要全行業以"硅基生命體"的共生理念,共同繪制半導體產業的下一個黃金時代。

關于我們AI網絡全棧式互聯架構產品及解決方案提供商

奇異摩爾,成立于2021年初,是一家行業領先的AI網絡全棧式互聯產品及解決方案提供商。公司依托于先進的高性能RDMA 和Chiplet技術,創新性地構建了統一互聯架構——Kiwi Fabric,專為超大規模AI計算平臺量

身打造,以滿足其對高性能互聯的嚴苛需求。

我們的產品線豐富而全面,涵蓋了面向不同層次互聯需求的關鍵產品,如面向北向Scale out網絡的AI原生智能網卡、面向南向Scale up網絡的GPU片間互聯芯粒、以及面向芯片內算力擴展的2.5D/3D IO Die和UCIe Die2Die IP等。這些產品共同構成了全鏈路互聯解決方案,為AI計算提供了堅實的支撐。

奇異摩爾的核心團隊匯聚了來自全球半導體行業巨頭如NXP、Intel、Broadcom等公司的精英,他們憑借豐富的AI互聯產品研發和管理經驗,致力于推動技術創新和業務發展。團隊擁有超過50個高性能網絡及Chiplet量產項目的經驗,為公司的產品和服務提供了強有力的技術保障。我們的使命是支持一個更具創造力的芯世界,愿景是讓計算變得簡單。奇異摩爾以創新為驅動力,技術探索新場景,生態構建新的半導體格局,為高性能AI計算奠定穩固的基石。

-

芯片

+關注

關注

459文章

52291瀏覽量

437584 -

AI

+關注

關注

88文章

34553瀏覽量

276087 -

人工智能

+關注

關注

1805文章

48833瀏覽量

247321 -

chiplet

+關注

關注

6文章

453瀏覽量

12908

原文標題:Chiplet&互聯專題:AI時代變革下 3D IC 芯粒技術的最新應用趨勢解讀

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

NVIDIA助力影眸科技3D生成工具Rodin升級

3D IC背后的驅動因素有哪些?

騰訊混元3D AI創作引擎正式發布

騰訊混元3D AI創作引擎正式上線

揭秘3D集成晶圓鍵合:半導體行業的未來之鑰

AI時代驅動下的3D IC應用趨勢

AI時代驅動下的3D IC應用趨勢

評論