本文由半導體產業縱橫(ID:ICVIEWS)編譯自chipestimate

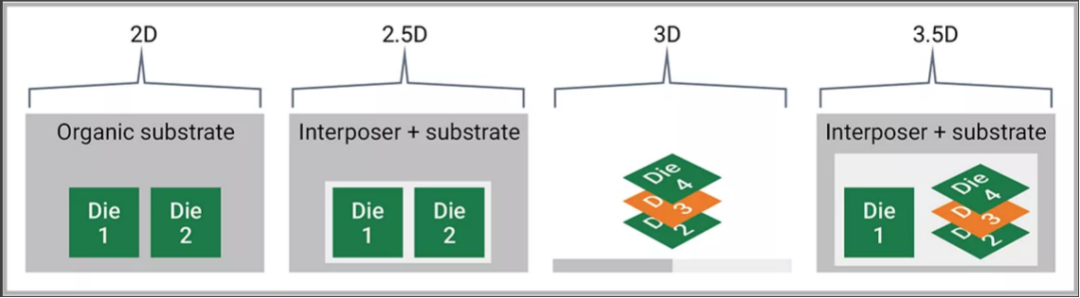

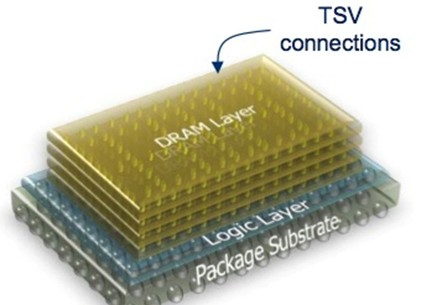

3D多芯片設計背后的驅動因素以及3D封裝的關鍵芯片到芯片和接口IP要求。3D 多芯片設計的市場預測顯示,硅片的設計和交付方式將發生前所未有的變化。IDTechEx 預測到 2028 年 Chiplet 市場規模將達到 4110 億美元。Market.us 報告預測先進封裝的規模將從 2023 年的 350 億美元增長到 2033 年的 1580 億美元,在同一報告中,Market.us 預測 1550 億美元中超過 600 億美元將是 3D SoC 和 3D 堆疊存儲器。這些數字和報告證實了快速采用多芯片設計和 3D 封裝的趨勢。本文重點介紹了 3D 多芯片設計背后的驅動因素以及 3D 封裝的關鍵芯片到芯片和接口 IP 要求。為了克服摩爾定律的限制并充分利用多芯片設計,設計人員可以通過多種方式在單個封裝中集成異構和同質芯片,如圖 1 所示。

圖 1:單個封裝中多個芯片集成的示例

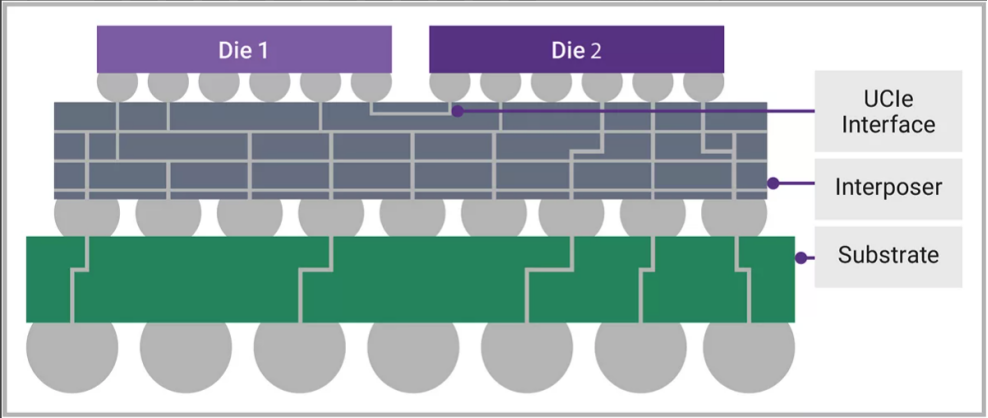

第一個例子展示了在一個封裝中集成 2 個或更多芯片,使用有機基板與單端或差分 IO 或短距離串行收發器連接。2D 集成方法成本相對較低,但芯片之間的帶寬有限。在 2.5D 集成中,如圖 2 所示,使用更高性能的中介層來實現多個芯片之間的高密度信號路由。然后將信號路由到封裝基板并輸出到封裝引腳。芯片通過芯片到芯片接口(如 UCIe)連接,每通道數據速率為 40G 或更高,旨在提供更高的帶寬,同時管理延遲和熱約束權衡。

圖 2:帶有中介層 + 基板封裝的 2.5D 集成

3D 集成可以減小尺寸,但更重要的是增加互連密度、降低延遲和降低互連功率,以實現更好的可擴展性。在 3.5D 集成中,包括從 3D 芯片堆棧到另一個 2D 芯片或 3D 芯片堆棧的芯片到芯片連接。

2.5D 多芯片設計驅動因素

先進的工藝節點正在推動更多的晶體管,但隨著摩爾定律的放緩和對提高復雜 AI 工作負載的計算性能的需求,設計需要比單個 800mm2 光罩所包含的更多的處理能力。作為第一步,設計人員可以將兩個或更多芯片放置在通過并行或串行 I/O 連接的封裝中,以擴展到更多的處理能力。更好的方法是將功能分解為多個較小的芯片(也稱為小芯片)。較小的芯片可以提高良率,并且即使增加了芯片到芯片接口的硅片面積和先進封裝成本,也可以提供更低成本的解決方案。這種多芯片設計方法包括優化每個芯片的工藝節點的選項,從而可以節省更多成本。

通過精心規劃,產品經理和架構師可以從可重復使用的芯片芯片集合中抽取,這些芯片可以集成在高級封裝中。例如,低端系統可能只有一個 AI 加速器芯片,而高性能產品可能包含多個 AI 加速器芯片以擴展性能。每個產品都可以使用同一組基本芯片以不同的組合或拓撲結構創建,以優化處理、熱管理和成本需求。此外,通過重復使用芯片并創建新的封裝來生產新產品,新系統的實施速度比使用傳統方法流片單片芯片要快得多,而且總擁有成本要低得多。

2.5D 集成已經在 FPGA 等應用中大規模生產了十多年。2.5D 集成面臨的一些挑戰是用于互連多個芯片的硅中介層的尺寸有限(近期為 3-5 個掩模版)。這限制了單個封裝中可以包含的芯片數量。較大的硅中介層會帶來可靠性問題,例如脆性和翹曲,這可能會影響凸塊連接的可靠性。為了解決其中一些尺寸和可靠性問題并擴展 2.5D 集成的實用性,業界正在開發帶有或不帶有硅橋的新型再分布層 (RDL) 中介層。硅橋可以增加比 RDL 中介層單獨提供的更高的信號密度路由。

3D多芯片設計驅動程序

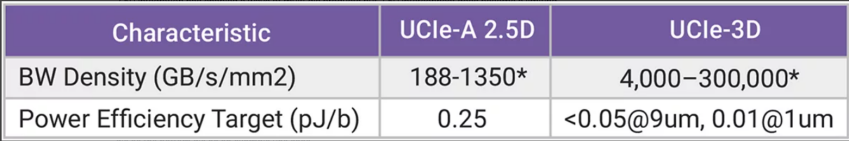

2.5D 集成已推動了多芯片產品的浪潮,但 2.5D 互連確實成為帶寬、處理和低延遲需求的限制因素,而這些需求的增長速度快于串行 2.5D 芯片到芯片鏈接能力。一種改進方法是使用 3D 芯片堆疊。3D 封裝有可能大幅提高互連密度,同時降低延遲和互連功耗,在某些拓撲中幾乎采用線到線鏈接。UCIe 規范顯示,UCIe Advanced(或 UCI-A)互連的目標帶寬規范為每平方毫米 (mm2) 188-1350 GB/s,而 UCIe-3D 的目標值為每 mm2 4TB/s,假設凸塊間距為 9um,如表 1 所示。同時,功率效率從 0.25 pJ/b 目標提高到 <0.05 pJ/b 目標。以計算芯片作為頂部芯片、緩存存儲器芯片作為底部芯片的系統為例,3D 封裝的低延遲優勢至關重要。

表 1:UCIe 聯盟 2.5D 和 3D 封裝的 KPI 目標

3D 封裝的 IP 注意事項

實現 3D 封裝在可擴展性和性能方面提供了許多好處,但也帶來了新的挑戰。為了應對這些挑戰,需要一種新方法和新工具來進行架構定義和規劃、可行性評估、原型設計和高級封裝設計。設計人員需要考慮新的多物理方面,例如不同芯片上元件之間的串擾以及多個芯片的熱管理,其中一個芯片可能會加熱附近的芯片。

有了 3D 封裝,IO 不再需要放置在芯片的邊緣。此外,通過使用混合鍵合技術,芯片之間的垂直芯片到芯片連接更加緊密。混合鍵合使用微小的銅對銅連接(<10um)連接封裝中的芯片。

接口 IP 3D 集成

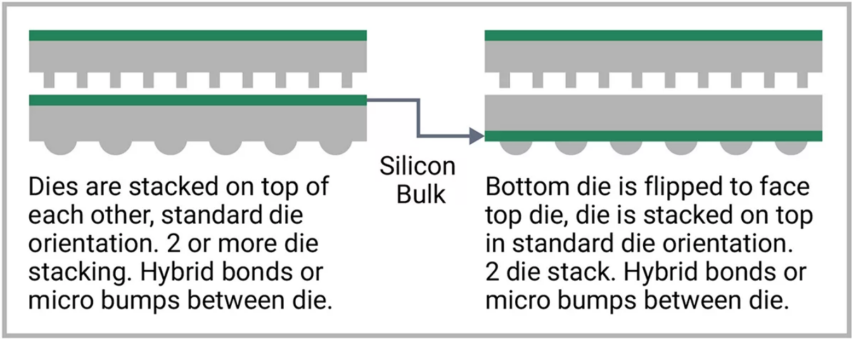

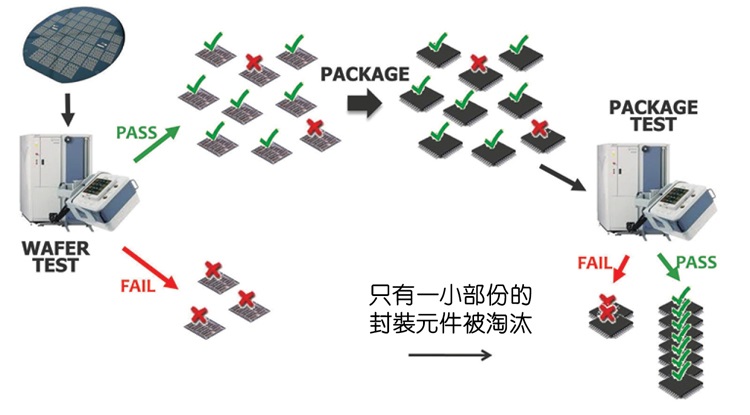

在考慮將接口 IP 與片外 IO PHY 集成時,并不像采用現有的 2D 實現并通過支持 3D 的工具運行它們那么簡單。IP 提供商必須仔細考慮提供在特定 3D IC 拓撲環境中工作的 IP。這將需要 IP 提供商和設計人員之間建立比過去更緊密的合作關系。一種常見的 3D 拓撲是晶圓上芯片 (CoW)。這種拓撲將經過測試的芯片堆疊在經過測試的晶圓頂部,然后切割成單個已知良好的芯片堆棧,然后組裝和測試以創建最終產品。芯片與晶圓的鍵合可以使用金屬對金屬混合鍵合技術或焊料凸塊連接。在這種拓撲中,與標準的面朝下的倒裝芯片組裝相比,底部芯片是翻轉的,因此金屬面朝上并直接面向頂部芯片的金屬,這是標準方向,如圖 3 所示。這提供了 2 個芯片之間最高密度和最低電阻的連接,但僅限于 2 個芯片的堆棧。面對面拓撲將芯片保持在標準倒裝芯片面朝下的方向,但允許在 HBM 存儲器等應用中堆疊 2 個以上的芯片。

圖 3:Face-to-Back vs. Face-to-Face

在Face-to-Back拓撲中,典型的堆棧將尖端計算節點作為頂部芯片,而下部芯片將位于較舊且成本較低的工藝節點上,并包括模擬和 I/O 功能,這些功能不會從擴展到最新節點中受益太多。

可能包含的底部芯片接口 IP 示例有 2.5D UCIe 接口(用于連接到同一封裝中的其他 3D 堆棧或 2D 芯片)或 PCIe 6.0/7.0 或 224G 以太網接口(用于通過封裝連接到外界)。在這些情況下,必須重新定位 PHY IP,以便來自凸塊的信號通過硅通孔 (TSV) 穿過硅塊連接到金屬層并路由到擴散層硅器件。IO 可能還需要考慮添加 TSV 和路由以將信號和電源連接到頂部芯片。在這種情況下,底部芯片(PHY IP)的尺寸可能會增加,以考慮這些額外的信號,并且設計人員必須執行額外的分析來解決多物理場對 TSV 信號和嵌入式電感的影響。

-

IC

+關注

關注

36文章

6120瀏覽量

179312 -

3D

+關注

關注

9文章

2959瀏覽量

110726 -

芯片設計

+關注

關注

15文章

1086瀏覽量

55639

發布評論請先 登錄

3D IC最快2014年可望正式量產

層疊的藝術:帶你深入了解3D IC

3D IC測試的現在與未來

3D IC背后的驅動因素有哪些?

3D IC背后的驅動因素有哪些?

評論