本案例為何需要引入FIFO

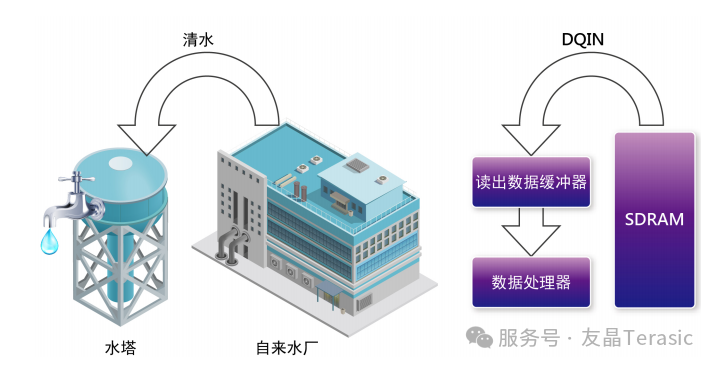

為了加深讀者對(duì) FPGA 端控制架構(gòu)的印象,在數(shù)據(jù)讀取的控制部分,首先我們可以將SDRAM 想作是一個(gè)自來(lái)水廠,清水得先送至用戶樓上的水塔中存放,在家里轉(zhuǎn)開(kāi)水龍頭要用水時(shí),才能及時(shí)供應(yīng),相同的原理,要讀取 SDRAM 中的數(shù)據(jù)來(lái)處理時(shí), FPGA 端的控制架構(gòu)中一定要有相當(dāng)于水塔功能的“讀出數(shù)據(jù)緩沖器”,在數(shù)據(jù)的處理上才會(huì)流暢。

而在使用自來(lái)水時(shí),自來(lái)水廠會(huì)補(bǔ)充清水至水塔中,用戶才可以連續(xù)的使用,同樣保存著從 SDRAM 讀出數(shù)據(jù)的緩沖器,當(dāng)數(shù)據(jù)量下降到某個(gè)程度時(shí)也必須要補(bǔ)充,在數(shù)據(jù)的處理上才不會(huì)中斷。

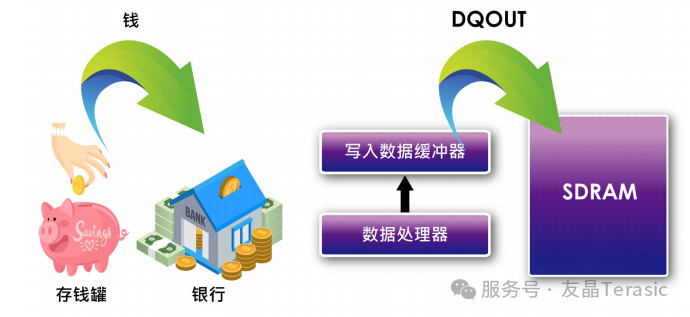

接著在數(shù)據(jù)寫(xiě)入的控制部分,我們可以將 SDRAM 想作是一個(gè)銀行,相信當(dāng)你身上有零錢時(shí)會(huì)順手存進(jìn)存錢罐,而不會(huì)費(fèi)時(shí)的跑一趟銀行去存錢,相同的原理,要將數(shù)據(jù)寫(xiě)入SDRAM 時(shí), FPGA 端的控制架構(gòu)中一定要有相當(dāng)于存錢罐功能的“寫(xiě)入數(shù)據(jù)緩沖器”,才不會(huì)降低 SDRAM 存取的使用效率。只有在存錢罐存到一個(gè)程度時(shí),我們才會(huì)取出錢拿去銀行存放,同樣保存著要寫(xiě)入 SDRAM 數(shù)據(jù)的緩沖器,當(dāng)數(shù)據(jù)量上升到某個(gè)程度時(shí)也必須要取出放進(jìn) SDRAM,才不會(huì)造成數(shù)據(jù)的遺失。

FIFO IP核簡(jiǎn)介

FIFO 本質(zhì)是RAM,其作用主要是作為緩存。

RAM和ROM的讀寫(xiě)都是根據(jù)地址來(lái)的,而FIFO( First In First Out)讀寫(xiě)不需要提供讀地址和寫(xiě)地址,其數(shù)據(jù)讀寫(xiě)按照先入先出的方式。所以FIFO的讀寫(xiě)非常簡(jiǎn)單,但靈活性稍差,不能做到靈活讀寫(xiě)。

FIFO分兩種:同步FIFO和異步FIFO。同步FIFO讀寫(xiě)時(shí)鐘是一個(gè)。異步FIFO的讀時(shí)鐘和寫(xiě)時(shí)鐘是分開(kāi)的。

同步FIFO和異步FIFO常應(yīng)用在同步時(shí)鐘系統(tǒng)和異步時(shí)鐘系統(tǒng)中。異步FIFO應(yīng)用場(chǎng)景如多比特?cái)?shù)據(jù)做跨時(shí)鐘域處理、前后帶寬不同步等。

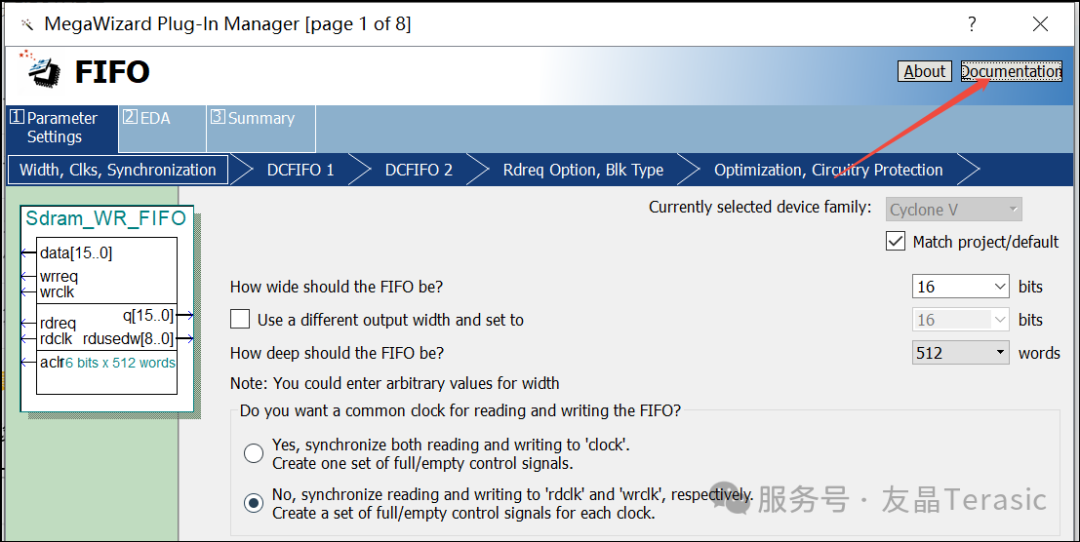

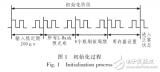

本案例中用到的是異步FIFO。異步FIFO IP模塊接口如下圖:

異步FIFO IP模塊信號(hào)描述如下:

*注意:FIFO復(fù)位信號(hào)是高電平有效。

打開(kāi)FIFO IP 設(shè)置界面可以找到FIFO文檔鏈接:

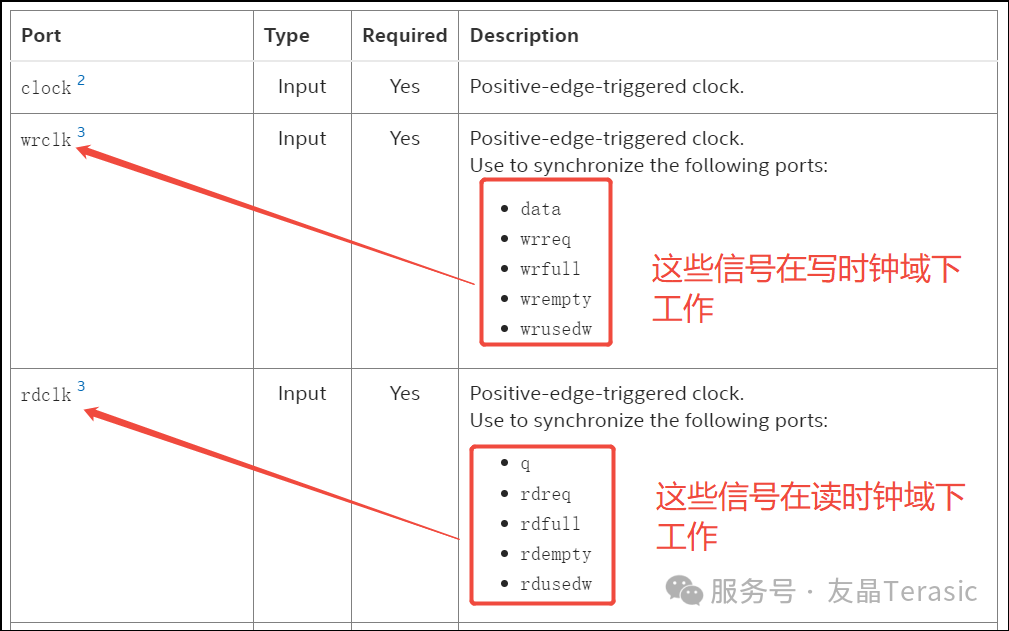

閱讀FIFO文檔可知異步FIFO寫(xiě)操作的各個(gè)信號(hào)在寫(xiě)時(shí)鐘下進(jìn)行工作,讀操作的各個(gè)信號(hào)在讀時(shí)鐘下進(jìn)行工作:

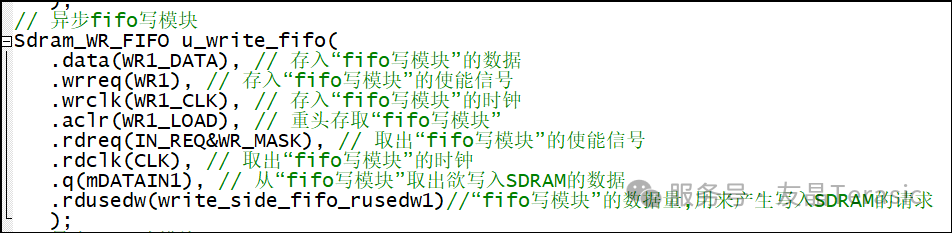

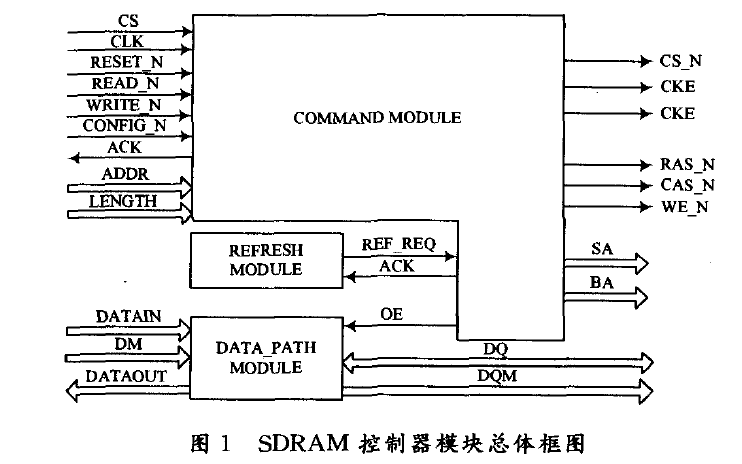

Sdram_Control.v文件里面例化了兩個(gè)FIFO模塊,一個(gè)是異步FIFO寫(xiě)模塊,用于緩存要寫(xiě)入SDRAM器件的數(shù)據(jù)。異步FIFO寫(xiě)模塊的數(shù)據(jù)寫(xiě)入在27MHz時(shí)鐘下進(jìn)行,數(shù)據(jù)的讀出在100MHz時(shí)鐘下進(jìn)行。

Sdram_Control.v文件例化的另一個(gè)FIFO模塊是異步FIFO讀模塊,用于緩存從SDRAM器件讀出的數(shù)據(jù)。異步FIFO讀模塊的數(shù)據(jù)寫(xiě)入在100MHz時(shí)鐘下進(jìn)行,數(shù)據(jù)的讀出在27MHz時(shí)鐘下進(jìn)行。

FIFO IP 設(shè)置

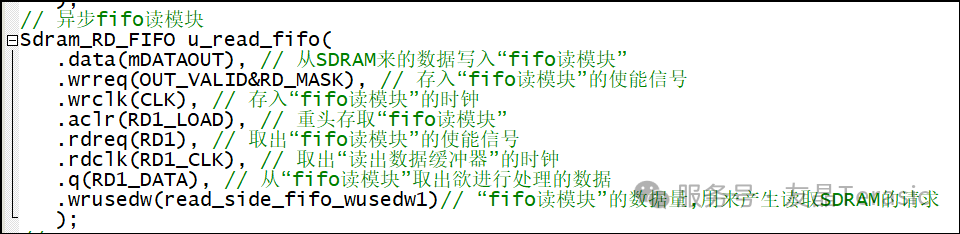

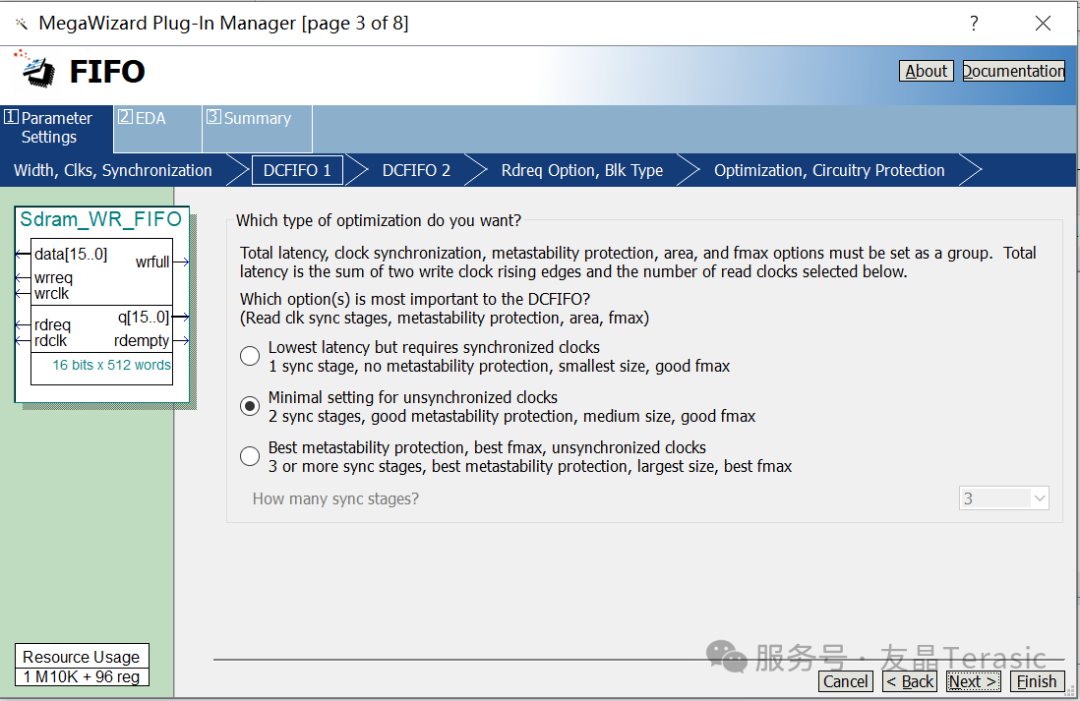

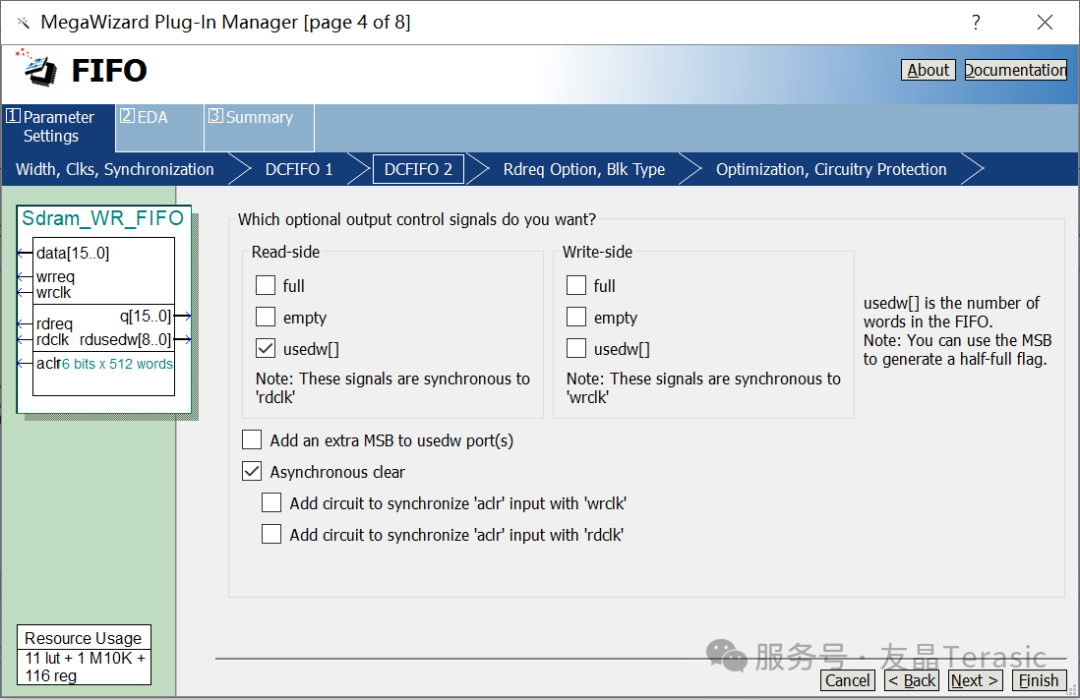

異步FIFO寫(xiě)模塊的IP設(shè)置如下:

FIFO數(shù)據(jù)位寬是16bit,與SDRAM位寬保持一致。

FIFO存儲(chǔ)深度設(shè)置512字,雖然實(shí)際存儲(chǔ)255個(gè)數(shù)據(jù),但一般深度都設(shè)置大一點(diǎn)。

勾選讀寫(xiě)時(shí)鐘分開(kāi)的選項(xiàng)。

勾選讀端口的rdusedw接口,用來(lái)生成寫(xiě)SDRAM器件的請(qǐng)求信號(hào)。

其他選項(xiàng)可以選擇默認(rèn)。

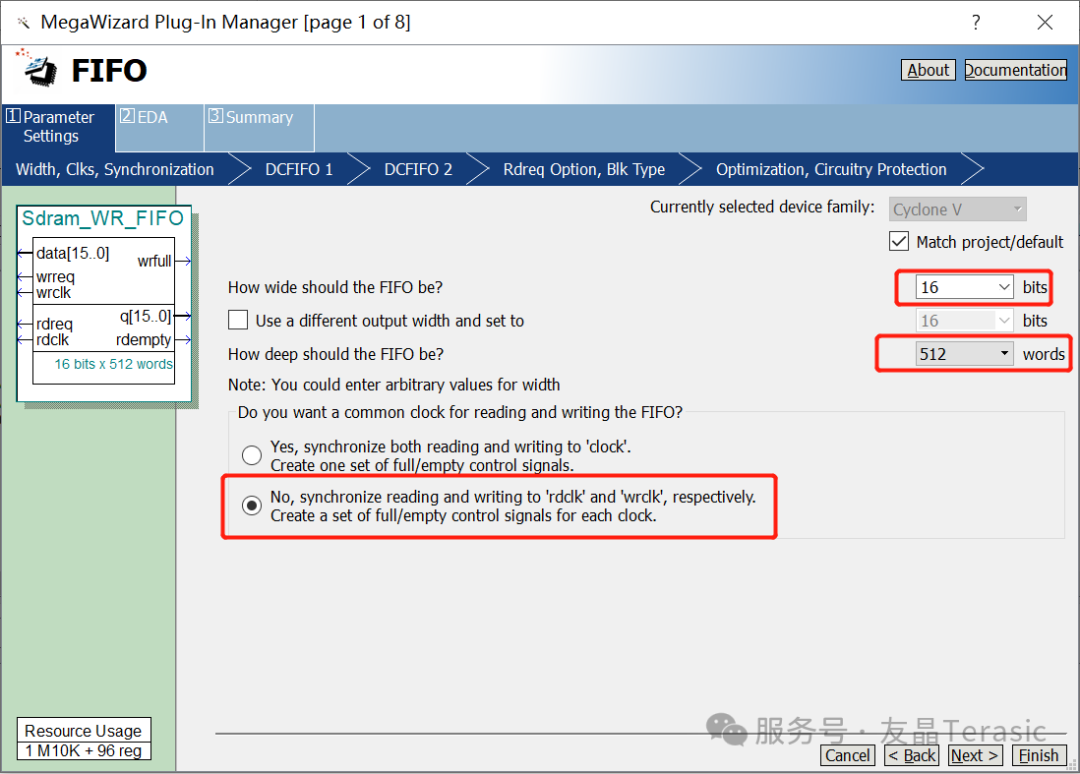

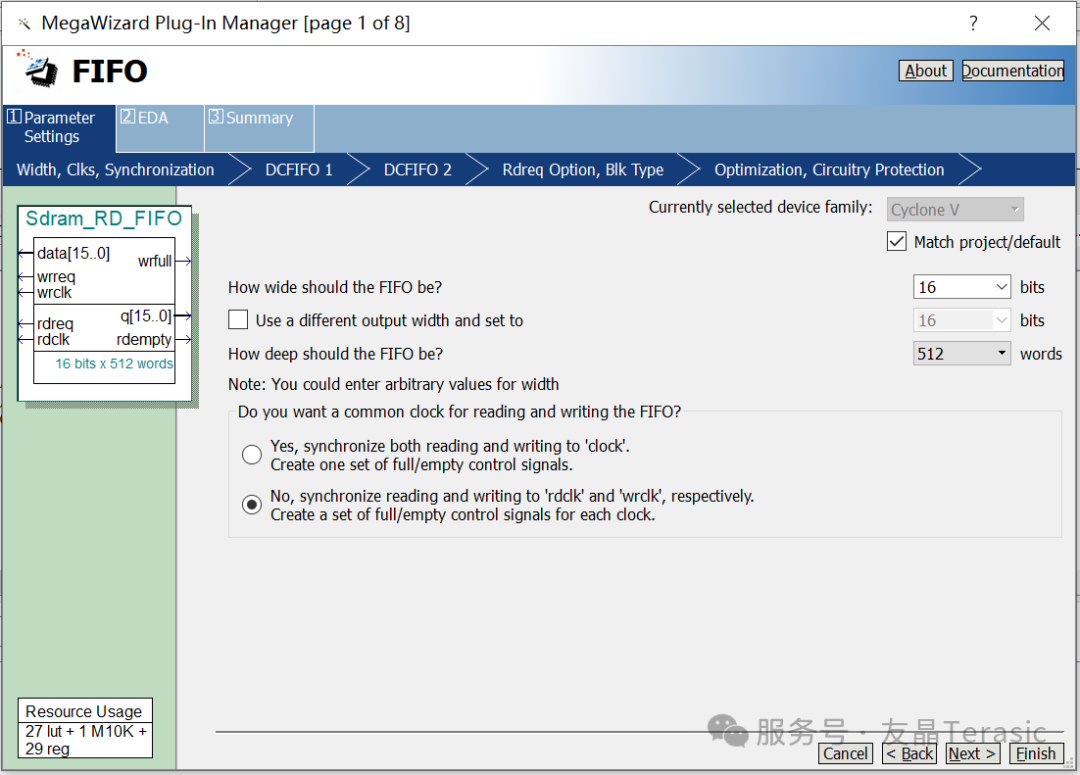

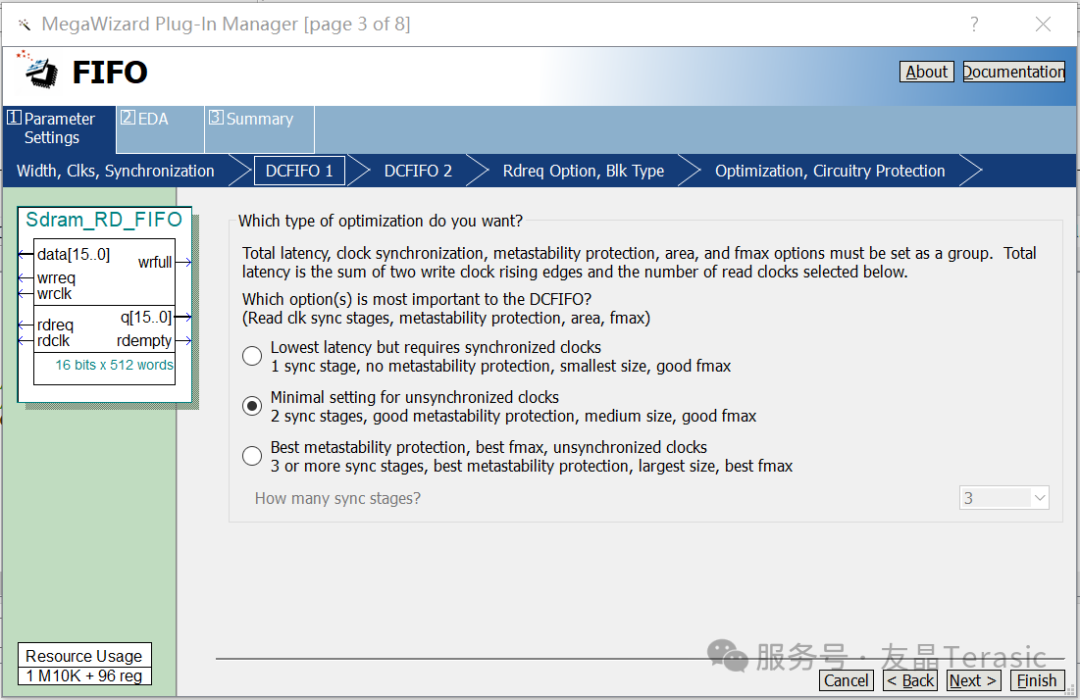

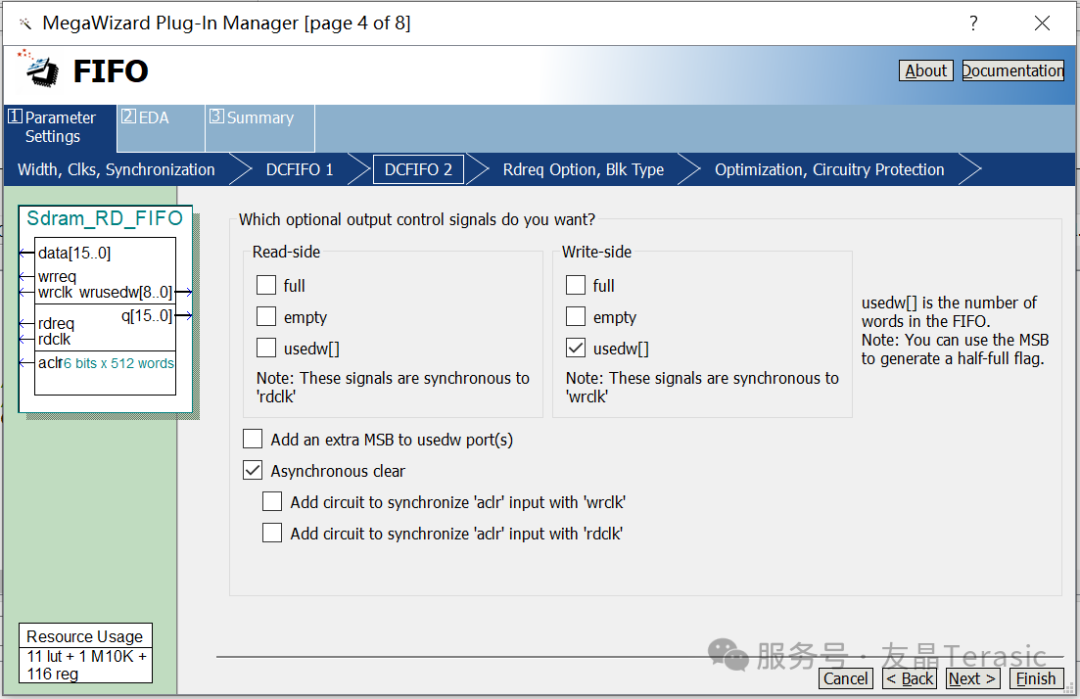

異步FIFO讀模塊的IP設(shè)置如下:

FIFO數(shù)據(jù)位寬是16bit,與SDRAM位寬保持一致。

FIFO存儲(chǔ)深度設(shè)置512字,雖然實(shí)際存儲(chǔ)127個(gè)數(shù)據(jù),但一般深度都設(shè)置大一點(diǎn)。

勾選讀寫(xiě)時(shí)鐘分開(kāi)的選項(xiàng)。

勾選寫(xiě)入端口的wrusedw接口,用來(lái)生成讀SDRAM器件的請(qǐng)求信號(hào)。

其他選項(xiàng)可以選擇默認(rèn)。

-

FPGA

+關(guān)注

關(guān)注

1639文章

21887瀏覽量

610860 -

控制器

+關(guān)注

關(guān)注

113文章

16789瀏覽量

181890 -

SDRAM

+關(guān)注

關(guān)注

7文章

438瀏覽量

55841 -

fifo

+關(guān)注

關(guān)注

3文章

396瀏覽量

44398

原文標(biāo)題:06-SDRAM控制器的設(shè)計(jì)——異步FIFO的調(diào)用

文章出處:【微信號(hào):友晶FPGA,微信公眾號(hào):友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析(異步FIFO讀寫(xiě)模塊、讀寫(xiě)SDRAM過(guò)程)

【開(kāi)源騷客】《輕松設(shè)計(jì)SDRAM控制器》第九講—解密讀寫(xiě)FIFO

Gowin SDRAM控制器的參考設(shè)計(jì)

使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器

SDRAM控制器簡(jiǎn)易化設(shè)計(jì)

SDRAM控制器的設(shè)計(jì)

FPGA讀寫(xiě)SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文

如何使用FPGA設(shè)計(jì)SDRAM控制器

基于SDRAM控制器軟核的Verilog設(shè)計(jì)

Gowin SDRAM控制器用戶指南

異步FIFO之Verilog代碼實(shí)現(xiàn)案例

FIFO設(shè)計(jì)—異步FIFO

PIC32系列參考手冊(cè)之DDR SDRAM控制器

SDRAM控制器設(shè)計(jì)之異步FIFO的調(diào)用

SDRAM控制器設(shè)計(jì)之異步FIFO的調(diào)用

評(píng)論