概述

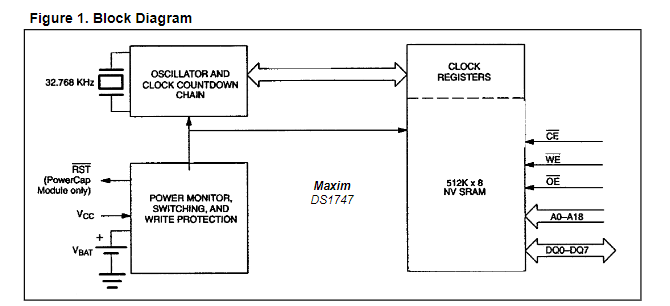

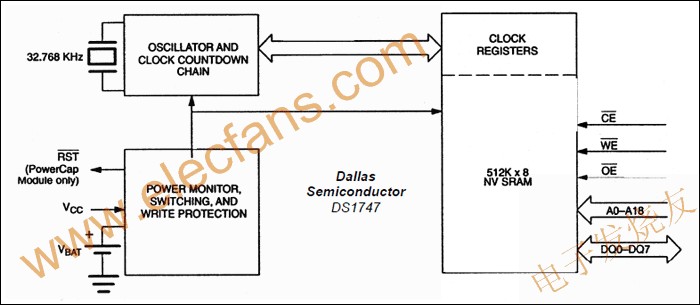

DS1747是功能完備、2000年兼容(Y2KC)的實時時鐘/日歷(RTC)和512k x 8非易失性SRAM。用戶可通過如圖1所示的單字節(jié)寬度的接口對DS1747內(nèi)部的所有寄存器進行訪問。RTC信息和控制位占用RAM中最高的8個地址。RTC寄存器包含世紀、年、月、日、星期、小時、分和秒數(shù)據(jù),采用24小時BCD格式。器件可自動對每個月份及閏年進行日期校正。RTC時鐘寄存器采用雙緩沖,可避免在時鐘更新周期內(nèi)訪問不正確的數(shù)據(jù)。雙緩沖系統(tǒng)還可以防止訪問時間寄存器時導致倒數(shù)計時無法減少而引起的時間丟失。DS1747還包含電源失效電路,用于當VCC電源超出容差時,禁止選通器件。由于低VCC引起不可預測的系統(tǒng)操作,該特性可以避免這種情況下的數(shù)據(jù)丟失,從而避免錯誤的訪問和更新。

數(shù)據(jù)表:*附件:DS1747 Y2K兼容、非易失時鐘RAM技術(shù)手冊.pdf

特性

- 集成的NV SRAM、實時時鐘(RTC)、晶體、電源失效控制電路和鋰電池

- 訪問時鐘寄存器方式與靜態(tài)RAM完全相同,這些寄存器位于RAM中最高的8個地址

- 世紀字節(jié)寄存器;Y2K兼容

- 完全的非易失性,可在缺少電源的條件下工作10年以上

- BCD編碼的世紀、年、月、日、星期、小時、分和秒數(shù)據(jù),可自動進行閏年補償至2100年

- 電池電壓指示標志

- 電源失效寫保護,允許±10%的V

CC電源容差 - 鋰電池處于開路的保鮮模式,直至首次電源加電

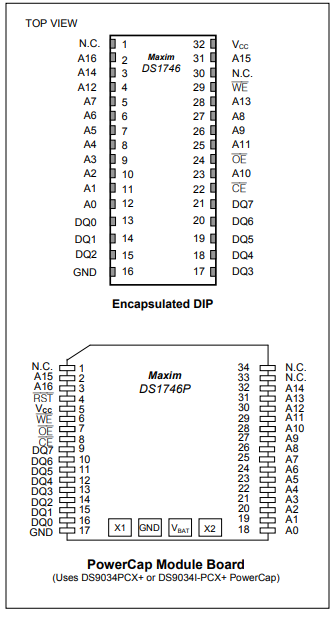

- 僅對于DIP模塊:

- 標準的JEDEC字節(jié)寬度512k x 8靜態(tài)RAM引腳排列

- 僅對于PowerCap模板:

- 可表貼的封裝直接與包含電池和晶體的PowerCap連接

- 可替換的電池(PowerCap)

- 上電復位輸出

- 引腳兼容于其他密度的DS174xP時間保持RAM

- 可提供工作在工業(yè)級溫度范圍(-40°C至+85°C)的芯片

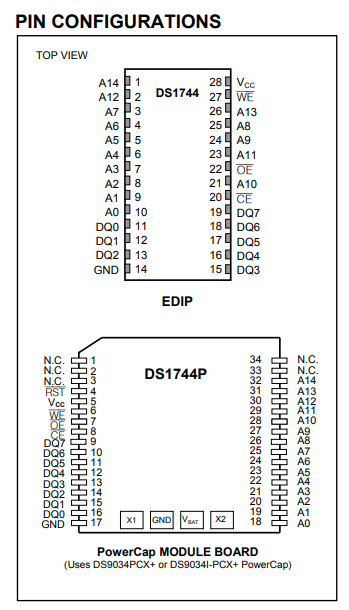

引腳配置

設置時鐘

如表2所示,控制寄存器的第7位是W(寫)位。將W位設置為1會停止對設備寄存器的更新。用戶隨后可以將正確的日期和時間值加載到所有八個寄存器中,然后對控制寄存器進行00小時的寫入周期,以清除W位并將這些新設置傳輸?shù)綍r鐘中,從而允許從新的設定點恢復計時操作。

再次參考表2,控制寄存器的位6是R(讀取)位。將R位設置為1會停止對設備寄存器的更新。用戶隨后可以從八個寄存器中讀取日期和時間值,而這些內(nèi)容在I/0操作期間可能不會改變。隨后向控制寄存器寫入00小時以清除R位,允許計時操作從之前的設定點恢復。如果在該寫入操作中將W或R位設置為1,則控制寄存器位0:5(世紀值)的預先存在的內(nèi)容將被忽略/不被控制的寫入周期修改。

如果在寫入操作中將W位清除為0,則控制寄存器位0:5(世紀值)的預先存在的內(nèi)容將通過寫入周期修改為控制。如果在該寫入操作中將R位清除為0,則控制寄存器位0:5(世紀值)的預先存在的內(nèi)容將不會被寫入周期修改為控制。

-

sram

+關注

關注

6文章

783瀏覽量

115728 -

RTC

+關注

關注

2文章

614瀏覽量

68431 -

DS1747

+關注

關注

0文章

2瀏覽量

5799

發(fā)布評論請先 登錄

DS1746 pdf datasheet (Y2K兼容、非易

非易失Y2K兼容時鐘RAM DS1557

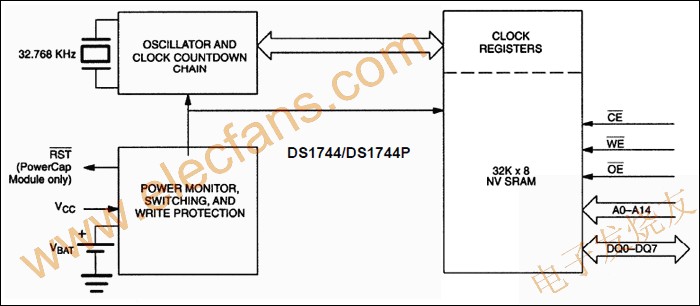

Y2K兼容、非易失時鐘SRAM DS1744

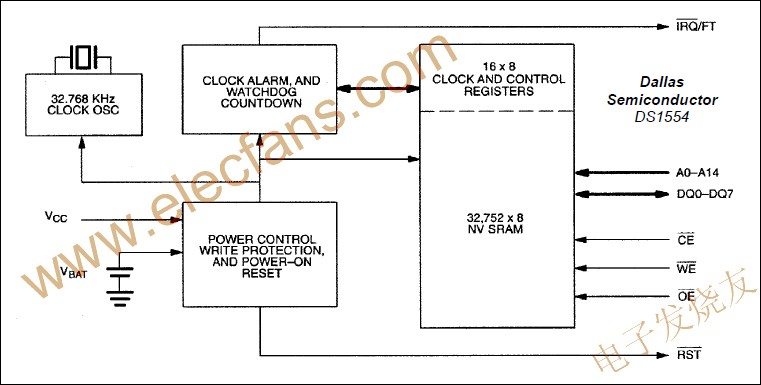

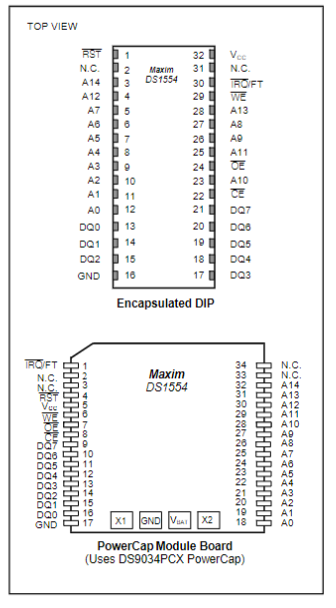

256k非易失、Y2K兼容時鐘RAM DS1554

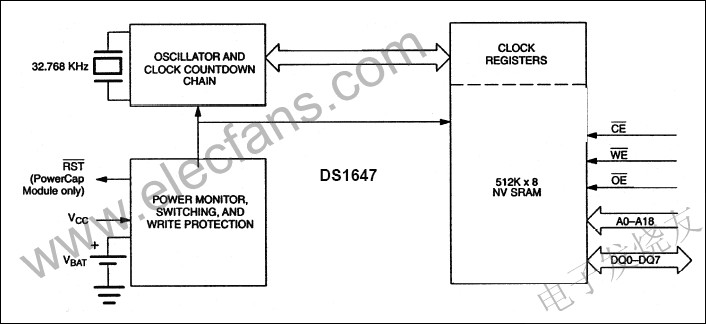

DS1647為512k x 8非易失性靜態(tài)RAM

DS1248,DS1248P帶有隱含時鐘非易失RAM

DS1746,DS1746P非易失時鐘RAM

DS1747,DS1747P Y2K兼容、非易失時鐘RAM

DS1744系列Y2K兼容、非易失時鐘RAM技術(shù)手冊

DS1554 256k非易失、Y2K兼容時鐘RAM技術(shù)手冊

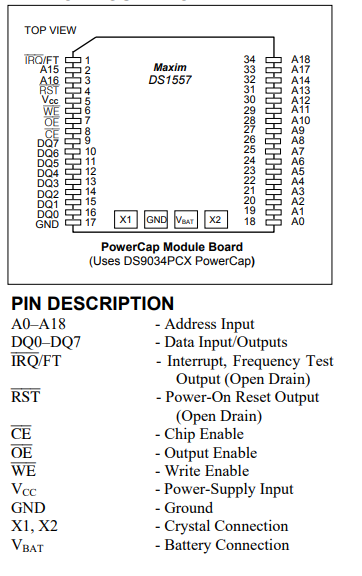

DS1557 4M非易失、Y2K兼容時鐘RAM技術(shù)手冊

DS1747 Y2K兼容、非易失時鐘RAM技術(shù)手冊

DS1747 Y2K兼容、非易失時鐘RAM技術(shù)手冊

評論