文章來源:半導體與物理

原文作者:jjfly686

本文介紹了芯片結構的柵極(Gate)。

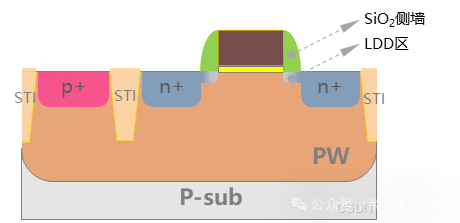

柵極(Gate)是晶體管的核心控制結構,位于源極(Source)和漏極(Drain)之間。其功能類似于“開關”,通過施加電壓控制源漏極之間的電流通斷。例如,在MOS管中,柵極電壓的變化會在半導體表面形成導電溝道,從而調節電流的導通與截止。

柵極材料與關鍵工藝

柵極材料的演變

傳統多晶硅柵極

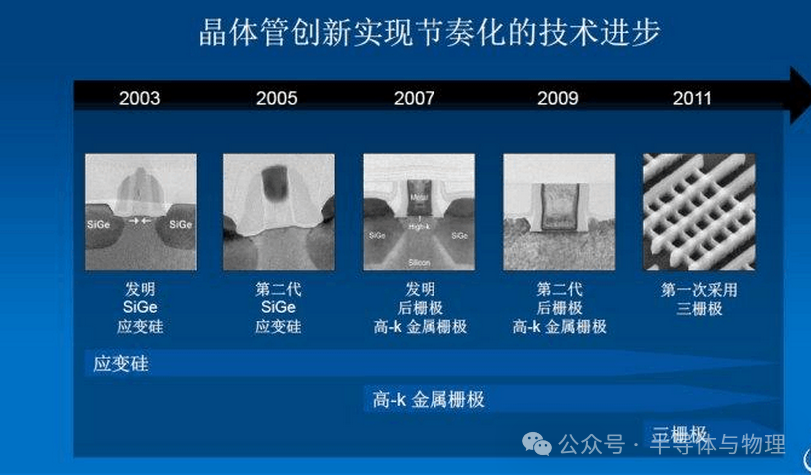

早期采用多晶硅(Poly-Si)作為柵極材料,但因其電阻較高且與High-k介電層兼容性差,逐漸被金屬柵極取代。

金屬柵極

現代先進工藝使用金屬材料(如鎢、鈷、鈦等)或金屬硅化物(如硅化鎢、硅化鈦),具有低電阻和高穩定性優勢。

功函數金屬層

通過鈦等金屬調節晶體管的閾值電壓,例如在N型/P型晶體管中分別使用不同金屬組合。

關鍵工藝技術

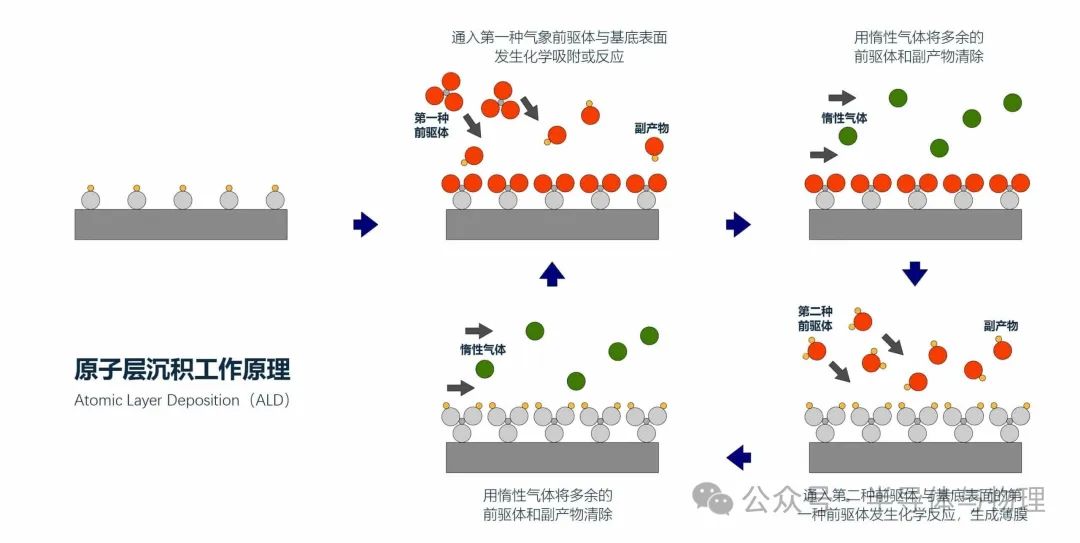

原子層沉積(ALD)

用于沉積高均勻性的High-k介電層(如氧化鉿)或金屬層,確保薄膜厚度精確到原子級別。

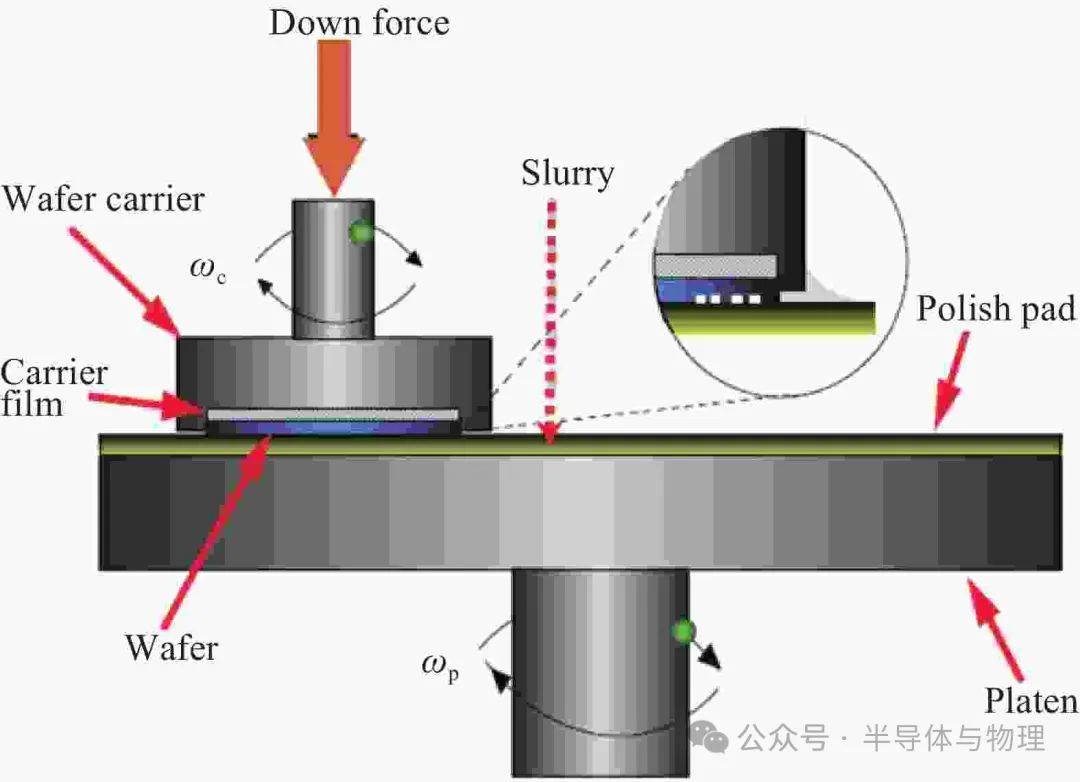

化學機械拋光(CMP)

用于金屬柵極的平坦化處理,避免后續工藝中的金屬殘留問題。

柵極制造的典型流程

襯底與柵介質層制備

襯底處理

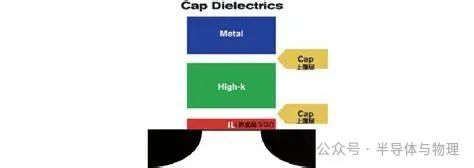

在硅襯底上生長氧化層或High-k介電層(如HfO?),作為柵極與溝道之間的絕緣層。

界面鈍化

通過惰性氣體等離子體處理去除界面游離元素(如氧或硅),防止后續高溫工藝中形成二氧化硅缺陷層。

柵極結構形成

多晶硅/金屬沉積

通過物理氣相沉積(PVD)或化學氣相沉積(CVD)形成多晶硅層或金屬層。

疊層結構構建

例如,在DRAM器件中,依次堆疊多晶硅層、阻擋層(如硅氮化鈦)和金屬硅化物層,以抑制離子擴散。

圖案化與刻蝕

利用光刻和干法刻蝕技術定義柵極形狀,需精確控制線寬以匹配納米級晶體管尺寸。

金屬柵極的先進工藝

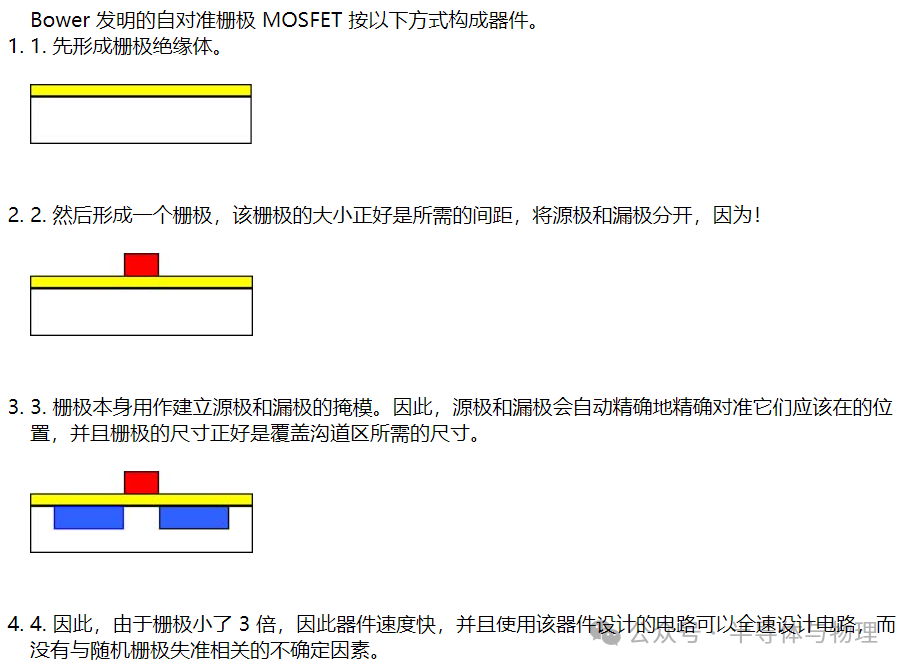

偽柵極替換(Replacement Gate)

虛設柵極形成

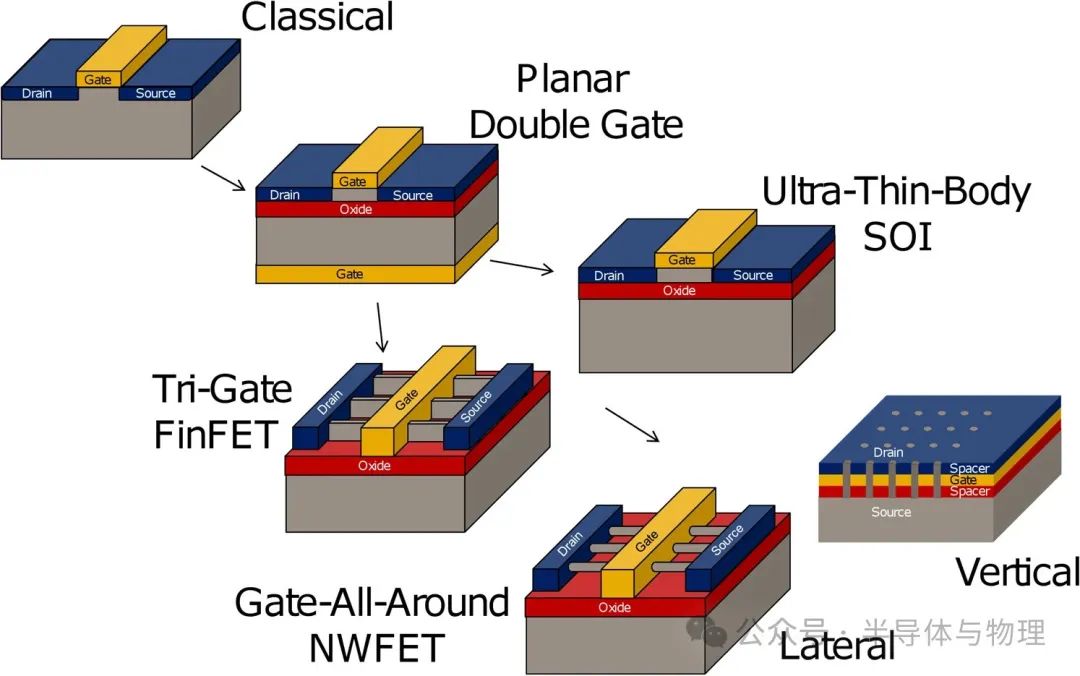

在FinFET或GAA晶體管中,先用多晶硅制作虛設柵極并完成側墻刻蝕。

溝槽填充

移除虛設柵極后,依次沉積High-k介電層、功函數金屬層(如TiN、TaN)和填充金屬(如鎢、鈷)。

平坦化處理

通過CMP去除多余金屬,確保柵極與層間介質層平整。

-

芯片

+關注

關注

460文章

52511瀏覽量

440860 -

晶體管

+關注

關注

77文章

10020瀏覽量

141665 -

柵極

+關注

關注

1文章

185瀏覽量

21365

原文標題:芯片結構:柵極(Gate)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶體管柵極結構形成

晶體管柵極結構形成

評論