概述

LTC6952 是一款高性能、超低抖動(dòng) JESD204B/C 時(shí)鐘生成和分配 IC。該器件包括一個(gè)鎖相環(huán) (PLL) 內(nèi)核,由基準(zhǔn)分頻器、具有鎖相指示器的相位頻率檢波器 (PFD)、超低噪聲充電泵和整數(shù)反饋分頻器構(gòu)成。LTC6952 的 11 個(gè)輸出可配置為最多 5 個(gè) JESD204B/C subclass 1 器件時(shí)鐘/SYSREF 對(duì)以及一個(gè)通用輸出,或者就是 11 個(gè)面向非 JESD204B/C 應(yīng)用的通用時(shí)鐘輸出。每個(gè)輸出都有自己的可單獨(dú)編程分頻器和輸出驅(qū)動(dòng)器。所有輸出也可以采用單獨(dú)的粗略半周期數(shù)字延遲和精細(xì)模擬時(shí)間延遲實(shí)現(xiàn)同步,并設(shè)定為精確的相位對(duì)齊。

對(duì)于需要 11 個(gè)以上總輸出的應(yīng)用,可以使用 EZSync 或 ParallelSync 同步協(xié)議將多個(gè) LTC6952 連接在一起。

數(shù)據(jù)表:*附件:LTC6952具有11個(gè)輸出并支持JESD204B JESD204C協(xié)議的超低抖動(dòng)、4.5GHz PLL技術(shù)手冊(cè).pdf

應(yīng)用

- 高性能數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘

- 無線基礎(chǔ)設(shè)施

- 測(cè)試和測(cè)量

特性

- JESD204B/C,子類 1 SYSREF 信號(hào)生成

- 低噪聲整數(shù) N PLL

- 附加輸出抖動(dòng) < 6fs

RMS- (集成帶寬 = 12kHz 至 20MHz,f = 4.5GHz)

- 附加輸出抖動(dòng) 65fs

RMS(ADC SNR 方法) - EZSync ^?^ 、ParallelSync^?^ 多芯片同步

- –229dBc/Hz 歸一化帶內(nèi)相位本底噪聲

- –281dBc/Hz 歸一化帶內(nèi) 1/f 噪聲

- 11 個(gè)獨(dú)立低噪聲輸出,具有可編程粗?jǐn)?shù)字延遲和精細(xì)模擬延遲

- 靈活的輸出可以用作套件時(shí)鐘或 SYSREF 信號(hào)

- 基準(zhǔn)輸入頻率達(dá) 500MHz

- LTC6952Wizard^?^ 軟件設(shè)計(jì)工具支持

- 工作結(jié)溫范圍為 –40oC 至 125°C

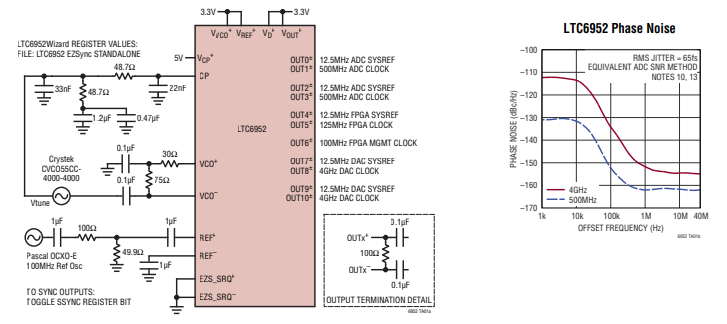

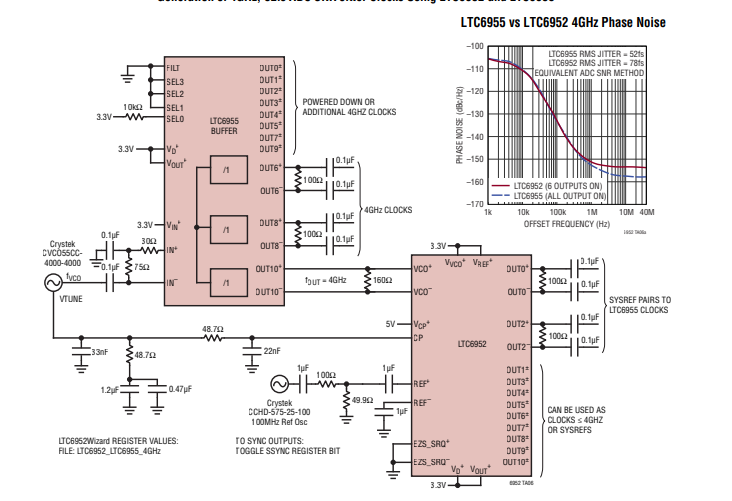

典型應(yīng)用

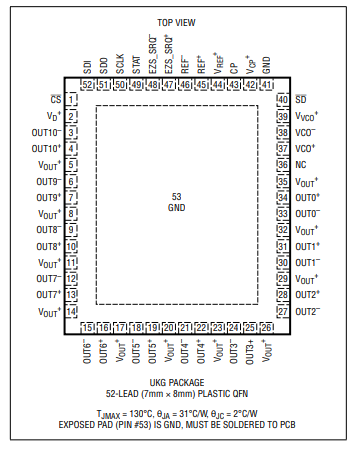

引腳圖

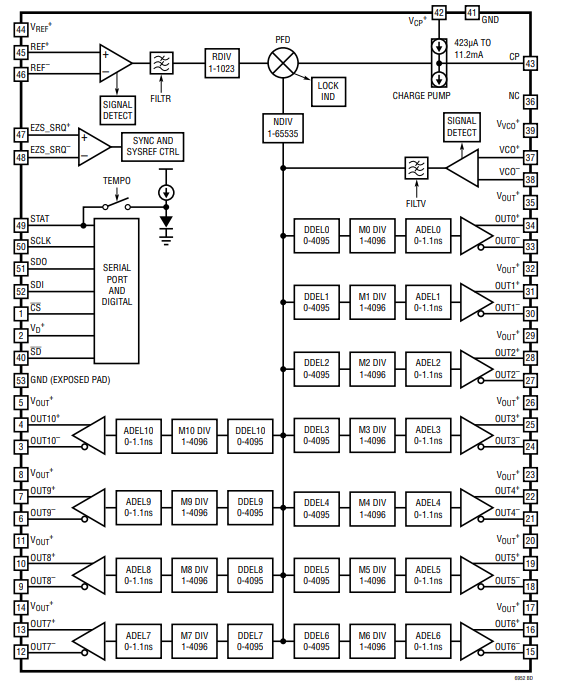

框圖

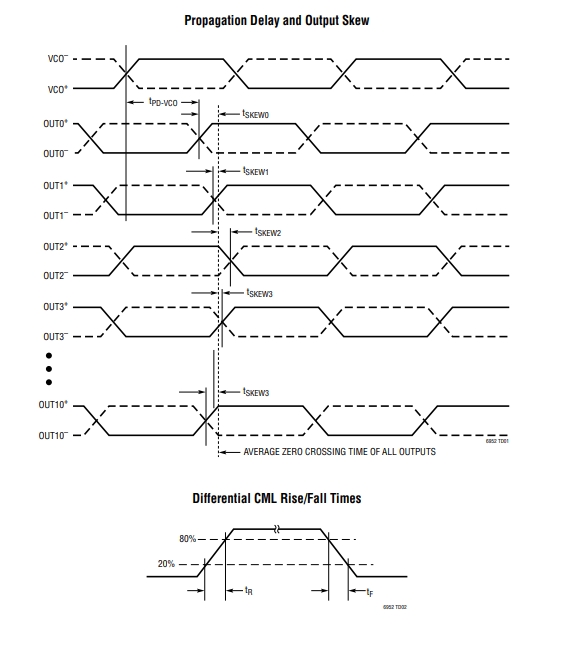

時(shí)序圖

應(yīng)用電路

-

分頻器

+關(guān)注

關(guān)注

43文章

491瀏覽量

50916 -

pll

+關(guān)注

關(guān)注

6文章

887瀏覽量

136148 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1887瀏覽量

132933

發(fā)布評(píng)論請(qǐng)先 登錄

JESD204B的系統(tǒng)級(jí)優(yōu)勢(shì)

JESD204B串行接口時(shí)鐘的優(yōu)勢(shì)

帶JESD204B輸出的14位170Msps雙通道ADC

JESD204C的標(biāo)準(zhǔn)和新變化

JESD204B協(xié)議有什么特點(diǎn)?

如何采用系統(tǒng)參考模式設(shè)計(jì)JESD204B時(shí)鐘

JESD204B協(xié)議介紹

LTC6952 具有 11 個(gè)輸出和 JESD204B/JESD204C 支持的超低抖動(dòng) 4.5GHz PLL

LTC6952:超低抖動(dòng)、4.5 GHz PLL,帶11個(gè)輸出和JESD204B/JESD204C支持數(shù)據(jù)表

LTC6953:超低抖動(dòng)、4.5 GHz時(shí)鐘分配器,帶11個(gè)輸出和JESD204B/JESD204C支持數(shù)據(jù)表

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

從JESD204B升級(jí)到JESD204C時(shí)的系統(tǒng)設(shè)計(jì)注意事項(xiàng)

JESD204B使用說明

LTC6953具有11個(gè)輸出并支持JESD204B/JESD204C協(xié)議的超低抖動(dòng)、4.5GHz時(shí)鐘分配器技術(shù)手冊(cè)

LTC6952具有11個(gè)輸出并支持JESD204B/JESD204C協(xié)議的超低抖動(dòng)、4.5GHz PLL技術(shù)手冊(cè)

LTC6952具有11個(gè)輸出并支持JESD204B/JESD204C協(xié)議的超低抖動(dòng)、4.5GHz PLL技術(shù)手冊(cè)

評(píng)論