概述

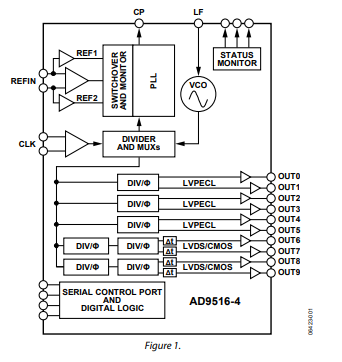

AD9516-4*提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.45 GHz至1.80 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

AD9516-4具有出色的低抖動和相位噪聲特性,可極大地提升數據轉換器的性能,并且也有利于其它相位噪聲和抖動要求嚴苛的應用。

數據表:*附件:AD9516-4 14路輸出時鐘發生器,集成1.6GHz VCO技術手冊.pdf

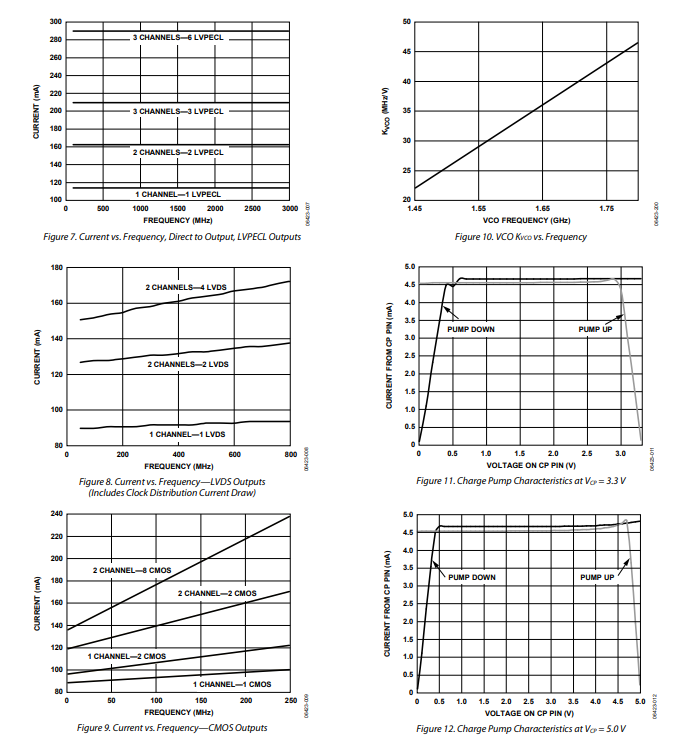

AD9516-4提供6路LVPECL輸出(分為三對)、4路LVDS輸出(分為兩對)和8路CMOS輸出(每路LVDS輸出對應兩路)。LVPECL輸出的工作頻率達1.6 GHz,LVDS輸出的工作頻率達800 MHz,CMOS輸出的工作頻率達250 MHz。

每對輸出均有分頻器,其分頻比和粗調延遲(或相位)均可以設置。LVPECL輸出的分頻范圍為1至32。LVDS/CMOS輸出的分頻范圍最高可達1024。

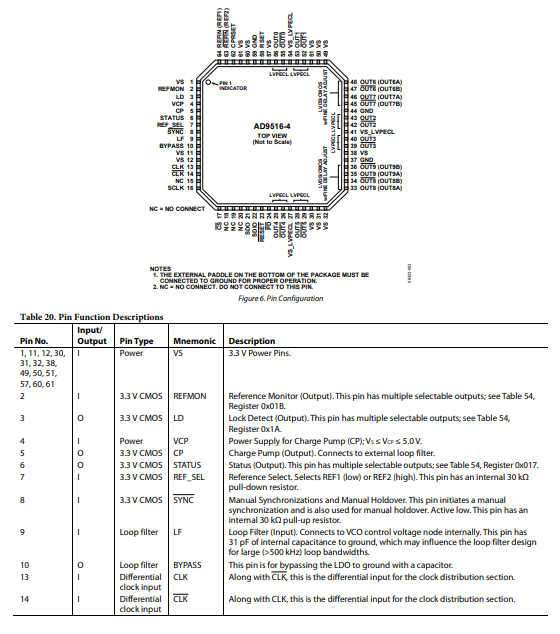

AD9516-4提供64引腳LFCSP封裝,可以采用3.3 V單電源供電。將電荷泵電源(VCP)與5V電壓相連時,可以使用外部VCO,它需要更寬的電壓范圍。獨立的LVPECL電源可以為2.5 V至3.3 V(標稱值)。

AD9516-4的額定工作溫度范圍為?40°C至+85°C工業溫度范圍。

應用

- 低抖動、低相位噪聲時鐘分配

- 10/40/100 Gb/s網絡線路卡,包括SONET、同步以太網、OTU2/3/4

- 前向糾錯(G.710)

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE提供時鐘

- 高性能無線收發器

- 自動測試設備(ATE)和高性能儀器儀表

特性

- 低相位噪聲鎖相環(PLL)

片內VCO的調諧頻率范圍為1.45 GHz至1.80 GHz

可選外部VCO/VCXO,最高達2.4 GHz

1路差分或2路單端基準輸入 - 6對1.6 GHz LVPECL輸出

每對輸出共用1至32分頻器和粗調相位延遲

加性輸出抖動:225 fs均方根值

通道間偏斜成對輸出小于10 ps - 4對800 MHz LVDS時鐘輸出

每對輸出共用兩個1至32級聯分頻器和粗調相位延遲

加性輸出抖動:275 fs均方根值

上電時所有輸出自動同步

提供手動輸出同步

64引腳LFCSP - 欲了解更多特性,請參考數據手冊

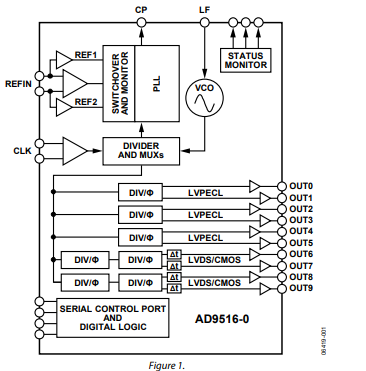

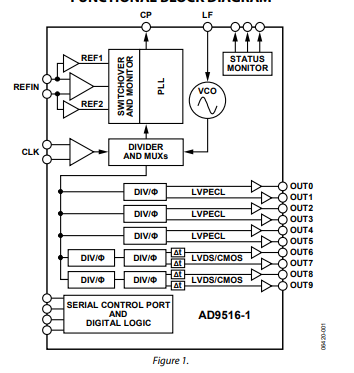

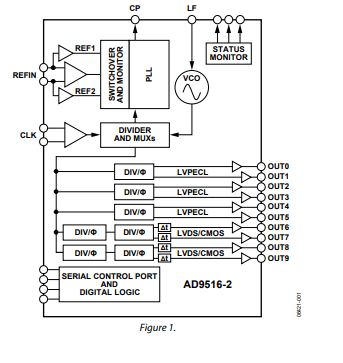

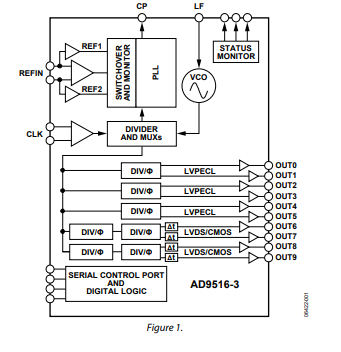

框圖

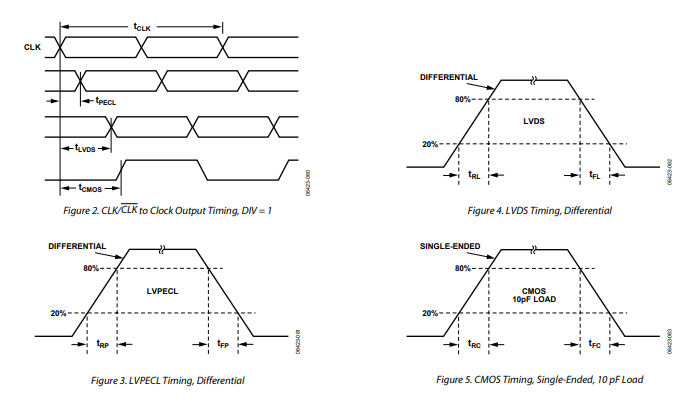

時序圖

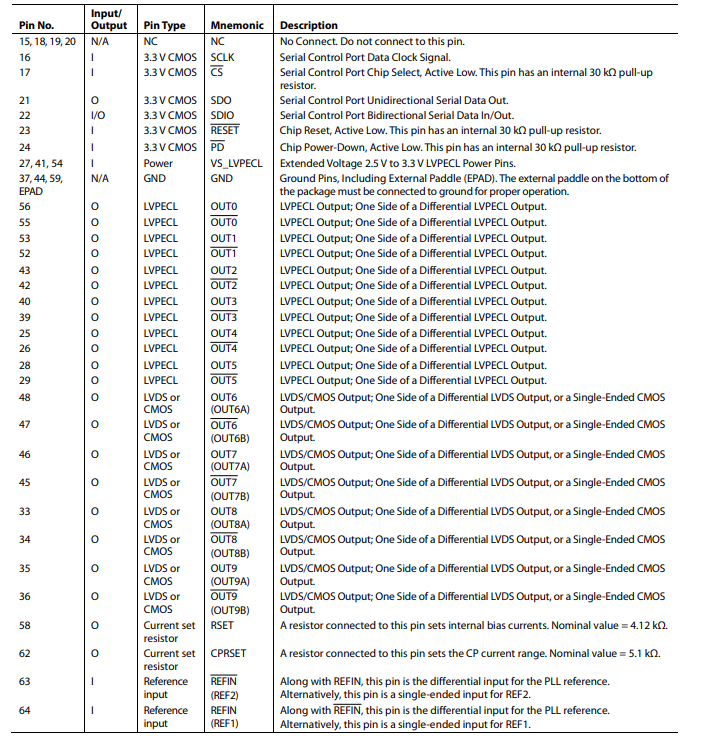

引腳配置描述

典型性能特征

數字鎖檢測(DLD)

通過在每個引腳上的多路復用器選擇合適的輸出,DLD功能可在LD、STATUS和REFMON引腳上實現。當PFD輸入的上升沿時間差小于指定值(鎖定閾值)時,DLD電路指示鎖定狀態;當時間差超過指定值(解鎖閾值)時,指示鎖定丟失。需注意,解鎖閾值比鎖定閾值更寬,這允許在鎖定窗口外出現一定誤差,而不會使鎖定指示器抖動。

鎖檢測窗口定時取決于三個設置:數字鎖檢測窗口位(寄存器0x018[14])、抗反沖脈沖寬度設置(寄存器0x017[1:0],見表2)和鎖檢測計數器(寄存器0x018[6:5])。只有在連續多個PFD周期內時間差小于鎖檢測閾值時,才會指示鎖定。鎖檢測電路會持續指示鎖定,直到時間差大于解鎖閾值,并出現單個后續周期。為使鎖定檢測正常工作,PFD頻率周期必須大于解鎖閾值。鎖定所需的連續PFD周期數可通過寄存器0x018[6:5]編程設置。

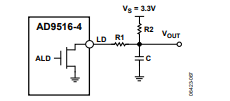

模擬鎖檢測(ALD)

AD9516提供ALD功能,可用于LD引腳。ALD有以下兩種版本:

- N溝道開漏鎖檢測 :此信號需上拉電阻以提供邏輯電平。輸出通常為高電平,低電平脈沖表示鎖定,鎖定由高電平脈沖的最小占空比指示。

- P溝道開漏鎖檢測 :此信號需下拉電阻至GND。輸出通常為低電平,高電平脈沖表示鎖定,鎖定由高電平脈沖的最小占空比指示。

模擬鎖檢測功能需一個R - C濾波器,以提供指示鎖定/解鎖的邏輯電平。

圖50. 使用N溝道開漏驅動器的模擬鎖檢測濾波器示例

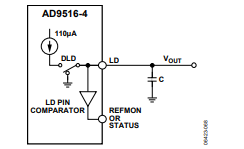

電流源數字鎖檢測(DLD)

在PLL鎖定序列期間,DLD信號通常會多次翻轉,在PLL完全鎖定并穩定后保持穩定。可能存在一些應用場景,需要在PLL牢固鎖定后禁用DLD。這可通過電流源鎖檢測功能實現。當從LD引腳控制選擇為輸出時(寄存器0x01A[5:0]),該功能可用。

當DLD為真時,電流源鎖檢測提供110 μA的電流;當DLD為假時,它短路到地。如果將電容連接到LD引腳,電容在DLD為真時以由電流源確定的速率充電,但在DLD為假時幾乎瞬間放電。通過監測LD引腳(電容頂部)的電壓,在DLD變為真后,可使邏輯高電平引腳僅在短暫的時間內保持高電平。任何瞬間的DLD假信號都會充分重置電容。通過選擇合適尺寸的電容,可以延遲鎖檢測指示,直到PLL穩定鎖定,且鎖檢測不會抖動。

電容上的電壓可由連接到LD引腳的外部比較器檢測。不過,AD9516有一個內部LD引腳比較器,可在REFMON引腳控制(寄存器0x01B[4:0])或STATUS引腳控制(寄存器0x017[7:2])下作為有源高信號讀取。它也可作為有源低信號在REFMON(寄存器0x01B[4:0])和STATUS(寄存器0x017[7:2])中使用。內部LD引腳比較器的觸發點和滯后見表16。

圖51. 電流源鎖檢測

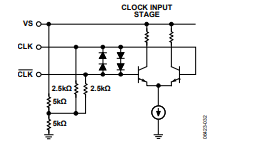

外部VCXO/VCO時鐘輸入(CLK/{CLK}})

CLK是一個差分輸入,可用于驅動AD9516時鐘分配部分。此輸入可接收高達2.4 GHz的信號。內部自偏置,輸入信號應通過電容交流耦合。

圖52. CLK等效輸入電路

CLK/CLK}}**輸入既可用作僅分配輸入(帶PLL關閉),也可用作外部VCO/VCXO的反饋輸入,通過內部PLL使用,此時內部VCO不使用。CLK/**CLK}}$輸入可用于高達2.4 GHz的頻率。

-

pll

+關注

關注

6文章

889瀏覽量

136455 -

時鐘

+關注

關注

11文章

1901瀏覽量

133253 -

VCO

+關注

關注

13文章

311瀏覽量

70231 -

AD9516

+關注

關注

0文章

12瀏覽量

8073

發布評論請先 登錄

AD9516-4 14路輸出時鐘發生器,集成1.6 GHz VCO

AD9520-0:12路LVPECL/24路CMOS輸出時鐘發生器,集成2.8 GHz VCO

AD9516-4 14路輸出時鐘發生器,集成1.6GHz VCO技術手冊

AD9516-4 14路輸出時鐘發生器,集成1.6GHz VCO技術手冊

評論