文章來(lái)源:學(xué)習(xí)那些事

原文作者:趙先生

本文介紹了芯片的堆疊與堆疊產(chǎn)生的應(yīng)力問(wèn)題。

多芯片堆疊

多芯片堆疊技術(shù)的出現(xiàn),順應(yīng)了器件朝著小型化、集成化方向發(fā)展的趨勢(shì)。該技術(shù)與先進(jìn)封裝領(lǐng)域中的系統(tǒng)級(jí)封裝(SIP)存在一定差異。先進(jìn)封裝涵蓋多種前沿工藝技術(shù),如重布線層(RDL)、硅通孔(TSV)、金屬凸點(diǎn)(Bump)以及晶圓級(jí)封裝(WLP)等。晶圓級(jí)封裝已突破傳統(tǒng)封裝在劃片、粘片、鍵合和密封等方面的工藝范疇,像芯片再布線、凸點(diǎn)生長(zhǎng)與倒裝焊接,芯片通孔、疊層與互連,乃至扇出型晶圓級(jí)封裝(FOWLP)、扇入型晶圓級(jí)封裝(FIWLP),均屬于廣義上的封裝概念。部分中道線工藝在一些工廠雖被歸為后道工序,但相較于后道封裝工藝,其與前道晶圓制造工藝的聯(lián)系更為緊密。

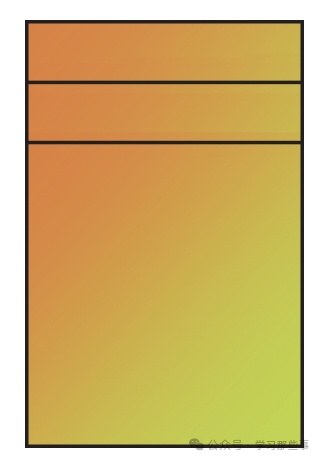

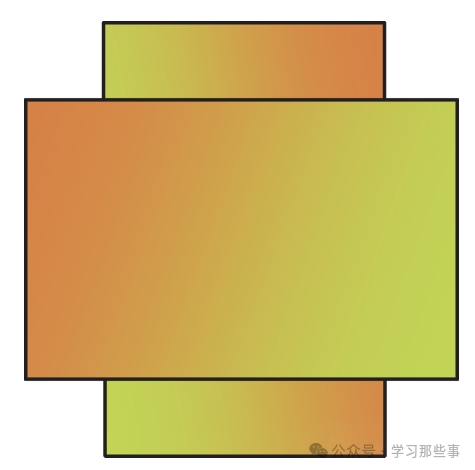

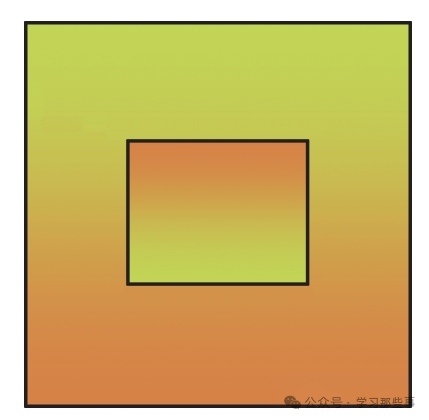

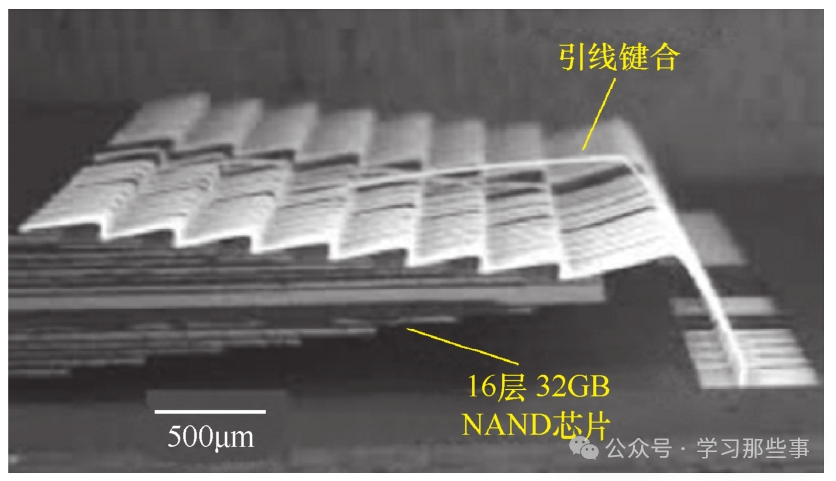

多芯片堆疊所構(gòu)建的器件,同樣屬于SIP。不過(guò),其采用的是傳統(tǒng)的芯片粘接和引線鍵合工藝,因此本質(zhì)上屬于傳統(tǒng)封裝類型。芯片的疊層粘接能夠大幅節(jié)省空間,但在操作過(guò)程中,需確保下層芯片的管腳(Pad)點(diǎn)不會(huì)被上層芯片或粘接劑覆蓋,以免對(duì)后續(xù)的引線鍵合工序造成影響。多芯片堆疊的形式主要由芯片的大小、形狀以及管腳點(diǎn)的分布決定,常見(jiàn)的堆疊形式如圖1-圖3所示。

圖1 多芯片的錯(cuò)層堆疊

圖2 多芯片的交叉堆疊

圖3 多芯片的金字塔堆疊

多層芯片堆疊應(yīng)力集中

在多層芯片堆疊過(guò)程中,由于芯片正面設(shè)有鈍化層,無(wú)法采用合金燒結(jié)的方式進(jìn)行芯片間的堆疊,一般會(huì)選用膠黏劑來(lái)實(shí)現(xiàn)粘接。具體的粘接工藝流程為,首先將最下層芯片進(jìn)行粘接;接著在最下層芯片表面涂抹膠黏劑,隨后粘接上層芯片,依此方式逐層疊加粘接。研究顯示,由于膠黏劑與硅芯片的熱膨脹系數(shù)存在差異,多層芯片之間會(huì)產(chǎn)生較大應(yīng)力。

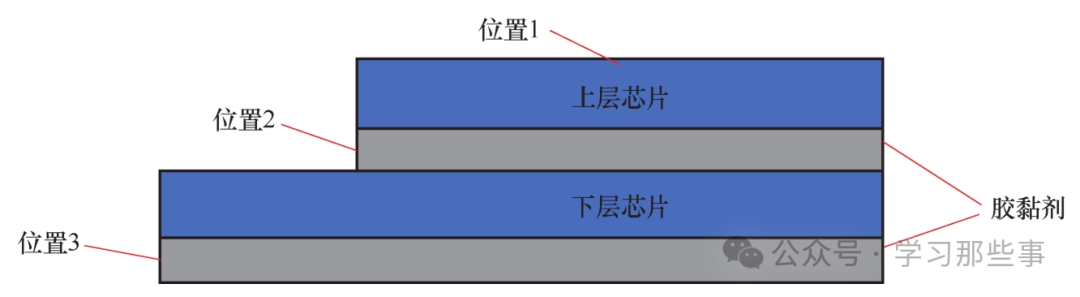

有研究人員針對(duì)塑封的多層芯片堆疊器件開(kāi)展建模仿真,識(shí)別出應(yīng)力集中的三種主要形式,如圖4所示。

圖4多層堆疊粘片主要失效位置

多層芯片堆疊應(yīng)力集中產(chǎn)生的失效形式:

芯片與環(huán)氧塑封料分層:上層芯片與環(huán)氧塑封料之間會(huì)產(chǎn)生應(yīng)力,這一應(yīng)力致使芯片與塑封料界面處出現(xiàn)分層現(xiàn)象。

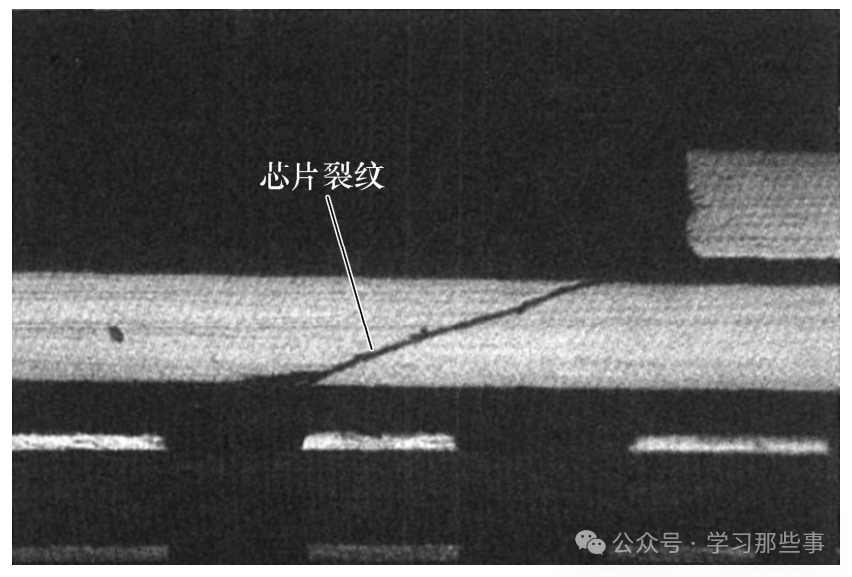

下層芯片損傷:上下層芯片間的應(yīng)力會(huì)在上層芯片的邊角位置高度集中。這種集中應(yīng)力往往會(huì)導(dǎo)致下層芯片出現(xiàn)裂紋,嚴(yán)重時(shí)甚至造成芯片斷裂,對(duì)器件造成致命性破壞,具體可參考圖5。

圖5下層芯片裂紋

芯片與膠黏劑整體和環(huán)氧塑封料分層:下層芯片邊緣與環(huán)氧塑封料之間存在應(yīng)力,這種應(yīng)力會(huì)使芯片和膠黏劑構(gòu)成的整體,與環(huán)氧塑封料之間發(fā)生分層。

研究表明,上述應(yīng)力的大小,與材料的熱膨脹系數(shù)、芯片厚度等關(guān)鍵參數(shù)緊密相關(guān)。

芯片的裂紋

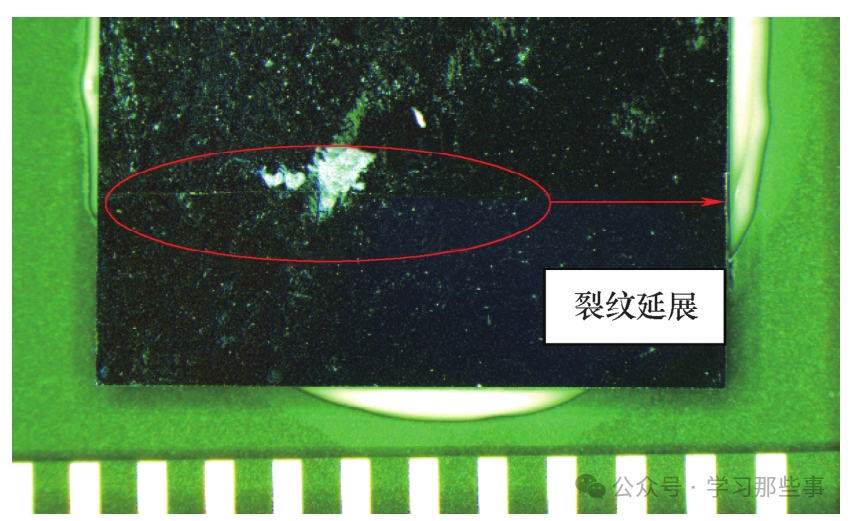

為了通過(guò)目檢清晰觀察膠黏劑從芯片四周溢出的輪廓,通常會(huì)在芯片下方懸空部位填充不導(dǎo)電膠。研究人員將硅片切割成與待封裝芯片相同尺寸,并分別堆疊至兩層、三層、四層,隨后開(kāi)展 -55℃至125℃的溫度循環(huán)試驗(yàn)。試驗(yàn)結(jié)果顯示,填充不導(dǎo)電膠的電路出現(xiàn)了熱失配問(wèn)題。在溫度循環(huán)試驗(yàn)結(jié)束后,上層芯片均出現(xiàn)了不同程度的裂紋,裂紋首先沿底層芯片邊緣位置擴(kuò)展,最終有可能貫穿整個(gè)芯片,具體現(xiàn)象如圖6所示。

仿真結(jié)果表明,使用不導(dǎo)電膠填充的模型,其最大應(yīng)力位置與實(shí)際觀察到的上層芯片裂紋位置一致,均出現(xiàn)在上層芯片、填充的不導(dǎo)電膠、下層芯片邊緣三者的交接面上。而未使用不導(dǎo)電膠填充的模型,上層芯片的最大應(yīng)變相較于使用不導(dǎo)電膠填充的模型,降低了91.7%。由此可見(jiàn),硅芯片與膠黏劑之間匹配性的差異,是引發(fā)芯片裂紋的主要原因。這些裂紋在溫度循環(huán)等可靠性試驗(yàn)過(guò)程中,會(huì)進(jìn)一步擴(kuò)展,嚴(yán)重時(shí)可導(dǎo)致芯片斷裂。底部無(wú)填充的堆疊芯片情況,如圖7所示。

圖6堆疊粘片的裂紋

圖7無(wú)填充的堆疊芯片

爬膠與膠膜

在傳統(tǒng)封裝工藝?yán)铮酒辰悠毡椴捎弥苯油磕▽?dǎo)熱膠的方式。這種導(dǎo)熱膠不僅使用便捷,而且能提供足夠的粘接強(qiáng)度。然而,在多層堆疊芯片的場(chǎng)景下,芯片通常會(huì)被減薄至很薄的尺寸,部分芯片厚度甚至達(dá)到100μm。當(dāng)使用常規(guī)導(dǎo)熱膠進(jìn)行這類超薄芯片間的粘接時(shí),爬膠問(wèn)題頻繁出現(xiàn)。爬膠會(huì)致使部分導(dǎo)熱膠溢出到芯片表面,污染管腳(Pad)點(diǎn),進(jìn)而對(duì)后續(xù)的鍵合工序造成嚴(yán)重影響。

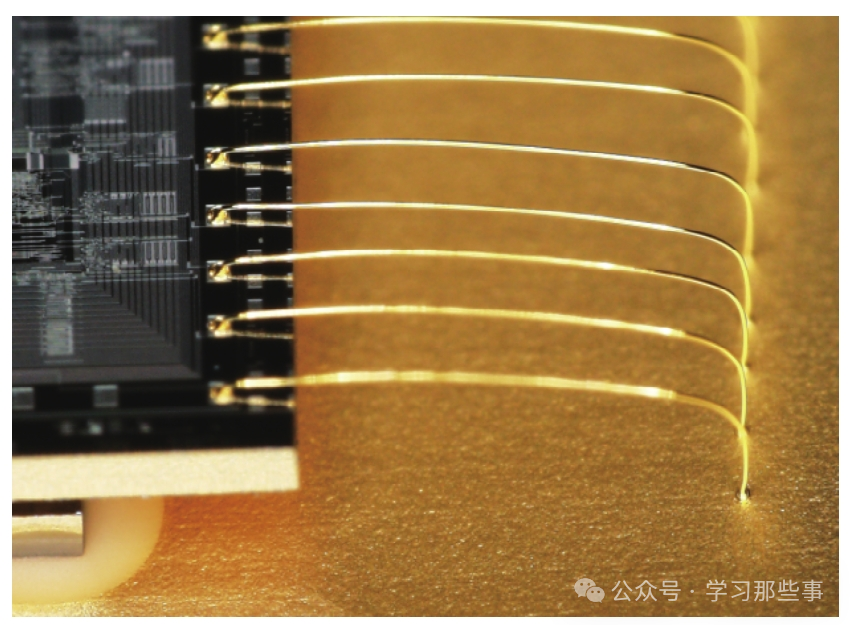

為解決這一難題,材料供應(yīng)商研發(fā)出導(dǎo)熱膠膜,以此替代傳統(tǒng)導(dǎo)熱膠。導(dǎo)熱膠膜具有固定的厚度,借助這一特性,能夠有效控制膠量和粘接厚度,從而避免爬膠現(xiàn)象的發(fā)生。不僅如此,導(dǎo)熱膠膜還能在高度設(shè)計(jì)方面提供更大的靈活性。從實(shí)際應(yīng)用來(lái)看,在民用產(chǎn)品領(lǐng)域,部分多層堆疊結(jié)構(gòu)已經(jīng)實(shí)現(xiàn)了百余層的堆疊。圖8展示了一種存儲(chǔ)器芯片的堆疊示意圖。

圖8一種存儲(chǔ)器芯片的堆疊示意圖

-

芯片

+關(guān)注

關(guān)注

459文章

52256瀏覽量

437140 -

晶圓

+關(guān)注

關(guān)注

52文章

5130瀏覽量

129246 -

封裝

+關(guān)注

關(guān)注

128文章

8566瀏覽量

144901 -

堆疊

+關(guān)注

關(guān)注

0文章

37瀏覽量

16827

原文標(biāo)題:芯片的堆疊與堆疊產(chǎn)生的應(yīng)力問(wèn)題

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

華為公布芯片堆疊專利,能否解缺芯燃眉之急

一文詳解多芯片組件MCM技術(shù)

請(qǐng)問(wèn)Ultrascale FPGA中單片和下一代堆疊硅互連技術(shù)是什么意思?

芯片堆疊的主要形式

一文讀懂交換機(jī)堆疊技術(shù)

華為又一專利公開(kāi),芯片堆疊技術(shù)持續(xù)進(jìn)步

華為公布兩項(xiàng)芯片堆疊相關(guān)專利

一文解析多芯片堆疊封裝技術(shù)(上)

一文解析芯片堆疊封裝技術(shù)

一文解析多芯片封裝技術(shù)

一文詳解多芯片堆疊技術(shù)

一文詳解多芯片堆疊技術(shù)

評(píng)論