概述

AD9512提供多路輸出時(shí)鐘分配功能,輸入信號(hào)最高可達(dá)1.6 GHz。它具有低抖動(dòng)和低相位噪聲特性,能夠極大地提升數(shù)據(jù)轉(zhuǎn)換器的時(shí)鐘性能。

數(shù)據(jù)表:*附件:AD9512 1.2 GHz時(shí)鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調(diào)整、5路輸出技術(shù)手冊(cè).pdf

3路獨(dú)立的LVPECL時(shí)鐘輸出和2路LVDS時(shí)鐘輸出工作頻率分別為1.2 GHz和800 MHz。可選的CMOS時(shí)鐘輸出工作頻率為250 MHz。每路輸出都有一個(gè)可編程分頻器,可以旁路該分頻器或者設(shè)置最高32的整數(shù)分頻比。

用戶可以通過各分頻器改變一路時(shí)鐘輸出相對(duì)于其它時(shí)鐘輸出的相位,這種相位選擇功能可用于時(shí)序粗調(diào)。1路輸出還提供可編程延遲特性,具有最長10 ns的用戶可選滿量程延遲值。該精調(diào)延遲模塊通過一個(gè)5位字進(jìn)行編程,提供32個(gè)可用的延遲時(shí)間供用戶選擇。

AD9512非常適合數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘應(yīng)用,利用亞皮秒抖動(dòng)編碼信號(hào),可實(shí)現(xiàn)優(yōu)質(zhì)的轉(zhuǎn)換器性能。

AD9512提供48引腳LFCSP封裝,額定溫度范圍為-40°C至+85°C,可以采用3.3 V單電源供電。

應(yīng)用

- 低抖動(dòng)、低相位噪聲時(shí)鐘分配

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE?轉(zhuǎn)換器提供時(shí)鐘

- 無線基礎(chǔ)設(shè)施收發(fā)器

- 高性能儀器儀表

- 寬帶基礎(chǔ)設(shè)施

特性

- 兩路1.6 GHz差分時(shí)鐘輸入

- 5個(gè)可編程分頻器,1至32整數(shù)分頻比

- 用于輸出到輸出延遲粗調(diào)的相位選擇

- 3路獨(dú)立的1.2 GHz LVPECL輸出

加性輸出抖動(dòng):225 fs均方根值 - 2路獨(dú)立的800 MHz/250 MHz LVDS/CMOS輸出

加性輸出抖動(dòng):275 fs均方根值

1路輸出提供延遲精調(diào),5位延遲字 - 4線式或3線式串行控制端口

- 節(jié)省空間的48引腳LFCSP封裝

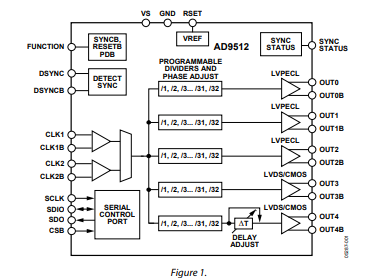

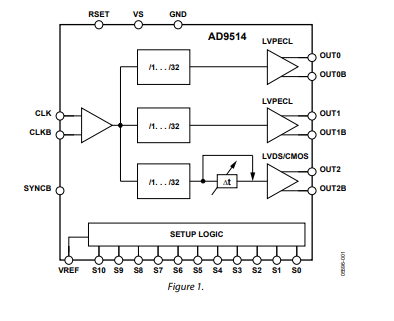

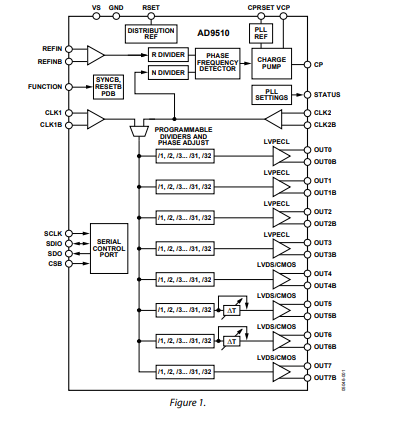

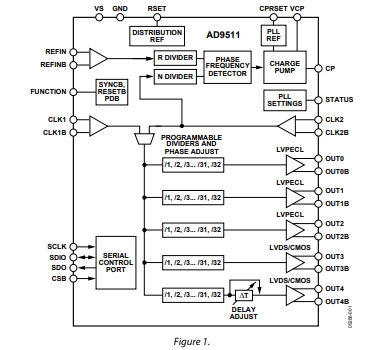

框圖

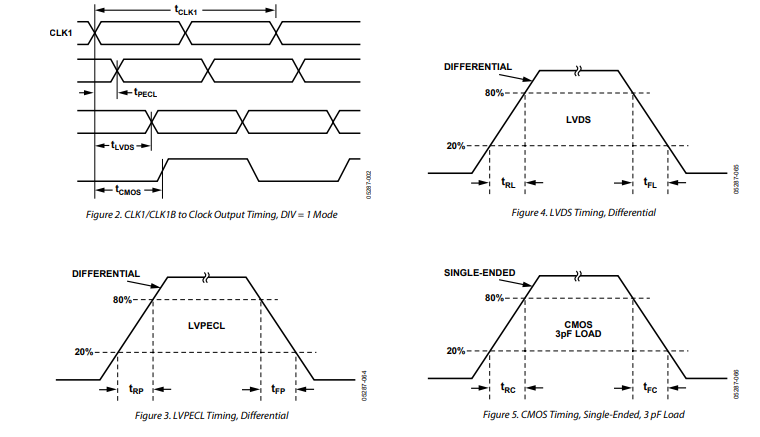

時(shí)序圖

引腳配置描述

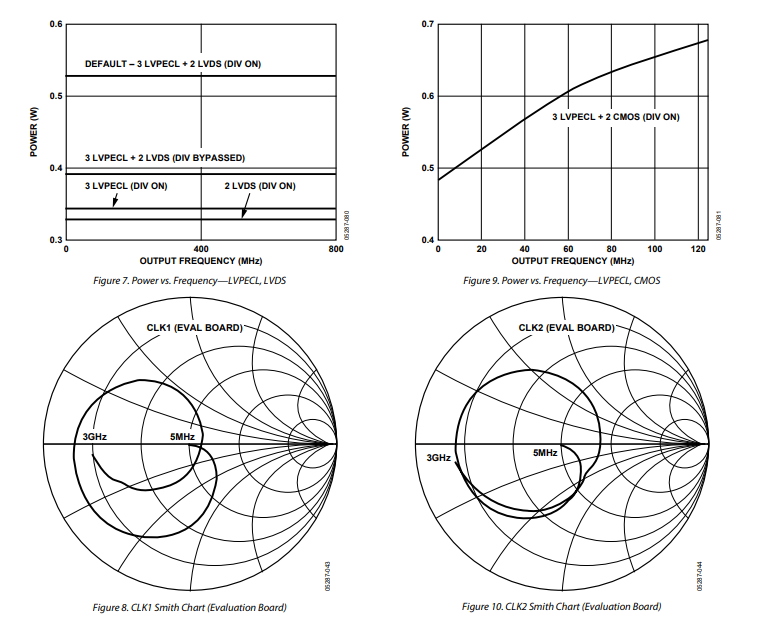

典型性能特征

功能描述

總體

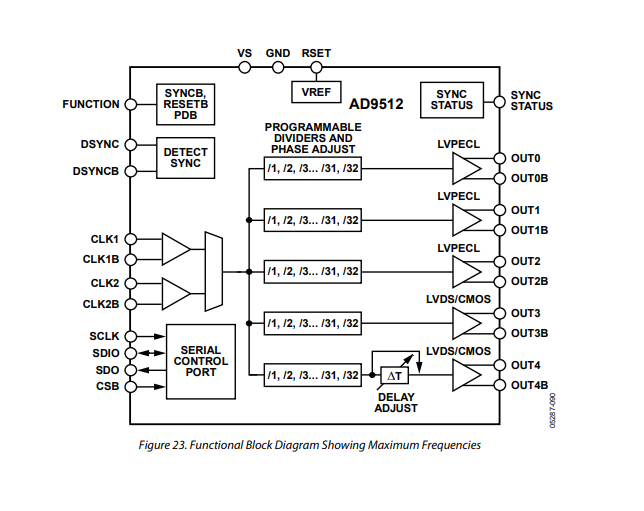

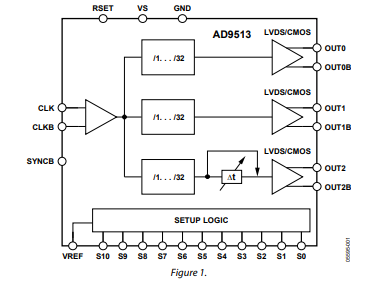

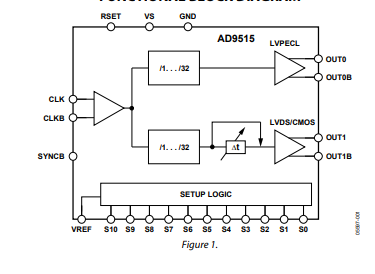

圖 23 展示了 AD9512 的框圖。AD9512 接受兩個(gè)時(shí)鐘輸入(CLK1 或 CLK2)中的任意一個(gè)。該時(shí)鐘可被除以 1 到 32 之間的任意整數(shù)值。輸出的占空比和相對(duì)相位可進(jìn)行調(diào)整。

有三個(gè) LVPECL 輸出(OUT0、OUT1、OUT2)和兩個(gè)可設(shè)置為 LVDS 或 CMOS 邏輯電平的輸出(OUT3、OUT4)。OUT4 也可使用可變延遲模塊。

AD9512 僅提供時(shí)鐘分配功能,不存在時(shí)鐘倍頻。輸入時(shí)鐘信號(hào)直接通過并可在輸出端占主導(dǎo)地位。

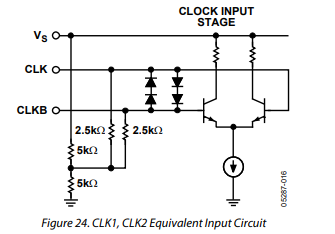

有關(guān) CLK1 和 CLK2 的等效電路,請(qǐng)參見圖 24。

功能引腳(引腳 12)有三種功能,通過寄存器 58h<6:5> 中的設(shè)置進(jìn)行選擇。此引腳上有一個(gè) 30 kΩ 的下拉電阻。

- RESETB:58h<6:5> = 00b(默認(rèn)) :在其默認(rèn)模式下,功能引腳充當(dāng) RESETB,拉低時(shí)會(huì)產(chǎn)生異步復(fù)位或硬復(fù)位。復(fù)位結(jié)果會(huì)將默認(rèn)值寫入串行控制端口緩沖寄存器,并使芯片控制寄存器恢復(fù)默認(rèn)值。AD9512 會(huì)立即按照默認(rèn)值恢復(fù)運(yùn)行。當(dāng)該引腳再次拉高時(shí),會(huì)發(fā)出異步 SYNC 信號(hào)(參見 SYNCB:58h<6:5> = 01b 部分)。

- SYNCB:58h<6:5> = 01b :功能引腳可用于使不同時(shí)鐘輸出之間實(shí)現(xiàn)同步或?qū)R相位。同步僅適用于以下時(shí)鐘輸出:

- 未斷電;

- 分頻器未被屏蔽(no_sync = 0);

- 未被旁路(bypass = 0)。

SYNCB 低電平有效。當(dāng) SYNCB 為低電平時(shí),所選輸出會(huì)進(jìn)入預(yù)設(shè)狀態(tài)。分頻器以預(yù)設(shè)的分頻值或快速時(shí)鐘(fast clock,由 CLK1 或 CLK2 中的選定時(shí)鐘輸入決定)開始計(jì)數(shù)。SYNCB 的應(yīng)用會(huì)影響分頻器相位引腳中的所有位。無論該引腳是否也被指定用于復(fù)位或斷電,只要 SYNCB 功能被選中,功能引腳就不會(huì)充當(dāng) RESETB 或 PDB。

- PDB:58h<6:5> = 11b :功能引腳也可被編程為全功率關(guān)閉。在此斷電模式下,仍有一些殘余電壓 V 存在。在 PDB 模式下,功能引腳為高電平有效。芯片在該引腳變?yōu)榈碗娖街耙恢北3值凸臓顟B(tài)。返回設(shè)置請(qǐng)參閱芯片斷電或睡眠模式 - PDB 部分,以了解有關(guān)功能引腳啟動(dòng)斷電時(shí)的更多詳細(xì)信息。

動(dòng)態(tài)同步引腳(DSYNC AND DSYNCB PINS)

DSYNC 和 DSYNCB 引腳(引腳 1 和引腳 2)用于 AD9512 在多路同步配置中(見多路同步部分)。

時(shí)鐘輸入(CLOCK INPUTS)

AD9512 有兩個(gè)時(shí)鐘輸入(CLK1、CLK2)可供使用。CLK2 和 CLK1 可接受高達(dá) 1600 MHz 的輸入頻率。圖 24 為 CLK2 和 CLK1 的等效電路。

時(shí)鐘輸入為全差分且自偏置。如果必須使用單端輸入,可通過在差分輸入的一側(cè)連接一個(gè)電容器來實(shí)現(xiàn)。另一側(cè)應(yīng)通過一個(gè)電容器旁路至安靜的交流地。

未選擇的時(shí)鐘輸入(無論是 CLK1 還是 CLK2)應(yīng)接地,以消除不需要的時(shí)鐘信號(hào)進(jìn)入選定時(shí)鐘輸入的任何可能性。

-

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1891瀏覽量

133001 -

數(shù)據(jù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

375瀏覽量

28887 -

ad9512

+關(guān)注

關(guān)注

0文章

3瀏覽量

1331

發(fā)布評(píng)論請(qǐng)先 登錄

ADI設(shè)計(jì)峰會(huì)講義分享:實(shí)現(xiàn)更高信號(hào)處理性能的高級(jí)技術(shù)

1.2千兆赫時(shí)鐘分配IC 1.6GHz輸入分頻器延遲調(diào)整五輸出ad9512數(shù)據(jù)表

AD9512 1.2 GHz時(shí)鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調(diào)整、5路輸出

AD9512: 1.2 GHz Clock Distribution IC, 1.6 GHz Inputs, Dividers, Delay Adjust, Five Outputs Data Sheet

AD9510:1.2 GHz時(shí)鐘分配IC,PLL內(nèi)核,分頻器,延遲調(diào)整,8路輸出

AD9508:1.65 GHz時(shí)鐘扇出緩沖器,集成輸出分頻器和延遲調(diào)整

AD9512:1.2 GHz時(shí)鐘分配IC,1.6 GHz輸入,分頻器,延遲調(diào)整,五輸出數(shù)據(jù)表

AD9515:1.6 GHz時(shí)鐘分配IC、分頻器、延遲調(diào)整、雙輸出數(shù)據(jù)表

AD9515 1.6 GHz時(shí)鐘分配IC,分頻器,延遲調(diào)整,雙輸出數(shù)據(jù)表

AD9513 800MHz時(shí)鐘分配IC,分頻器,延遲調(diào)整,三路輸出技術(shù)手冊(cè)

AD9515 1.6GHz時(shí)鐘分配IC,分頻器,延遲調(diào)整,兩路輸出技術(shù)手冊(cè)

AD9514 1.6GHz時(shí)鐘分配IC、分頻器、延遲調(diào)整、3路輸出技術(shù)手冊(cè)

AD9510 1.2 GHz時(shí)鐘分配IC,PLL內(nèi)核,分頻器,延遲調(diào)整,8路輸出技術(shù)手冊(cè)

AD9511 1.2 GHz時(shí)鐘分配IC,PLL內(nèi)核,分頻器,延遲調(diào)整,5路輸出技術(shù)手冊(cè)

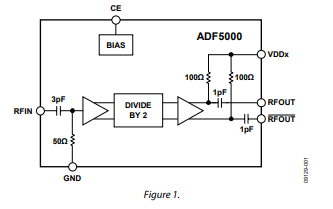

ADF5000 4GHz 至18GHz 2分頻預(yù)分頻器技術(shù)手冊(cè)

AD9512 1.2 GHz時(shí)鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調(diào)整、5路輸出技術(shù)手冊(cè)

AD9512 1.2 GHz時(shí)鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調(diào)整、5路輸出技術(shù)手冊(cè)

評(píng)論