概述

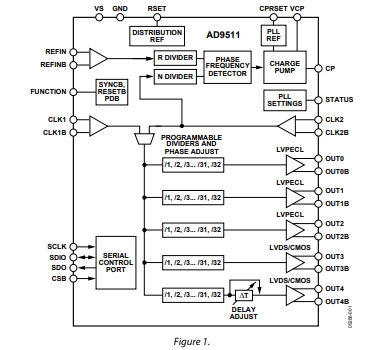

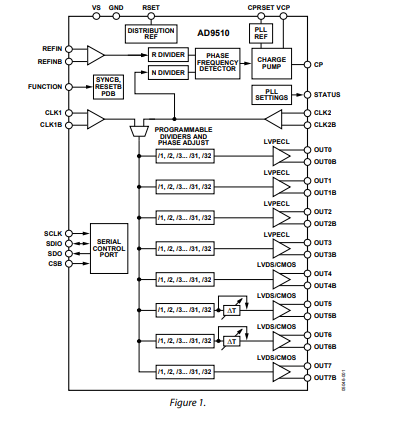

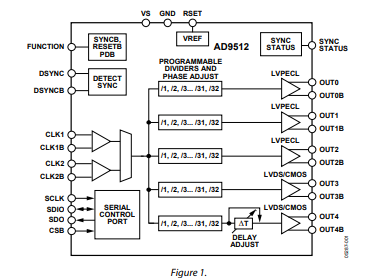

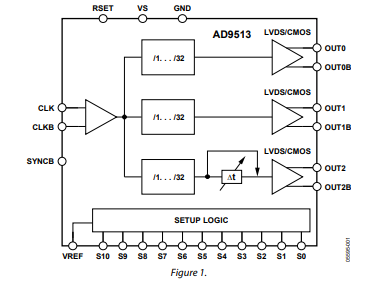

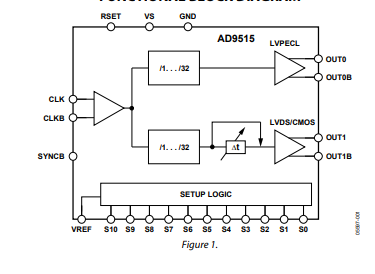

AD9511提供多路輸出時鐘分配功能,并集成一個片內鎖相環(PLL)內核。它具有低抖動和低相位噪聲特性,能夠極大地提升數據轉換器的時鐘性能。3路獨立的LVPECL時鐘輸出和2路LVDS時鐘輸出工作頻率分別為1.2 GHz和800 MHz。可選的CMOS時鐘輸出工作頻率為250 MHz。

數據表:*附件:AD9511 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,5路輸出技術手冊.pdf

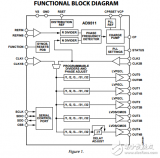

PLL部分由可編程參考分頻器(R)、低噪聲鑒頻鑒相器(PFD)、精密電荷泵(CP)和可編程反饋分頻器(N)組成。將外部VCXO或VCO連接到CLK2和CLK2B引腳時,最高達1.6 GHz的PLL輸出頻率可以與輸入參考REFIN同步。

時鐘分配部分提供LVPECL輸出和可編程為LVDS或CMOS的輸出。每路輸出都有一個可編程分頻器,可以旁路該分頻器或者設置最高32的整數分頻比。

用戶可以通過各分頻器改變一路時鐘輸出相對于其它時鐘輸出的相位,這種相位選擇功能可用于時序粗調。一路輸出還提供可編程延遲特性,具有最長10 ns的用戶可選滿量程延遲值。該精調延遲模塊通過一個5位字進行編程,提供32個可用的延遲時間供用戶選擇。

AD9511非常適合數據轉換器時鐘應用,利用亞皮秒抖動編碼信號,可實現優質的轉換器性能。

AD9511提供48引腳LFCSP封裝,額定溫度范圍為-40°C至+85°C,可以采用3.3 V單電源供電。如果用戶希望擴展外部VCO的電壓范圍,可以利用最高達5.5V的電荷泵電源VCP。

應用

特性

- 低相位噪聲鎖相環內核

- 最高250 MHz的參考輸入頻率

- 可編程雙模預分頻器

- 可編程電荷泵(CP)電流

- 獨立的CP電源(VCP)可擴展調整范圍

- 兩路1.6 GHz差分時鐘輸入

- 5個可編程分頻器,1至32整數分頻比

- 用于輸出到輸出延遲粗調的相位選擇

- 3路獨立的1.2 GHz LVPECL輸出

- 加性輸出抖動:225 fs RMS

- 2路獨立的800 MHz/250 MHz LVDS/CMOS輸出

- 加性輸出抖動:275 fs RMS

- 一路輸出提供延遲精調,5位延遲字

- 串行控制端口

- 節省空間的48引腳LFCSP封裝

框圖

時序圖

引腳配置

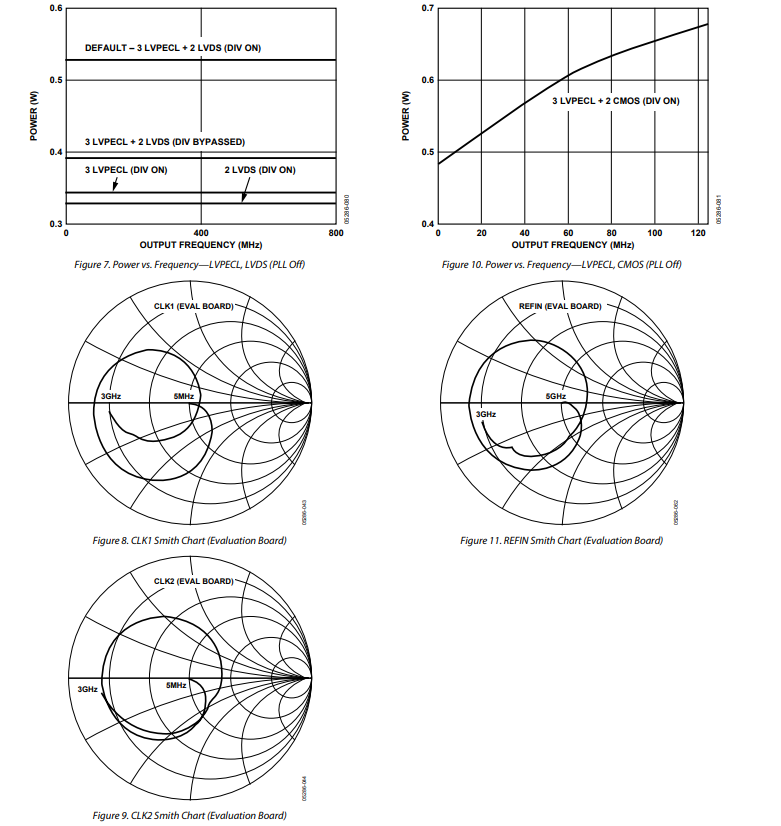

典型性能特征

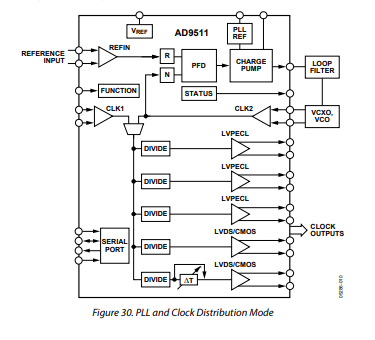

典型工作模式

帶外部壓控晶體振蕩器/壓控振蕩器(VCXO/VCO)并隨后進行時鐘分配的鎖相環(PLL)模式

這是 AD9511 最常見的工作模式。一個外部振蕩器(如圖所示的 VCO/VCXO)與參考輸入(REFIN)進行鎖相。鎖相環濾波器通常為無源設計。可以使用 VCO 或 VCXO 。CLK2 輸入是一個內部反饋路徑。CLK2 輸入為 PLL 提供反饋路徑。如果 VCO/VCXO 頻率超過輸出頻率的最大值,則必須使用相應的分頻器(s)。在分配部分中設置分頻比。通過關閉未使用的功能以及關閉任何未使用的時鐘通道,也可以節省一些功率(請參閱寄存器映射說明部分)。

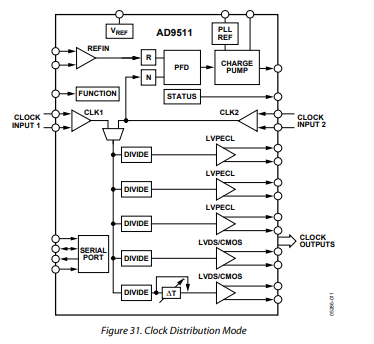

僅時鐘分配模式

只要不需要 PLL 部分,就可以僅使用分配部分。這樣也可以節省功率,方法是關閉 PLL 模塊,以及關閉任何未使用的時鐘通道(請參閱寄存器映射說明部分)。

在分配模式下,CLK1 和 CLK2 輸入均可通過低抖動多路復用器(mux)分配到輸出端。

-

pll

+關注

關注

6文章

887瀏覽量

136148 -

時鐘

+關注

關注

11文章

1887瀏覽量

132933 -

lvds

+關注

關注

2文章

1118瀏覽量

67191 -

AD9511

+關注

關注

0文章

3瀏覽量

6790

發布評論請先 登錄

1.2千兆赫時鐘分配IC鎖相環核心分頻器延遲調整五輸出ad9511數據表

AD9511 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,5路輸出

AD9511: 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs Data Sheet

AD9512:1.2 GHz時鐘分配IC,1.6 GHz輸入,分頻器,延遲調整,五輸出數據表

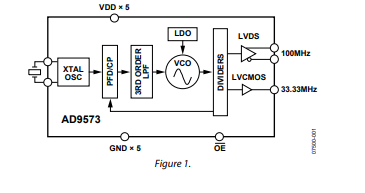

AD9573:PCI-Express時鐘發生器IC,PLL內核,分頻器,雙輸出數據表

AD9573 PCI-Express時鐘發生器IC,PLL內核,分頻器,兩路輸出技術手冊

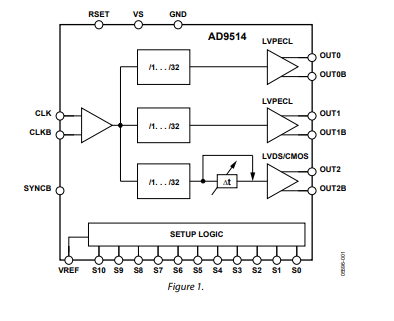

AD9514 1.6GHz時鐘分配IC、分頻器、延遲調整、3路輸出技術手冊

AD9510 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出技術手冊

AD9512 1.2 GHz時鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調整、5路輸出技術手冊

AD9511 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,5路輸出技術手冊

AD9511 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,5路輸出技術手冊

評論