本文翻譯轉載于:Cadence Blog

作者:MBhatnagar

我們很高興能在此宣布,Cadence 基于 UCIe標準封裝 IP 已在 Samsung Foundry 的 5nm 汽車工藝上實現首次流片成功。這一里程碑彰顯了我們持續提供高性能車規級 IP 解決方案?的承諾,可滿足新一代汽車電子和高性能計算應用的嚴格要求。

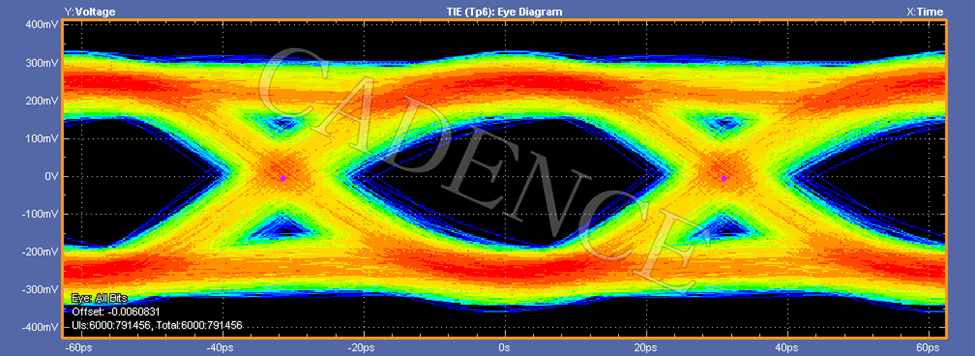

Cadence 的 UCle IP 在 16GT/s 的最高速率及所有支持的更低速率下均實現全功能運行,其眼圖質量和誤碼率(BER)遠優于規范要求。該性能驗證了設計的穩健性與可靠性,可無縫集成至對能效和可靠性要求嚴格的汽車電子和數據中心應用場景中。

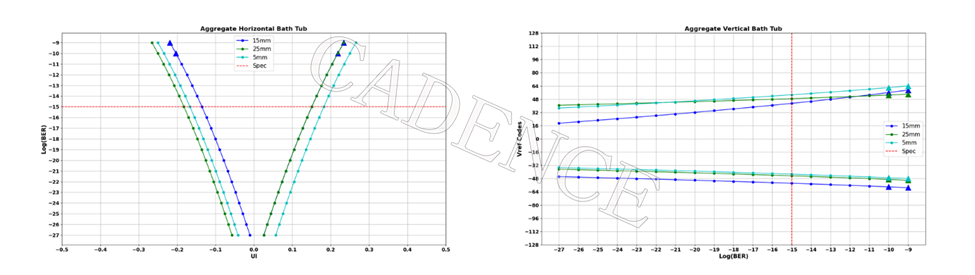

圖 1:速度為 16GT/s 時,在所有信道長度下提供卓越的性能,遠遠超出 UCIe 規范要求

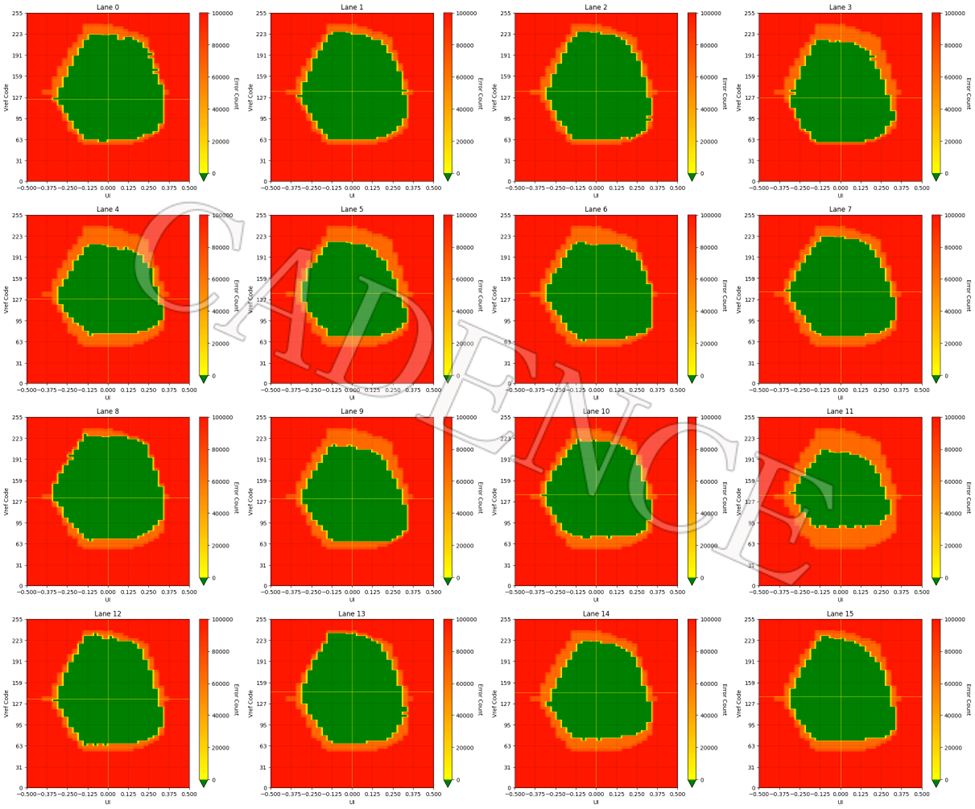

在圖 1 的浴盆曲線中,相位插值器(圖 1 左圖)和 Vref(圖 1 右圖)在 1e-15 規范要求下的眼圖性能(如紅色虛線所示)表明,在短、中、最大的裸片間距下,它們都表現出卓越的接收器性能。圖 2 顯示了使用 PRBS 檢查器測量的接收器眼圖,PRBS 模式在 UCIe 信道上以最大速度持續傳輸。基于硬件的成功啟動及訓練流程使得所有通道均呈現完全打開的眼圖。

圖 2:對于 16GT/s 下的 PRBS 模式,所有通道顯示良好的接收眼圖。

PHY 支持 16 Tx 和 16 Rx 標準封裝的全雙工通信互聯,最大距離為 25mm。我們已經在各種距離和布線方法的條件下進行了廣泛的測試,以驗證其性能。我們的 PHY 可在 Samsung 的 5nm 汽車工藝上實現,符合 UCIe 規范和嚴格的汽車行業要求。在對于 HPC/AI/ML 應用至關重要的多芯粒設計中,PHY 可在芯粒之間提供低功耗、低延遲的無縫通信,因此可以支持高性能計算(HPC)應用。

圖 3:Cadence 是 UCle 的核心成員之一,致力于協助制定包括汽車領域在內的技術規范

我們提供各種配置的 UCIe 控制器產品組合作為 PHY 的補充。從原始流接口到全 PCIe 協議以及輕量級、高效率的 AXI、CXS.B 和 CHI-C2C 接口,Cadence 都能提供支持。我們的控制器產品組合具有多種配置,包括 UCIe-CXS 和 UCIe-AXI,已獲得 SGS 的 ASIL-B 車規認證。在交付之前,控制器和 PHY 可無縫合并到 IP 子系統中,并在各級別進行廣泛的驗證,提供輕松的集成體驗,讓客戶可以專注于 SoC 差異化設計。

我們很高興能與 Samsung Foundry 持續合作,為雙方的共同客戶提供業界一流的 IP 解決方案,助力加速創新,將新一代汽車和高性能計算系統推向市場。

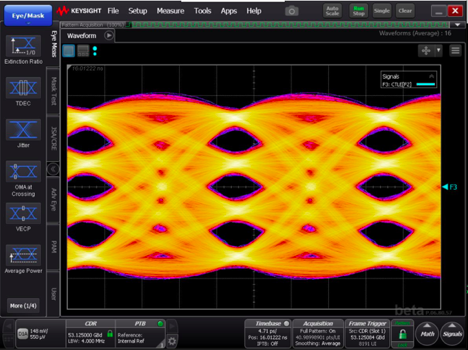

圖 4:示波器上顯示 16GT/s 下的 UCIe Tx 眼圖

我們將繼續推動拓寬互聯和系統性能的邊界,欲進一步了解 Cadence UCIe 產品更多信息,請點擊下方“閱讀原文”訪問。

-

控制器

+關注

關注

114文章

17049瀏覽量

183528 -

封裝

+關注

關注

128文章

8618瀏覽量

145116 -

工藝

+關注

關注

4文章

679瀏覽量

29343 -

Cadence

+關注

關注

67文章

968瀏覽量

144092 -

UCIe

+關注

關注

0文章

49瀏覽量

1821

原文標題:Cadence UCIe IP 在 Samsung Foundry 的 5nm 汽車工藝上實現流片成功

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Cadence 數字全流程解決方案通過三星5LPE工藝認證

Samsung Foundry成功部署全新Cadence解決方案

Cadence Voltus-XFi可用于Samsung Foundry的先進 5LPE 工藝技術

Cadence與Samsung Foundry合作認證面向 8nm 工藝技術的射頻集成電路設計參考流程

Cadence成功流片基于臺積電N3E工藝的16G UCIe先進封裝 IP

Cadence 與 Samsung Foundry 達成多年期協議以擴展其設計 IP 產品組合

Cadence Virtuoso Studio流程獲得Samsung Foundry認證,支持先進工藝技術的模擬IP自動遷移

Cadence數字和定制/模擬流程通過Samsung Foundry的SF2、SF3工藝技術認證

Cadence 推出經過認證的創新背面實現流程,以支持 Samsung Foundry SF2 技術

新思科技IP成功在臺積公司3nm工藝實現流片

Cadence EMX 3D Planar Solver 通過 Samsung Foundry 8nm LPP 工藝技術認證

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

評論