近日,核芯互聯(lián)正式推出新一代高性能時鐘抖動消除器——CLF7044。作為一款專為高速數(shù)據(jù)轉(zhuǎn)換與精密時鐘管理設(shè)計的核心器件,CLF7044在硬件架構(gòu)、封裝規(guī)格及關(guān)鍵性能指標上全面兼容行業(yè)標桿HMC7044,采用全國產(chǎn)化純CMOS工藝設(shè)計,為通信基站、微波基帶、波束成形、軟件定義無線電等領(lǐng)域提供了無縫替代方案,助力客戶在保持系統(tǒng)設(shè)計一致性的同時,實現(xiàn)性能升級與成本優(yōu)化。

一、全兼容設(shè)計:無縫銜接HMC7044生態(tài),降低遷移成本

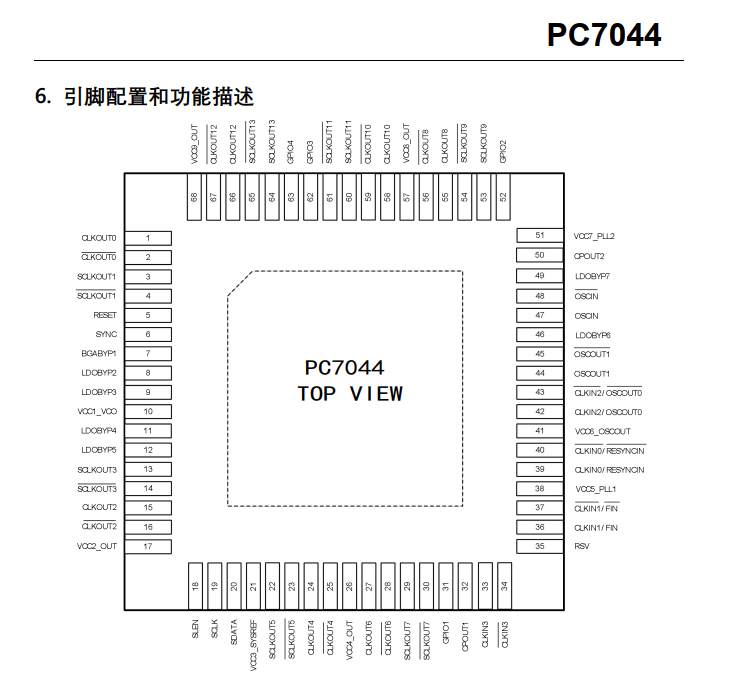

CLF7044采用與HMC7044完全一致的QFN68封裝及引腳定義,支持即插即用式替換,無需重新設(shè)計PCB布局。在硬件兼容性上,其輸入輸出接口全面適配LVDS、LVPECL、CML等多種標準,支持4路差分/單端時鐘輸入與14路可配置時鐘輸出,完美兼容現(xiàn)有HMC7044系統(tǒng)的外圍電路。

性能層面,CLF7044繼承了HMC7044的核心優(yōu)勢并實現(xiàn)突破:

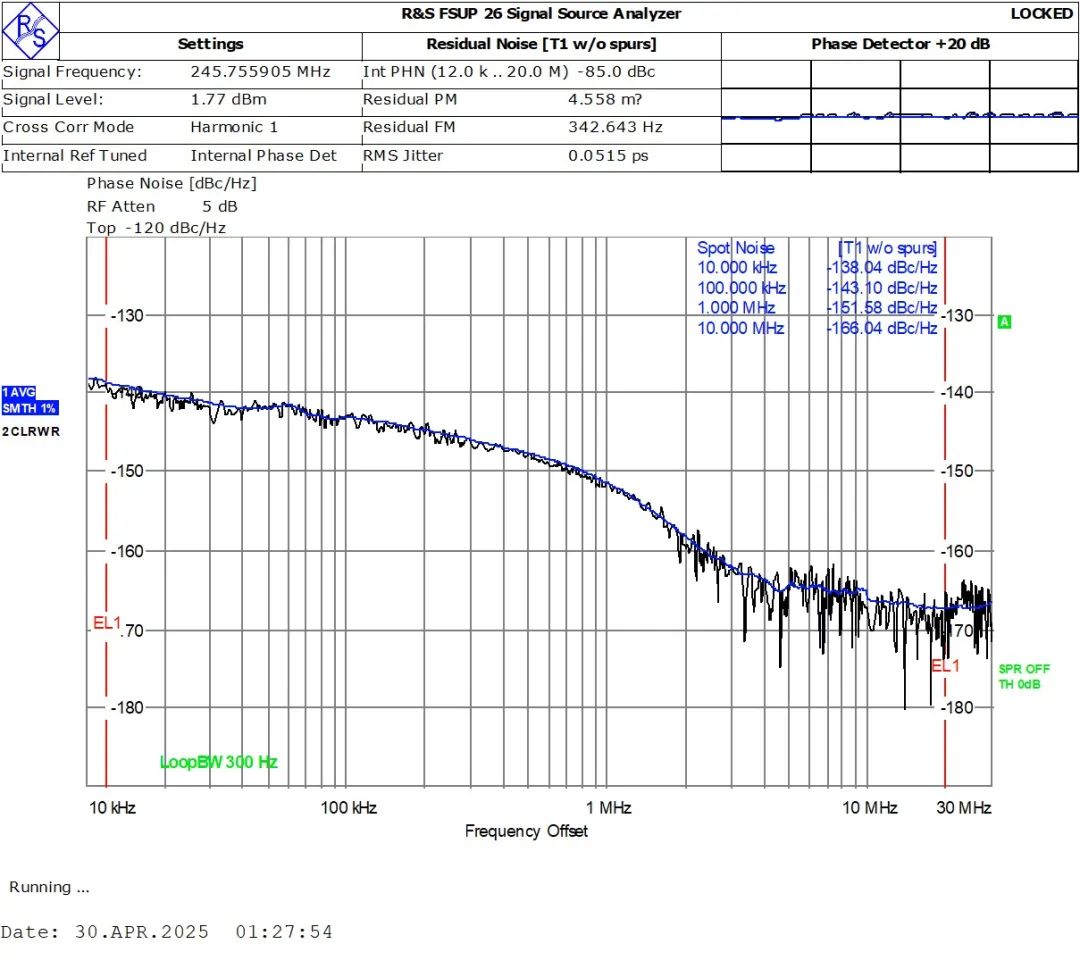

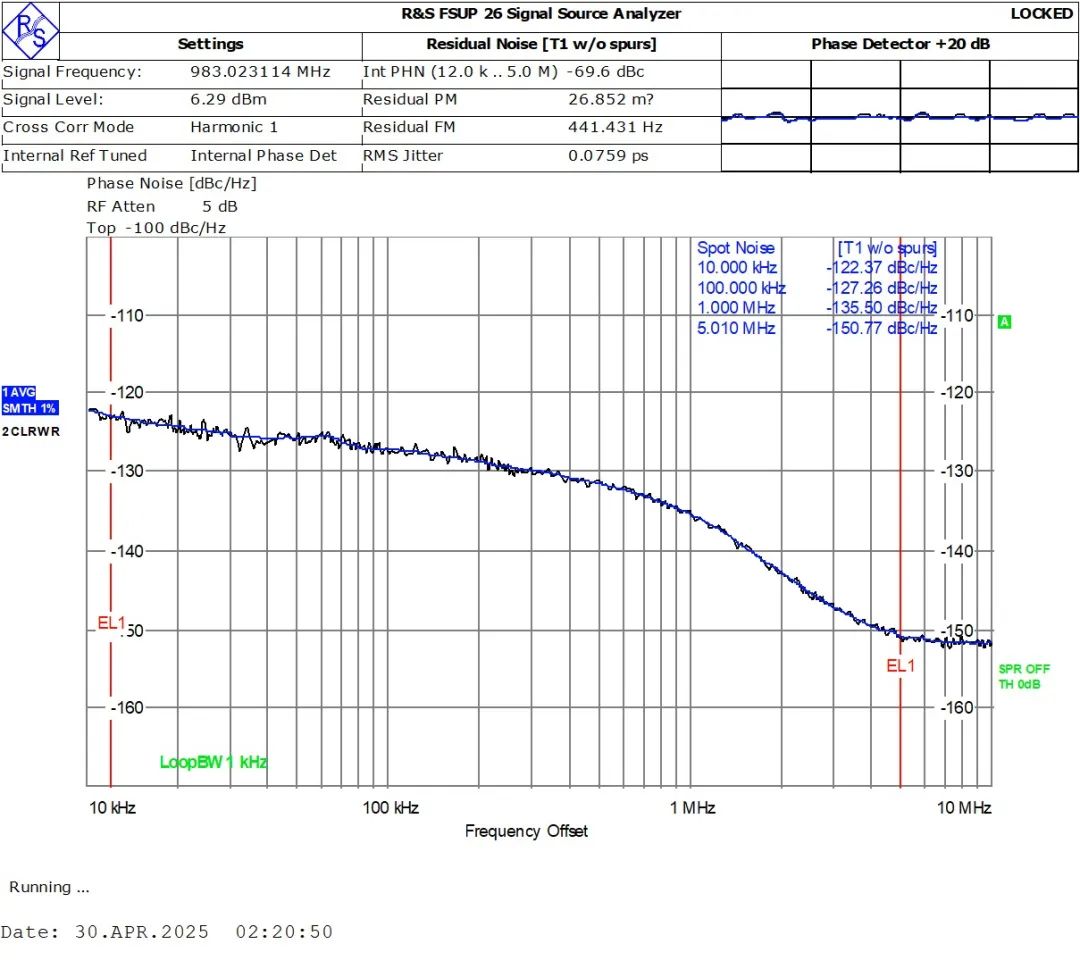

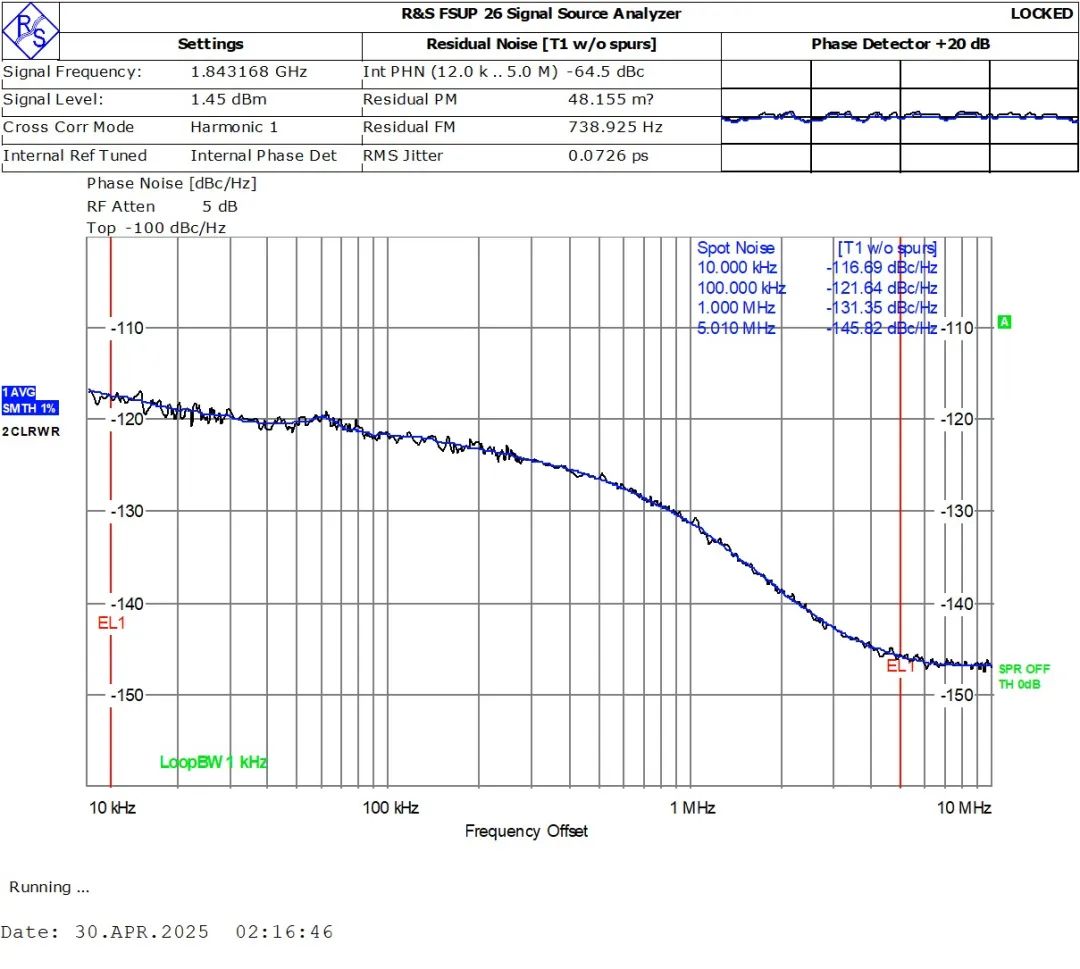

超低RMS抖動:在245.76 MHz頻率下,12kHz-20MHz帶寬內(nèi)抖動低至51.5fs RMS,滿足高精度數(shù)據(jù)轉(zhuǎn)換器對參考時鐘的嚴苛要求;

底噪性能:噪聲基底達-161dBc/Hz,有效抑制相位噪聲對信號鏈的干擾;

頻率范圍:支持最高3200MHz輸出頻率及寬范圍VCO調(diào)諧,適配多代通信協(xié)議的頻率需求。

對于正在使用HMC7044的客戶,CLF7044只需要略微調(diào)整原有驅(qū)動代碼與控制邏輯,即可通過SPI接口實現(xiàn)參數(shù)無縫遷移,大幅縮短產(chǎn)品迭代周期。

二、雙環(huán)路架構(gòu):重構(gòu)時鐘管理靈活性與穩(wěn)定性

CLF7044搭載雙整數(shù)模式PLL及重疊片上VCO,構(gòu)建了業(yè)界領(lǐng)先的時鐘處理架構(gòu):

雙環(huán)路協(xié)同優(yōu)化:PLL1支持外部VCXO或低成本晶振輸入,通過窄環(huán)路帶寬實現(xiàn)抖動消除;PLL2可獨立驅(qū)動14路輸出,支持JESD204B系統(tǒng)參考時鐘(SYSREF)脈沖生成,滿足多通道數(shù)據(jù)轉(zhuǎn)換器的同步需求。

智能延遲配置:每個輸出通道支持25ps模擬延遲與?VCO周期數(shù)字延遲獨立編程,精準調(diào)整時鐘相位,解決高速系統(tǒng)中的時序?qū)R難題。

高可靠性設(shè)計:集成信號丟失(LOS)檢測與無瞬斷參考時鐘切換功能,在主時鐘失效時自動切換至備用源,確保系統(tǒng)連續(xù)運行;4路GPIO報警接口實時反饋設(shè)備狀態(tài),提升系統(tǒng)健康管理能力。

三、多場景適配:定義下一代時鐘分配解決方案

CLF7044憑借卓越的性能與靈活性,成為復雜時鐘樹設(shè)計的理想選擇:

5G/6G基站:支持多載波GSM、LTE、W-CDMA等蜂窩協(xié)議,為基帶處理單元提供低抖動時鐘,優(yōu)化信號調(diào)制精度;

波束成形:14路低噪聲輸出可同步驅(qū)動多通道TR組件,25ps級延遲控制滿足陣列天線的相位一致性要求;

高速數(shù)據(jù)轉(zhuǎn)換:兼容JESD204B接口,為ADC/DAC提供潔凈的參考時鐘與SYSREF同步信號,提升高速采樣系統(tǒng)的信噪比(SNR);

工業(yè)與儀器儀表:支持-40℃~85℃寬溫工作范圍及優(yōu)秀的電源抑制比(PSRR),適應(yīng)嚴苛環(huán)境下的高精度測量需求。

四、技術(shù)亮點:細節(jié)處見真章

功耗與性能平衡:通過SPI可編程相位噪聲與功耗模式,用戶可根據(jù)場景動態(tài)調(diào)整,在低功耗模式下電流消耗低至1mA(斷電模式),兼顧能效與性能;

外部VCO支持:兼容最高3200MHz外部VCO輸入,靈活擴展系統(tǒng)頻率范圍,適配定制化高頻時鐘需求;

保持模式(Holdover):在參考時鐘丟失時維持輸出頻率穩(wěn)定,頻率精度達0.5ppm,保障通信系統(tǒng)在短暫信號中斷時的連續(xù)性。

五、核芯互聯(lián):持續(xù)賦能國產(chǎn)替代

作為本土高性能時鐘芯片的創(chuàng)新者,核芯互聯(lián)始終聚焦高端集成電路設(shè)計,致力于為客戶提供“高性能、高兼容、高可靠”的國產(chǎn)化解決方案。CLF7044的推出,通過用純國產(chǎn)化CMOS工藝對HMC7044進行全兼容設(shè)計,為產(chǎn)業(yè)鏈上下游提供了無風險的替代路徑,助力關(guān)鍵器件自主可控。

即日起,CLF7044樣品及評估板已開放申請,歡迎致電核芯互聯(lián)技術(shù)支持團隊(唐路:18601296113)或訪問官網(wǎng)(www.hexinhulian.com)獲取詳細資料。核芯互聯(lián)期待與您攜手,以精準時鐘賦能下一代智能系統(tǒng)。

關(guān)于核芯互聯(lián)

核芯互聯(lián)是一家專注于信號鏈、高速接口、時鐘管理及混合信號集成電路設(shè)計的高科技企業(yè),產(chǎn)品廣泛應(yīng)用于通信基礎(chǔ)設(shè)施、工業(yè)控制、數(shù)據(jù)中心等領(lǐng)域。公司堅持自主創(chuàng)新與開放合作相結(jié)合,致力于成為全球領(lǐng)先的模擬及混合信號芯片供應(yīng)商。

-

時鐘抖動

+關(guān)注

關(guān)注

1文章

63瀏覽量

16158 -

消除器

+關(guān)注

關(guān)注

0文章

55瀏覽量

8835 -

核芯互聯(lián)

+關(guān)注

關(guān)注

0文章

30瀏覽量

2017

原文標題:核芯互聯(lián) CLF7044 高性能時鐘抖動消除器正式發(fā)布:全面兼容 HMC7044

文章出處:【微信號:gh_0dbe96735e9d,微信公眾號:核芯互聯(lián)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

核芯互聯(lián)推出高性能任意時鐘發(fā)生器CLG5908M

核芯互聯(lián)CLF04828超低噪聲時鐘抖動消除器介紹

安芯半導體推出新一代低成本高性能防復制加密芯片RJGT28E16

芯原推出新一代高性能Vitality架構(gòu)GPU IP系列

芯華章推出新一代高性能FPGA原型驗證系統(tǒng)

國產(chǎn)EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統(tǒng)

CDCM7005高性能時鐘同步器和抖動消除器數(shù)據(jù)表

CDC7005高性能時鐘頻率合成器和抖動消除器數(shù)據(jù)表

CDCE72010十路輸出高性能時鐘同步器、抖動消除器和時鐘分配器數(shù)據(jù)表

核芯互聯(lián)推出新一代高性能時鐘抖動消除器CLF7044

核芯互聯(lián)推出新一代高性能時鐘抖動消除器CLF7044

評論