概述

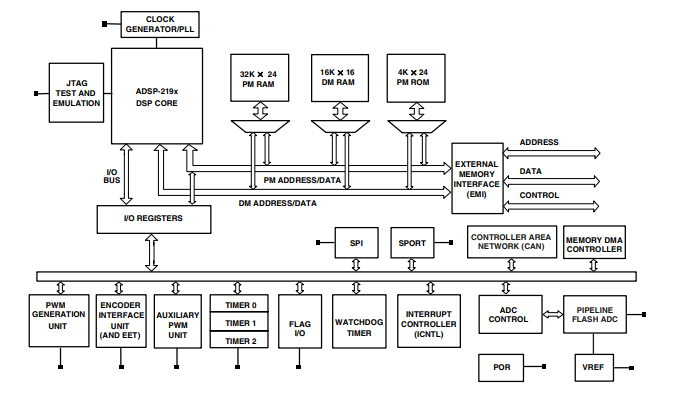

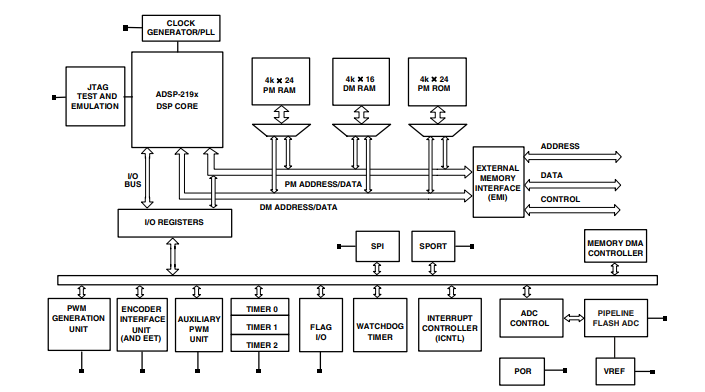

ADSP-21992進一步擴展了ADSP-2199x混合信號DSP產品系列的性能,可提供32K字程序存儲器RAM和16K字數據存儲器RAM。此外,ADSP-21992還可提供片上CAN通信端口,支持全CAN 2.0B,內置可配置郵箱和單個驗收濾波器。集成CAN接口可實現將嵌入式控制和信號處理以及現場總線通信接口整合在一起的單芯片方案。

數據表:*附件:ADSP-21992高性能混合型信號DSP,160MHz,32K字程序存儲器RAM,16K字數據存儲器RAM技術手冊.pdf

特性

- 160 MHz,ADSP-219x DSP內核

- 8通道、14位、20 MSPS ADC,內置片上電壓基準

- 集成控制器區域網絡(CAN)接口

- 外部存儲器接口(達1 M字)

- 帶雙輔助PWM輸出的三相PWM發生單元

- 32K字程序存儲器RAM,16K字數據存儲器RAM

- 三相PWM發生單元

- 增量編碼器接口單元

- 3個32位通用定時器

- 16位通用標識I/O端口

- 同步串行(SPORT)和SPI通信端口

- CROSSCORE?工具支持

框圖

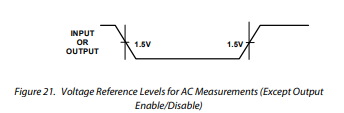

測試條件

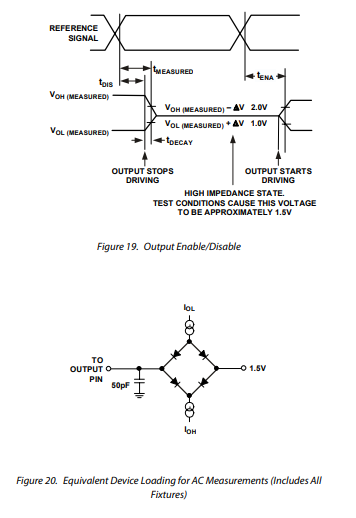

對數字信號處理器(DSP)的輸出使能、禁用和保持時間進行測試。

輸出禁用時間

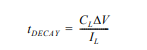

當輸出引腳停止驅動并進入高阻抗狀態時,視為輸出引腳被禁用。從輸出引腳停止驅動到總線上電壓開始下降的時間,以及電壓從測量輸出下降(Delta V)所需的時間,取決于電容負載(C_{L})和負載電流(I_{L}) 。下降時間可通過以下公式近似計算:

輸出禁用時間(t_{DISO})是(t_{MEASURED})和(t_{DECAY})之間的差值,如圖19所示。時間(t_{MEASURED})是參考信號切換到輸出電壓從測量輸出高電平或輸出低電平下降(Delta V)時的時間間隔。(t_{DECAY})是在測試負載(C_{L})和(I_{L}) 下,(Delta V)等于0.5V時計算得出的。

輸出使能時間

當輸出引腳從高阻抗狀態轉變為開始驅動時,視為輸出引腳被使能。輸出使能時間(t_{ENA})是從參考信號達到高電平或低電平,到輸出達到指定的高電平或低跳變點的時間間隔,如圖19(輸出使能/禁用圖)所示。如果多個引腳(如數據總線)被使能,測量值為第一個開始驅動的引腳的值。

示例系統保持時間計算

要確定特定系統中的數據輸出保持時間,首先使用第51頁“輸出禁用時間”中的公式計算(t_{DECAY}) 。選擇(Delta V)為ADSP - 21992輸出電壓與設備所需保持時間的輸入閾值之間的差值。典型的(Delta V)為0.4V。(C_{L})是總總線電容(每條數據線),(I_{L})是總泄漏或三態電流(每條數據線)。保持時間將是(t_{DECAY})加上最小禁用時間(即寫周期的(t_{DATWRH}) )。

-

dsp

+關注

關注

556文章

8158瀏覽量

357651 -

混合信號

+關注

關注

0文章

508瀏覽量

65370 -

RAM

+關注

關注

8文章

1392瀏覽量

117557

發布評論請先 登錄

幾種DSP與外接存儲器的連接方法

dsp與外擴展存儲器的連接方法

ADSP-21991 高性能混合型信號DSP,160 MHz,32K字程序存儲器RAM

ADSP-21992 高性能混合型信號DSP,160 MHz,32K字程序存儲器RAM,16K字數據存儲器RAM

ADSP-21992高性能混合型信號DSP,160MHz,32K字程序存儲器RAM,16K字數據存儲器RAM技術手冊

ADSP-21992高性能混合型信號DSP,160MHz,32K字程序存儲器RAM,16K字數據存儲器RAM技術手冊

評論