概述

DS28S60 DeepCover ^?^ 加密協(xié)處理器可輕松集成到嵌入式系統(tǒng)中,從而實(shí)現(xiàn)信息的機(jī)密性、身份驗(yàn)證和完整性。DS28S60具有固定的命令集且無需進(jìn)行器件級固件開發(fā),因此可以快速輕松地為物聯(lián)網(wǎng)設(shè)備實(shí)現(xiàn)全面的安全性。使用行業(yè)標(biāo)準(zhǔn)的SPI從機(jī)接口,以高達(dá)20Mbps的速度,通過一組簡單的命令與器件進(jìn)行通信,這些命令提供了一個(gè)利用基于硬件的加密塊的全面安全工具箱。作為SPI接口主機(jī)控制器的協(xié)處理器,命令功能包括ECDSA-P256簽名和驗(yàn)證、基于SHA-256的數(shù)字簽名、AES-128數(shù)據(jù)包加密/解密、用于會話密鑰生成的ECDHE密鑰交換以及訪問高質(zhì)量的隨機(jī)數(shù)。集成了符合NIST SP800-90B標(biāo)準(zhǔn)的真隨機(jī)數(shù)生成器(TRNG)用于片內(nèi)加密操作,并在需要時(shí)向主機(jī)控制器提供隨機(jī)數(shù)據(jù)和隨機(jī)數(shù)。通過3.6KB安全閃存支持密鑰、證書、公鑰/私鑰和特定于應(yīng)用程序的敏感數(shù)據(jù)的非易失性存儲。

DS28S60集成了Maxim的專利ChipDNA ^?^ 功能,這是一種物理不可克隆功能(PUF),可提供高性價(jià)比的解決方案,具有針對安全攻擊的卓效保護(hù)。ChipDNA電路利用晶圓制造過程中自然發(fā)生的半導(dǎo)體器件特性的隨機(jī)變化,產(chǎn)生隨時(shí)間、溫度和工作電壓變化可重復(fù)的唯一輸出值。如果黑客試圖探測或觀測ChipDNA的運(yùn)行情況,系統(tǒng)會觸發(fā)修改基礎(chǔ)電路的特性,防止黑客找到芯片加密函數(shù)使用的唯一值。ChipDNA輸出用作關(guān)鍵內(nèi)容,以加密方式保護(hù)所有器件存儲的數(shù)據(jù)。

數(shù)據(jù)表:*附件:DS28S60具有ChipDNA的DeepCover加密協(xié)處理器技術(shù)手冊.pdf

應(yīng)用

- 端點(diǎn)認(rèn)證

- 端到端加密

- 物聯(lián)網(wǎng)(IoT)設(shè)備安全性

- 密鑰管理和交換

- 防止偽造產(chǎn)品

特性 - 采用符合NIST標(biāo)準(zhǔn)的基于硬件的加密技術(shù)的安全協(xié)處理器

- FIPS-180 SHA-256 MAC和FIPS-198 HMAC哈希

- FIPS-197 AES-128與GCM

- FIPS-186 ECDSA-P256橢圓曲線數(shù)字簽名/驗(yàn)證

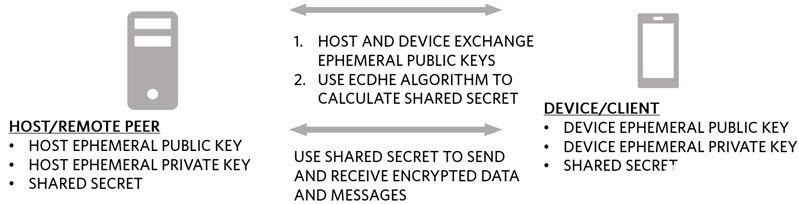

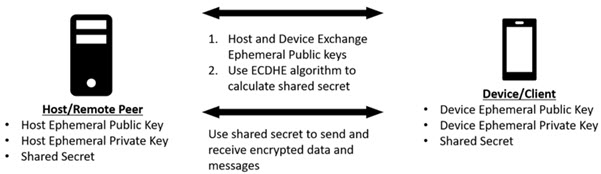

- SP800-56A ECDHE-P256密鑰交換

- 符合SP800-90B標(biāo)準(zhǔn)的TRNG

- 可靠的防范措施助力防護(hù)安全攻擊

- ChipDNA生成的密鑰以加密方式保護(hù)所有存儲的數(shù)據(jù)

- 主動監(jiān)控的芯片屏蔽可檢測入侵嘗試并做出反應(yīng)

- 通過輕松的終端應(yīng)用集成實(shí)現(xiàn)快速上市

- 固定功能命令集,無器件級固件

- 軟件開發(fā)示例的C源代碼演示

- 用于安全密鑰、證書和數(shù)據(jù)存儲的3.6KB閃存陣列

- 用于主機(jī)微控制器通信的高速接口

- 20MHz SPI,提供模式0或模式3操作

- 補(bǔ)充特性支持輕松集成到終端應(yīng)用中

- 唯一且不可更改的64位出廠編號(ROM ID)

- 低功耗工作

- 100nA(關(guān)斷模式)

- 0.35mA(空閑狀態(tài))

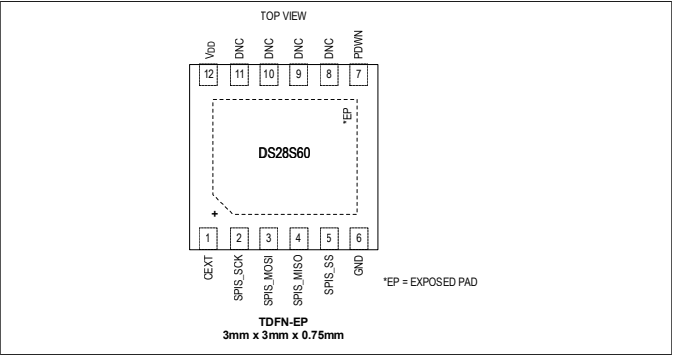

- 12引腳3mm x 3mm TDFN封裝

- -40°C至+105°C,1.62V至3.63V

特性

- 采用符合NIST標(biāo)準(zhǔn)的基于硬件的加密技術(shù)的安全協(xié)處理器

- FIPS-180 SHA-256 MAC和FIPS-198 HMAC哈希

- FIPS-197 AES-128與GCM

- FIPS-186 ECDSA-P256橢圓曲線數(shù)字簽名/驗(yàn)證

- SP800-56A ECDHE-P256密鑰交換

- 符合SP800-90B標(biāo)準(zhǔn)的TRNG

- 可靠的防范措施助力防護(hù)安全攻擊

- ChipDNA生成的密鑰以加密方式保護(hù)所有存儲的數(shù)據(jù)

- 主動監(jiān)控的芯片屏蔽可檢測入侵嘗試并做出反應(yīng)

- 通過輕松的終端應(yīng)用集成實(shí)現(xiàn)快速上市

- 固定功能命令集,無器件級固件

- 軟件開發(fā)示例的C源代碼演示

- 用于安全密鑰、證書和數(shù)據(jù)存儲的3.6KB閃存陣列

- 用于主機(jī)微控制器通信的高速接口

- 20MHz SPI,提供模式0或模式3操作

- 補(bǔ)充特性支持輕松集成到終端應(yīng)用中

- 唯一且不可更改的64位出廠編號(ROM ID)

- 低功耗工作

- 100nA(關(guān)斷模式)

- 0.35mA(空閑狀態(tài))

- 12引腳3mm x 3mm TDFN封裝

- -40°C至+105°C,1.62V至3.63V

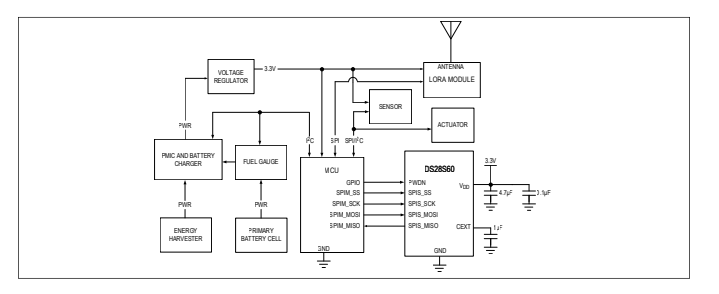

典型應(yīng)用示例:電池供電的LoRa端點(diǎn)

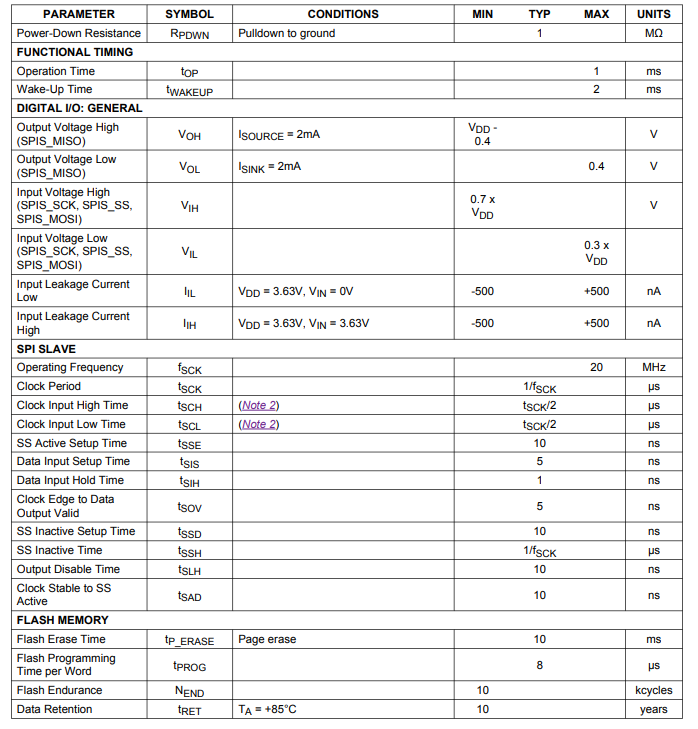

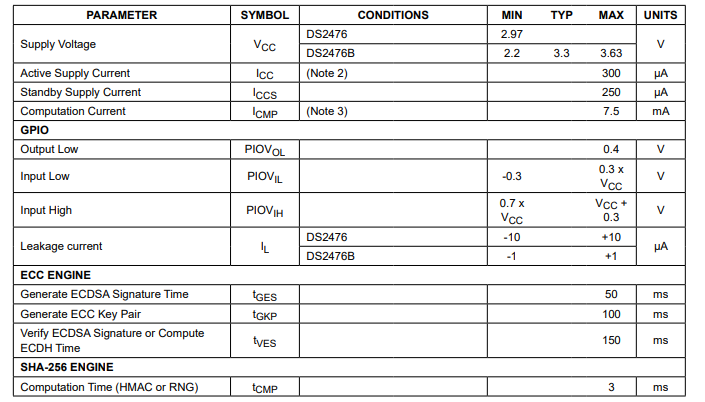

電特性

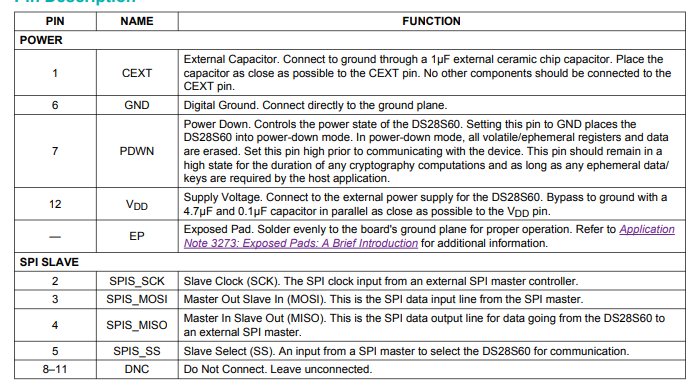

引腳配置描述

-

協(xié)處理器

+關(guān)注

關(guān)注

0文章

84瀏覽量

18542 -

加密

+關(guān)注

關(guān)注

0文章

317瀏覽量

24388 -

DeepCover

+關(guān)注

關(guān)注

0文章

59瀏覽量

12212

發(fā)布評論請先 登錄

使用DS28S60加密協(xié)處理器的基礎(chǔ)知識

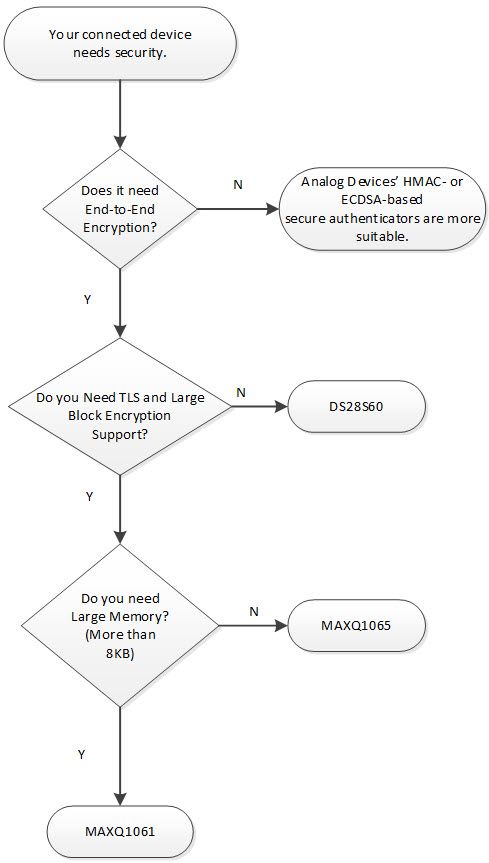

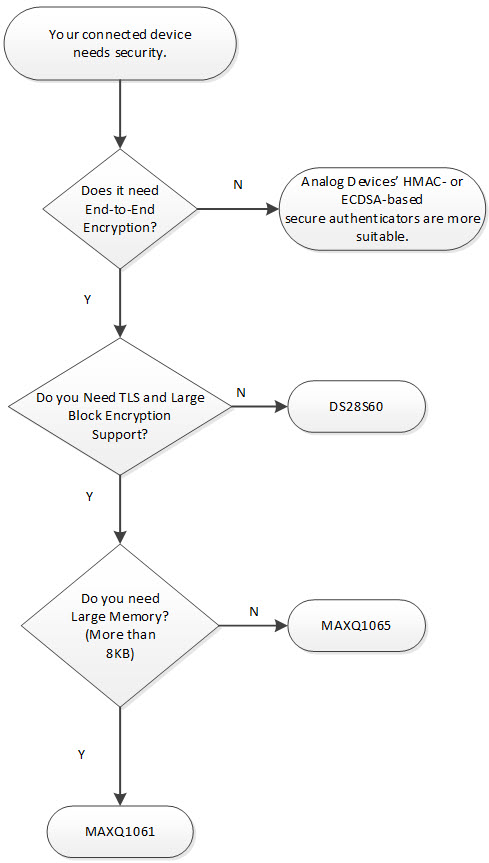

比較DS28S60、MAXQ1061和MAXQ1065功能

基于DS28S60的雙向身份驗(yàn)證示例

基于DS28S60的雙向身份驗(yàn)證示例,使用Jupyter筆記本

比較DS28S60、MAXQ1061和MAXQ1065功能

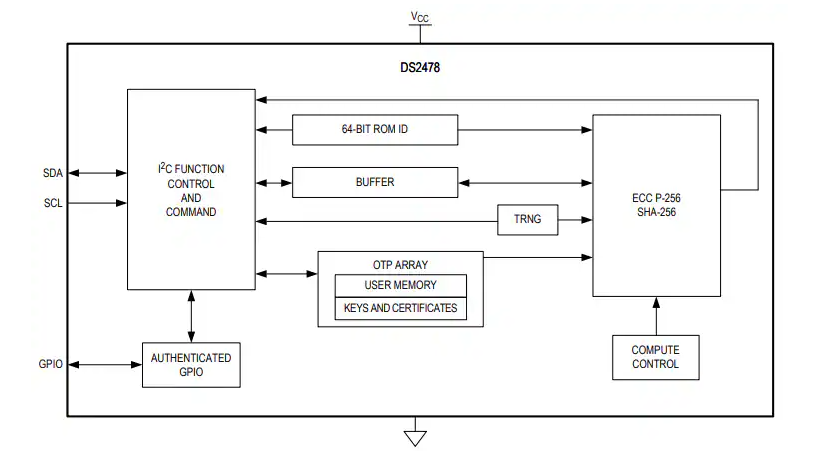

DS2478 DeepCover汽車安全協(xié)處理器技術(shù)手冊

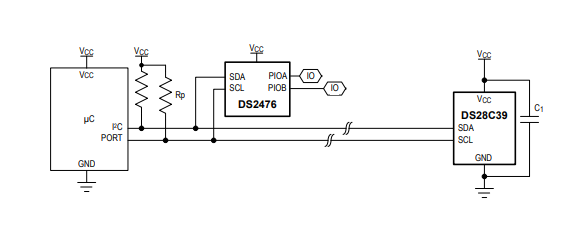

DS28C39具有ChipDNA PUF保護(hù)的DeepCover安全ECDSA雙向認(rèn)證器技術(shù)手冊

DS28C50具有ChipDNA PUF保護(hù)的DeepCover I2C安全SHA-3認(rèn)證器技術(shù)手冊

DS28E39具有ChipDNA PUF保護(hù)的DeepCover安全ECDSA雙向認(rèn)證器技術(shù)手冊

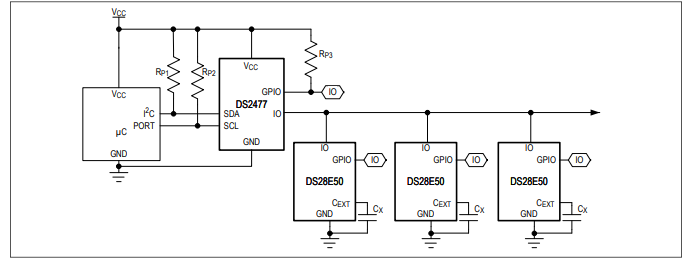

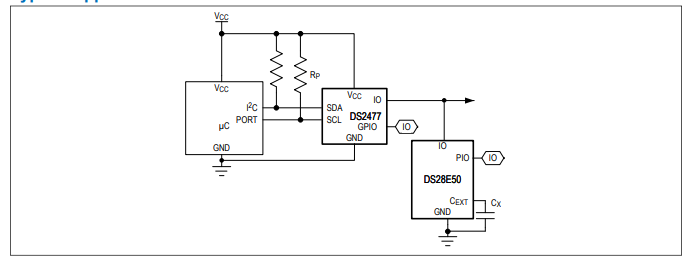

DS2477具有ChipDNA PUF保護(hù)的DeepCover安全SHA-3協(xié)處理器技術(shù)手冊

DS28E50具有ChipDNA PUF保護(hù)的DeepCover安全SHA-3認(rèn)證器技術(shù)手冊

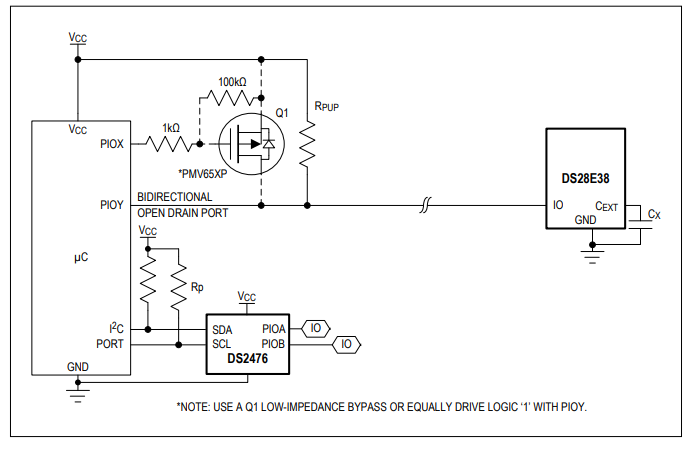

DS28E38具有ChipDNA PUF保護(hù)的DeepCover安全ECDSA認(rèn)證器技術(shù)手冊

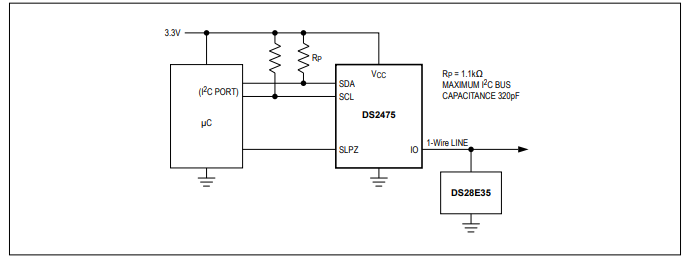

DS2475帶1-Wire主機(jī)的DeepCover ECDSA協(xié)處理器技術(shù)手冊

Analog Devices / Maxim Integrated DS2478 DeepCover?車用安全協(xié)處理器數(shù)據(jù)手冊

DS28S60具有ChipDNA的DeepCover加密協(xié)處理器技術(shù)手冊

DS28S60具有ChipDNA的DeepCover加密協(xié)處理器技術(shù)手冊

評論