概述

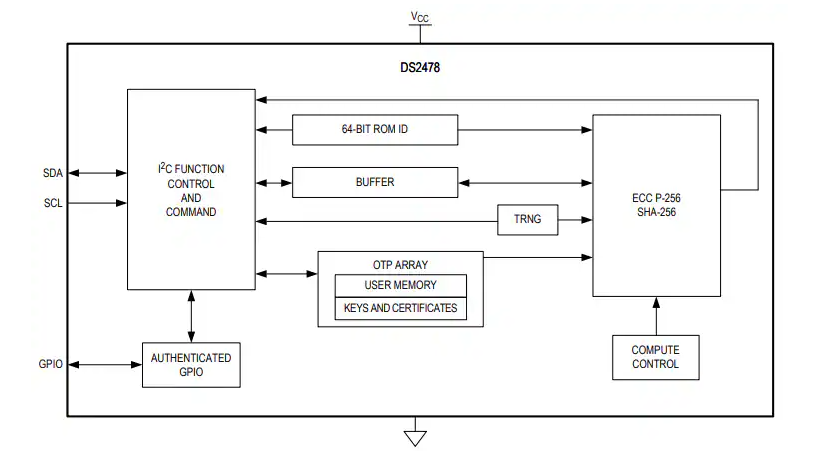

DS2476為安全ECDSA和HMAC SHA-256協處理器,與DS28C36配套。協處理器可計算在DS28C36執行任何運算所必須的HMAC或ECDSA簽名。DS2476提供一組核心的加密工具,集成非對稱(ECC-P256)和對稱(SHA-256)加密功能。除了硬件加密引擎提供的安全服務外,器件也集成FIPS/NIST真隨機數發生器(RNG)、8Kb安全EEPROM、僅遞減計數器、雙引腳可配置GPIO和唯一的64位ROM識別碼(ROM ID)。

ECC公鑰/私鑰功能采用NIST定義的P-256曲線,包括FIPS 186兼容的ECDSA簽名發生和驗證,支持雙向對稱密鑰認證模式。SHA-256密鑰功能兼容FIPS 180,可靈活地配合ECDSA使用或獨立使用,實現多種HMAC功能。

兩個GPIO引腳可通過命令控制獨立工作,包括配置,支持安全認證和非安全認證操作,包括基于ECDSA的密碼可靠模式,支持主機處理器安全引導。這種安全引導方法也可用于支持協處理器功能。

DeepCover?嵌入式安全方案采用多重先進的安全機制保護敏感數據,提供最高等級的密鑰存儲安全保護。為防止器件級安全攻擊,實施了入侵和非入侵反制措施,包括有源芯片屏蔽、密鑰存儲器加密,以及基于算法的方法。

數據表:*附件:DS2476 DeepCover安全協處理器技術手冊.pdf

應用

特性

- ECC-256計算引擎

- FIPS 186 ECDSA P256簽名和驗證

- ECDH密鑰認證交換,防止中間人攻擊

- ECDSA認證讀/寫可配置存儲器

- FIPS 180 SHA-256計算引擎

- HMAC

- ECDH SHA-256 OTP (一次性密碼本)加密讀/寫可配置存儲器(使用ECDH生成的密鑰)

- 兩個GPIO引腳,帶有可選的安全認證控制

- 漏極開路,4mA/0.4V

- 可選SHA-256或ECDSA安全認證開/關以及狀態讀取

- 可選ECDSA證書,在多塊哈希算法之后設置為開/關,實現安全引導

- RNG帶有NIST SP 800-90B兼容熵源,帶有讀出功能

- 可選芯片產生的私鑰/公鑰對,用于ECC運算

- 17位一次性可設置、非易失僅遞減計數器,帶安全認證讀操作

- 8Kb EEPROM,用于用戶數據、密鑰和證書

- 唯一且不可更改的工廠編程64位識別碼(ROM ID)

- 可選輸入數據元素,用于加密和密鑰運算

- I2C通信,100kHz和400kHz

- 工作范圍:3.3V ±10%,-40°C至+85°C

- 6引腳TDFN封裝

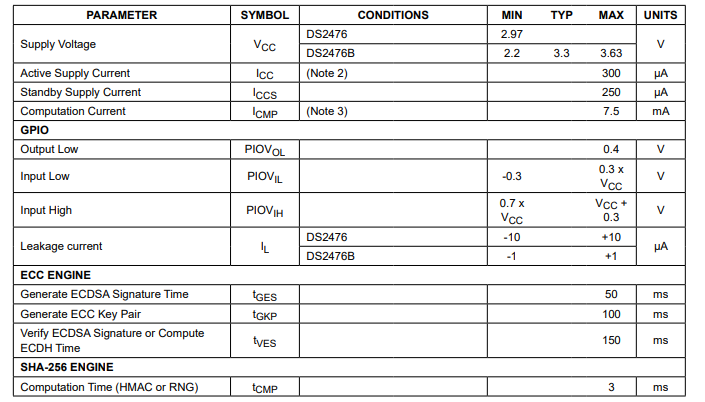

電特性

引腳配置描述

I2C

一般特性

I2C 總線由一條數據線(SDA)和一條時鐘線(SCL)組成,用于通信。SDA 和 SCL 都是雙向線路,通過上拉電阻連接到正電源電壓。當沒有通信時,兩條線均為高電平。連接到總線的輸出級設備必須具有開漏或集電極開路,以實現線與功能。I2C 總線上的數據以字節為單位傳輸,標準模式下速率高達 100kbps,快速模式下高達 400kbps。DS2476 在這兩種模式下均可工作。

在總線上發送數據的設備定義為發送器,接收數據的設備定義為接收器。控制通信的設備稱為主機。主機控制從機,當各個從機被單獨訪問時,每個從機都必須有一個不與總線上其他設備沖突的從機地址。

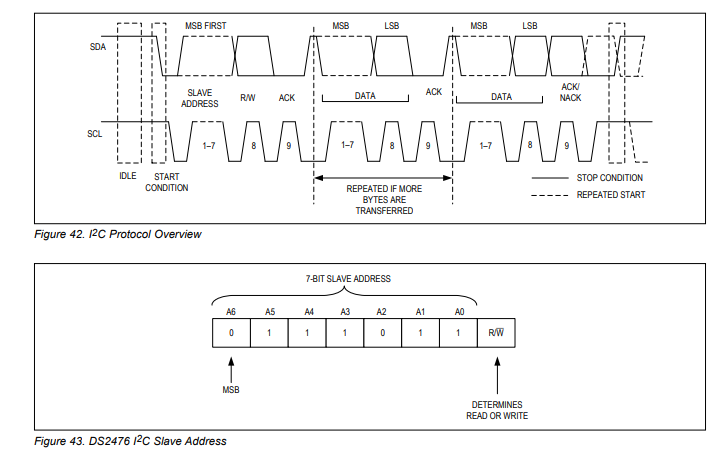

只有在總線不忙時才能啟動數據傳輸。主機生成串行時鐘(SCL),控制總線訪問,生成起始(START)和停止(STOP)條件,并確定傳輸的數據字節數。數據在起始和停止條件之間傳輸(見圖 42)。數據以字節為單位傳輸,最高有效位先發送。每個字節后面都跟隨一個來自主機的確認位,以實現主機和從機之間的同步。

從機地址

DS2476 響應的從機地址如圖 43 所示。從機地址是從機地址/控制字節的一部分。從機地址/控制字節的最后一位(R/W)定義數據方向。當設置為 0 時,后續數據從主機流向從機(寫操作);當設置為 1 時,數據從從機流向主機(讀操作)。

I2C定義

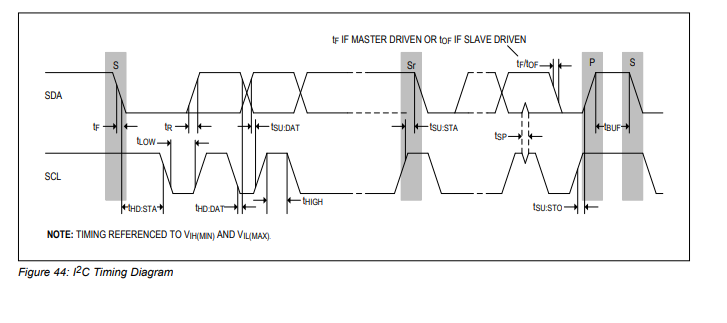

以下術語常用于描述I2C數據傳輸,其定時參考在圖44中定義。

總線空閑或非忙狀態

數據線(SDA)和時鐘線(SCL)均處于非活動狀態,且為邏輯高電平。

起始(START)條件

要與從機開始通信,主機必須生成一個起始條件。起始條件定義為:在時鐘線(SCL)保持高電平期間,數據線(SDA)從高電平變為低電平。

停止(STOP)條件

要與從機結束通信,主機必須生成一個停止條件。停止條件定義為:在時鐘線(SCL)保持高電平期間,數據線(SDA)從低電平變為高電平。

重復起始(Repeated START)條件

重復起始條件常用于在指定內存地址進行讀訪問后進行讀操作。主機可以在數據傳輸結束時生成一個重復起始條件,以便緊接著啟動新一輪數據傳輸。重復起始條件的生成方式與正常起始條件相同,但不會在停止條件后使總線進入空閑狀態。

有效數據

除了起始和停止條件外,只有在時鐘線(SCL)為低電平且穩定時,數據線(SDA)上的電平變化才有效。在整個SCL脈沖高電平期間,SDA上的數據必須保持穩定,且需滿足建立時間(tSU_DAT )和保持時間(tHD_DAT )的要求(在SCL上升沿之前),見圖44 。每個數據位對應一個時鐘脈沖。在SCL脈沖上升沿期間,數據移入接收設備。

寫操作完成時,主機必須在建立時間(最小tSU_DAT ,見圖44 )之前釋放SDA線,以便在SCL上升沿時有足夠時間開始讀操作。從機在SCL前一個脈沖的下降沿將每個數據位移出SDA線,并在SCL上升沿時將數據位的值鎖存。主機必須生成所有SCL時鐘脈沖,包括用于讀操作的那些脈沖。

-

協處理器

+關注

關注

0文章

84瀏覽量

18513 -

DeepCover

+關注

關注

0文章

59瀏覽量

12197

發布評論請先 登錄

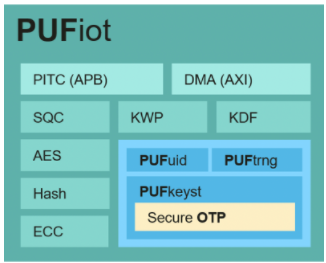

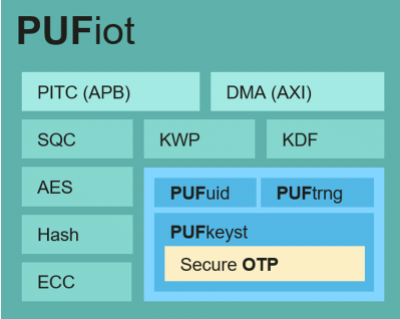

RISC-V設計的基本安全協處理器

貿澤備貨Maxim DS2477安全I2C協處理器 提供身份認證和物理安全性

帶有EEPROM的SHA1協處理器DS2460電子資料

DS2476Q+T DS2476Q+T - (Maxim Integrated) - 專用 IC

DS2476Q+U 專用 IC

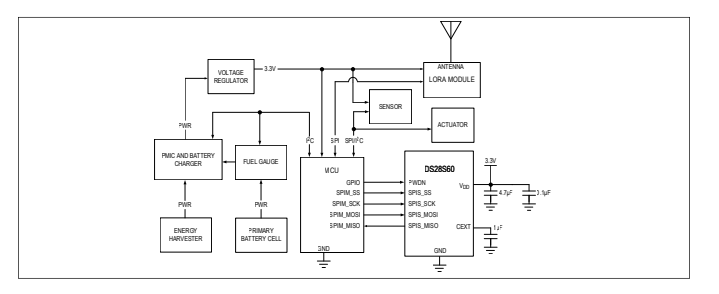

DS28S60具有ChipDNA的DeepCover加密協處理器技術手冊

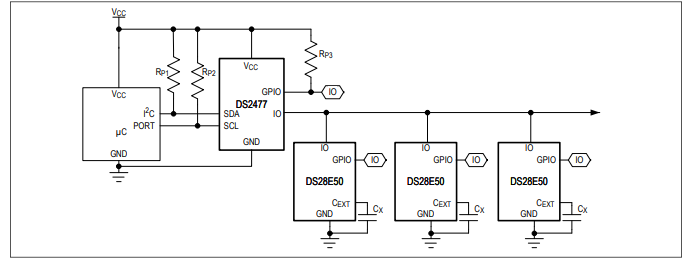

DS2477具有ChipDNA PUF保護的DeepCover安全SHA-3協處理器技術手冊

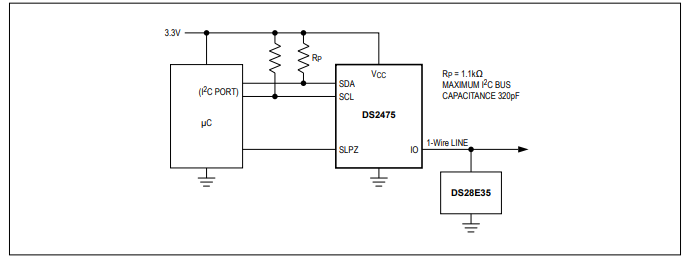

DS2475帶1-Wire主機的DeepCover ECDSA協處理器技術手冊

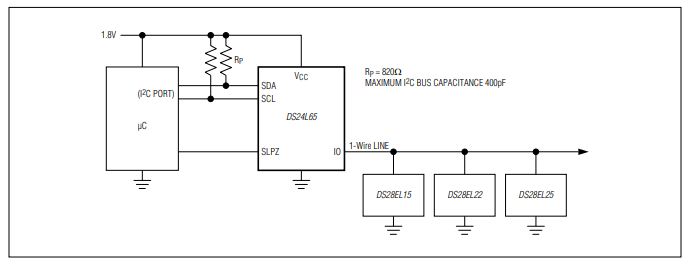

DS24L65 DeepCover安全認證器,具有SHA-256協處理器和1-Wire主機功能技術手冊

Analog Devices / Maxim Integrated DS2478 DeepCover?車用安全協處理器數據手冊

DS2476 DeepCover安全協處理器技術手冊

DS2476 DeepCover安全協處理器技術手冊

評論