相位累加器

關于相位累加器的使用,我不確定放在FPGA專題中是否合適,但是因為確實很多應用都是在FPGA上面的,所以暫時先這樣定吧。

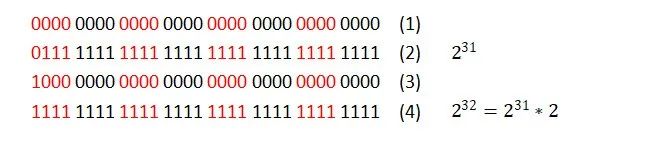

標題中所提到的DDS,我感覺這兩個放一起也可以,因為DDS的核心思想就是使用的相位累加器。那么這玩意兒的作用是啥?簡單來說就是在FPGA工作主頻之下,可以生成任意頻率的周期信號出來。

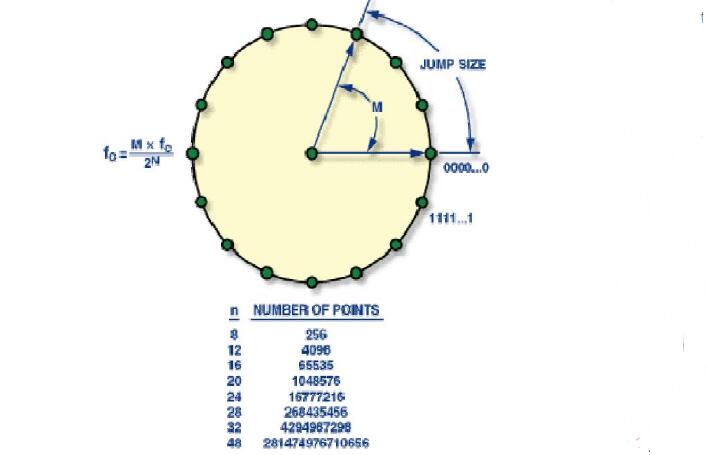

定義一個32bit的頻率字Acc

定義一個32bit的頻率控制字F_word

假設系統時鐘(準確的說法應該是相位累加器的參考時鐘)fclk

需要產生的時鐘頻率 fout

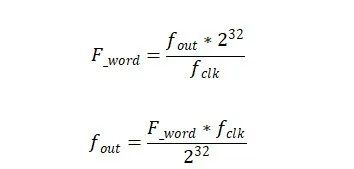

根據公式:

上面兩個公式可以在已知需要獲得的輸出頻率的基礎上,計算得到需要的頻率控制字。

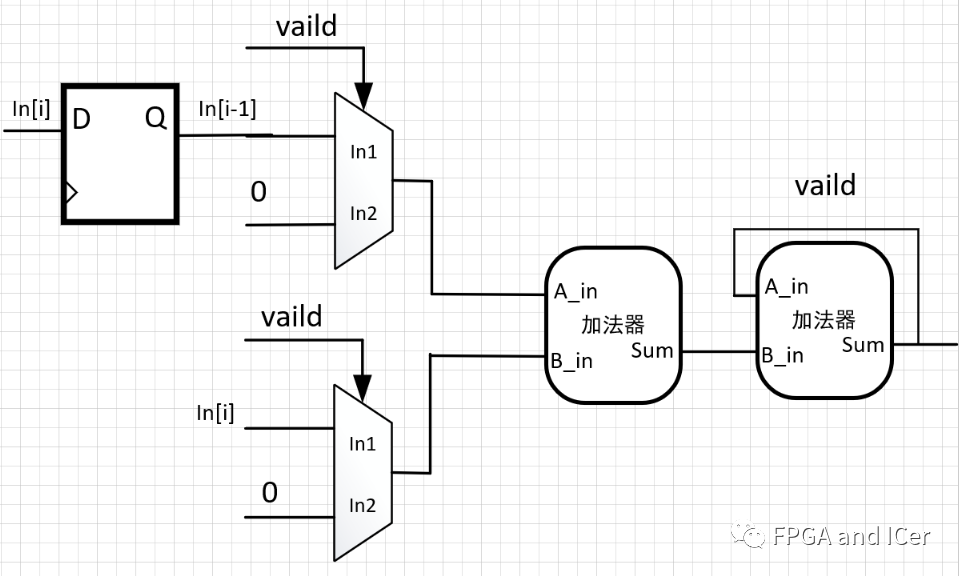

然后看下頻率控制字是怎么用的,這里就是用的相位累加器的原理。

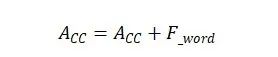

上式是一個累加的過程,實現的原理是在一個32bit的數據范圍內,即在(0~2^32-1)這個范圍內進行累加,累加的步進是F_word;完成這一個范圍內的累加之后,用時為T,那么這個T的倒數就是我們需要的fout了。完成一次累加之后,頻率字Acc會溢出,然后進入下一次累加,形成下一個周期信號;如此重復進行后就是一個振蕩的周期信號了。

那么這個周期信號該怎么表示出來呢?上面說了,完成(0~2^32-1)的累加過程是一個周期T,那么在這個周期里面,應該會有一次信號翻轉。即高電平時間T/2,低電平時間也是T/2。

對于一個32bit的數,當低31位不斷累加,直到第32bit從0跳轉到1的時間段內,就是用了T/2的時間;當第32bit變成1之后,低31位又開始累加,直到數據溢出,又是T/2的時間。

如果不能理解,結合下圖

也就是說,在整個累加過程中,我們只要判斷Acc的最高的情況,在0~T/2時間內,最高位為0;

在T/2~T的時間內,最高位為1;這樣就是會產生一個fout的方波信號了。

assign clk_out=Acc(31);

這樣的clk_out就是需要的fout了。

亦或者,直接對Acc的值進行判斷

always@(posedgeclkornegedgerst)if(!rst) clk_out <=?1'b0;elseif(Acc <=?32'h7fffffff) clk_out <=?1'b0;elseif(Acc >32'h7fffffff) clk_out <=?1'b1;

同樣可以輸出fout。

采樣率

同時,想說一下關于采樣率的問題。

常見于ADC這類芯片中,例如,某ADC芯片的采樣率為1MHz,意思是每秒可以采樣1M個點,那么采一個點所要花的時間是(1/1M) 秒。

在做FFT的時候,通常需要采集一個完整的正弦波,來進行FFT,這里就會涉及采樣率的問題。

假如一個正弦波的頻率為fsig=50KHz,我們需要用128個點來進行FFT,那就是要128個點采集完成這個正弦波。根據正弦波的頻率可以計算出正弦波的周期Tsig=1/fsig;那么這128個點所占的時間就應該是這個周期Tsig。也就是說,采樣芯片需要在Tsig時間內采集完成128個點,那么這個就可以計算出需要的采樣率了。采樣率設為Fs,則采一個點的時間是1/Fs;采128個點的時間就是128/Fs;則

128/Fs=1/fsig;會得出采樣率Fs=128fsig;得到的是和被采樣信號頻率的關系;

根據奈奎斯特定律,采樣頻率至少要是被采樣信號頻率的2倍,才能獲得被采樣信號的有效信息,否則就會出現失真。這里其實就可以分析得到,這里的128個點其實是可以人為設定的,假如設置為N;那么最后的公式就是Fs=Nfsig 。當然,保證這里的N>2是非常有必要的。

一般來說,我們的N會取的比較大。

FFT

說到上面的信息,不得不再說下FFT

其中的參數就包括上面說的Fs、N、fsig

FFT是一種計算,采樣到一個點,進行一系列的運算后,輸出一個復數,假設為A+Bi;這個復數中就包含這個被采樣信號sig的信息,對A和B求平方和再開根號,就是當前采樣點在頻譜上的幅值(注意并不是在正弦波形上的幅值),頻譜上幅值最大的點出現在fsig頻率處。

對于一個未知頻率的正弦波信號,對其進行采樣,然后進行頻譜幅值的最大值篩選,可以計算出這個信號的頻率。

Fs/N的意思是,對所有的N個采樣點,用Fs的采樣率來采樣,則在每個點處的頻率值(這個是在頻域上的信息)。假設fsig出現在從0~N之間的某個點n處,則會有Fs/N*(n-1)=fsig;同樣是可以計算出這個n。

-

FPGA

+關注

關注

1645文章

22040瀏覽量

618222 -

時鐘

+關注

關注

11文章

1898瀏覽量

133199 -

相位累加器

+關注

關注

0文章

11瀏覽量

9276

原文標題:相位累加器

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于相位累加器的任意分頻原理解析

累加器verilog語言編程問題

FPGA實現NCO中相位累加器的輸出和查找表地址什么關系?

請問AD9910并行端口控制相位時,并行數據是輸入到相位累加器中還是輸入到相位偏移字中?

dds相位累加器沒有提高采樣頻率

計算機累加器有加法器功能嗎,累加器是什么_累加器的作用及原理介紹 精選資料推薦

累加器A的主要作用是什么_一文解析累加器a和acc的區別

32位數字相位累加器的程序和工程文件免費下載

相位累加器的實現原理

相位累加器的實現原理

評論